## Withdrawn Draft

### Warning Notice

The attached draft document has been withdrawn, and is provided solely for historical purposes. It has been superseded by the document identified below.

Withdrawal Date October 27, 2021

**Original Release Date** May 20, 2021

### **Superseding Document**

| Status           | 2 <sup>nd</sup> Public Draft (2PD)                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Series/Number    | NIST Interagency or Internal Report 8320                                                                              |

| Title            | Hardware-Enabled Security: Enabling a Layered Approach to<br>Platform Security for Cloud and Edge Computing Use Cases |

| Publication Date | October 2021                                                                                                          |

| DOI              | https://doi.org/10.6028/NIST.IR.8320-draft2                                                                           |

| CSRC URL         | https://csrc.nist.gov/publications/detail/nistir/8320/draft                                                           |

|                  |                                                                                                                       |

**Additional Information**

| Draft NISTIR 8320                                        | 1  |

|----------------------------------------------------------|----|

| <b>Hardware-Enabled Security:</b>                        | 2  |

| abling a Layered Approach to Platform Security for Cloud | 3  |

| and Edge Computing Use Cases                             | 4  |

|                                                          | 5  |

| Michael Bartock                                          | 6  |

| Murugiah Souppaya                                        | 7  |

| Ryan Savino                                              | 8  |

| Tim Knoll                                                | 9  |

| Uttam Shetty                                             | 10 |

| Mourad Cherfaoui                                         | 11 |

| Raghu Yeluri                                             | 12 |

| Akash Malhotra                                           | 13 |

| Karen Scarfone                                           | 14 |

|                                                          | 15 |

|                                                          | 16 |

|                                                          | 17 |

| This publication is available free of charge from:       | 18 |

| https://doi.org/10.6028/NIST.IR.8320-draft               | 19 |

|                                                          | 20 |

|                                                          | 21 |

|                                                          | 22 |

|                                                          |    |

| Draft NISTIR 832                                                                                   | 20            |

|----------------------------------------------------------------------------------------------------|---------------|

| Hardware-Enabled Security                                                                          | V:            |

|                                                                                                    | <b>J</b> •    |

| Enabling a Layered Approach to Platform Security for Close                                         | oud           |

| and Edge Computing Use Cas                                                                         | ses           |

| Michael Bart                                                                                       | tock          |

| Murugiah Soupp                                                                                     | paya          |

| Computer Security Divis                                                                            |               |

| Information Technology Labora                                                                      | itory         |

|                                                                                                    |               |

| Ryan Sav                                                                                           |               |

| Tim K                                                                                              |               |

| Uttam Sh                                                                                           | •             |

| Mourad Cherfa                                                                                      |               |

| Raghu Ye                                                                                           |               |

| Intel Data Platforms Gr                                                                            |               |

| Santa Clara,                                                                                       | , <i>CA</i>   |

|                                                                                                    |               |

| Akash Malh                                                                                         |               |

| AMD Product Security and Strategy Gr                                                               | -             |

| Austin,                                                                                            | l, IX         |

| Kanan Card                                                                                         | c.            |

| Karen Scarf                                                                                        |               |

| Scarfone Cybersecu                                                                                 | -             |

| Clifton,                                                                                           | , <i>V</i> A  |

|                                                                                                    |               |

|                                                                                                    |               |

| May 2                                                                                              | 2021          |

|                                                                                                    |               |

| SUPPTINENT OF COMPA                                                                                | MINCE * POINT |

| U.S. Department of Comm                                                                            | nerce         |

| Gina Raimondo, Secre                                                                               |               |

| Gina Kalilohao, Seere                                                                              | y             |

| National Institute of Standards and Technol                                                        | ology         |

| James K. Olthoff. Performing the Non-Freducive Functions and Duties of the Under Secretary of Comm |               |

James K. Olthoff, Performing the Non-Exclusive Functions and Duties of the Under Secretary of Commerce for Standards and Technology & Director, National Institute of Standards and Technology

58 59

| 60 | National Institute of Standards and Technology Interagency or Internal Report 8320                           |

|----|--------------------------------------------------------------------------------------------------------------|

| 61 | 58 pages (May 2021)                                                                                          |

| 62 | This publication is available free of charge from:                                                           |

| 63 | https://doi.org/10.6028/NIST.IR.8320-draft                                                                   |

| 64 | Certain commercial entities, equipment, or materials may be identified in this document in order to describe |

64 Certain commercial entities, equipment, or materials may be identified in this document in order to describe an 65 experimental procedure or concept adequately. Such identification is not intended to imply recommendation or 66 endorsement by NIST, nor is it intended to imply that the entities, materials, or equipment are necessarily the best 67 available for the purpose.

There may be references in this publication to other publications currently under development by NIST in accordance with its assigned statutory responsibilities. The information in this publication, including concepts and methodologies, may be used by federal agencies even before the completion of such companion publications. Thus, until each publication is completed, current requirements, guidelines, and procedures, where they exist, remain operative. For planning and transition purposes, federal agencies may wish to closely follow the development of these new publications by NIST.

# Organizations are encouraged to review all draft publications during public comment periods and provide feedback to NIST. Many NIST cybersecurity publications, other than the ones noted above, are available at <a href="https://csrc.nist.gov/publications">https://csrc.nist.gov/publications</a>.

| 77                   | Public comment period: May 27, 2021 through June 30, 2021                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78<br>79<br>80<br>81 | National Institute of Standards and Technology<br>Attn: Applied Cybersecurity Division, Information Technology Laboratory<br>100 Bureau Drive (Mail Stop 2000) Gaithersburg, MD 20899-2000<br>Email: <u>hwsec@nist.gov</u> |

| 82                   | All comments are subject to release under the Freedom of Information Act (FOIA).                                                                                                                                           |

| 83                   |                                                                                                                                                                                                                            |

### **Reports on Computer Systems Technology**

85 The Information Technology Laboratory (ITL) at the National Institute of Standards and

86 Technology (NIST) promotes the U.S. economy and public welfare by providing technical

87 leadership for the Nation's measurement and standards infrastructure. ITL develops tests, test

88 methods, reference data, proof of concept implementations, and technical analyses to advance

- the development and productive use of information technology. ITL's responsibilities include the development of management, administrative, technical, and physical standards and guidelines for

- 91 the cost-effective security and privacy of other than national security-related information in

- 91 the cost-effective security and privacy of other than national security-related information is 92 federal information systems

- 92 federal information systems.

### 93

### Abstract

94 In today's cloud data centers and edge computing, attack surfaces have significantly increased,

95 hacking has become industrialized, and most security control implementations are not coherent

96 or consistent. The foundation of any data center or edge computing security strategy should be

97 securing the platform on which data and workloads will be executed and accessed. The physical

98 platform represents the first layer for any layered security approach and provides the initial

99 protections to help ensure that higher-layer security controls can be trusted. This report explains

100 hardware-enabled security techniques and technologies that can improve platform security and

101 data protection for cloud data centers and edge computing.

### 102

### Keywords

103 confidential computing; container; hardware-enabled security; hardware security module

104 *(HSM); secure enclave; trusted execution environment (TEE); trusted platform module (TPM);* 105 *virtualization.*

100 /0

### Disclaimer

107 Any mention of commercial products or reference to commercial organizations is for information

108 only; it does not imply recommendation or endorsement by NIST, nor does it imply that the 109 products mentioned are necessarily the best available for the purpose.

110

106

| 111                             | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 112<br>113                      | The authors thank everyone who contributed their time and expertise to the development of this report, including:                                                                                                                                                                                                                                                                                                             |

| 114<br>115<br>116<br>117        | • From Intel Corporation: Ravi Sahita, Alex Eydelberg, Sugumar Govindarajan, Kapil<br>Sood, Jeanne Guillory, David Song, Scott Raynor, Scott Huang, Matthew Areno, Charlie<br>Stark, Subomi Laditan, Kamal Natesan, Haidong Xia, Jerry Wheeler, Dhinesh<br>Manoharan, and John Pennington                                                                                                                                     |

| 118                             | From AMD: David Kaplan and Kathir Nadarajah                                                                                                                                                                                                                                                                                                                                                                                   |

| 119                             | Audience                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 120<br>121<br>122<br>123<br>124 | The primary audiences for this report are security professionals, such as security engineers and architects; system administrators and other information technology (IT) professionals for cloud service providers; and hardware, firmware, and software developers who may be able to leverage hardware-enabled security techniques and technologies to improve platform security for cloud data centers and edge computing. |

| 125                             | Trademark Information                                                                                                                                                                                                                                                                                                                                                                                                         |

| 126                             | All registered trademarks or trademarks belong to their respective organizations.                                                                                                                                                                                                                                                                                                                                             |

| 127                             |                                                                                                                                                                                                                                                                                                                                                                                                                               |

### **Call for Patent Claims**

129 This public review includes a call for information on essential patent claims (claims whose use 130 would be required for compliance with the guidance or requirements in this Information 131 Technology Laboratory (ITL) draft publication). Such guidance and/or requirements may be 132 directly stated in this ITL Publication or by reference to another publication. This call also 133 includes disclosure, where known, of the existence of pending U.S. or foreign patent applications 134 relating to this ITL draft publication and of any relevant unexpired U.S. or foreign patents. 135 136 ITL may require from the patent holder, or a party authorized to make assurances on its behalf, 137 in written or electronic form, either: 138 139 a) assurance in the form of a general disclaimer to the effect that such party does not hold 140 and does not currently intend holding any essential patent claim(s); or 141 142 b) assurance that a license to such essential patent claim(s) will be made available to 143 applicants desiring to utilize the license for the purpose of complying with the guidance 144 or requirements in this ITL draft publication either: 145 146 i. under reasonable terms and conditions that are demonstrably free of any unfair 147 discrimination: or 148 ii. without compensation and under reasonable terms and conditions that are 149 demonstrably free of any unfair discrimination. 150 151 Such assurance shall indicate that the patent holder (or third party authorized to make assurances 152 on its behalf) will include in any documents transferring ownership of patents subject to the 153 assurance, provisions sufficient to ensure that the commitments in the assurance are binding on 154 the transferee, and that the transferee will similarly include appropriate provisions in the event of 155 future transfers with the goal of binding each successor-in-interest. 156 157 The assurance shall also indicate that it is intended to be binding on successors-in-interest 158 regardless of whether such provisions are included in the relevant transfer documents. 159 160 Such statements should be addressed to: hwsec@nist.gov 161

| 162        |    |            | Table of Contents                                                                   |    |

|------------|----|------------|-------------------------------------------------------------------------------------|----|

| 163        | 1  | Intro      | oduction                                                                            | 1  |

| 164        | 2  | Harc       | dware Platform Security Overview                                                    | 3  |

| 165        | 3  | Plat       | form Integrity Verification                                                         | 5  |

| 166        |    | 3.1        | Hardware Security Module (HSM)                                                      | 5  |

| 167        |    | 3.2        | The Chain of Trust (CoT)                                                            | 6  |

| 168        |    | 3.3        | Supply Chain Protection                                                             | 7  |

| 169        | 4  | Soft       | ware Runtime Protection Mechanisms                                                  | 8  |

| 170<br>171 |    | 4.1<br>(CO | Return Oriented Programming (ROP) and Call/Jump Oriented Programmer (P/JOP) Attacks | •  |

| 172        |    | 4.2        | Address Translation Attacks                                                         | 8  |

| 173        | 5  | Data       | Protection and Confidential Computing                                               | 10 |

| 174        |    | 5.1        | Memory Isolation                                                                    | 10 |

| 175        |    | 5.2        | Application Isolation                                                               | 11 |

| 176        |    | 5.3        | VM Isolation                                                                        | 11 |

| 177        |    | 5.4        | Cryptographic Acceleration                                                          | 11 |

| 178        | 6  | Rem        | ote Attestation Services                                                            | 13 |

| 179        |    | 6.1        | Platform Attestation                                                                | 13 |

| 180        |    | 6.2        | TEE Attestation                                                                     | 15 |

| 181        | 7  | Clou       | Id Use Case Scenarios Leveraging Hardware-Enabled Security                          | 17 |

| 182        |    | 7.1        | Visibility to Security Infrastructure                                               | 17 |

| 183        |    | 7.2        | Workload Placement on Trusted Platforms                                             | 17 |

| 184        |    | 7.3        | Asset Tagging and Trusted Location                                                  | 19 |

| 185        |    | 7.4        | Workload Confidentiality                                                            | 20 |

| 186        |    | 7.5        | Protecting Keys and Secrets                                                         | 22 |

| 187        | 8  | Next       | t Steps                                                                             | 24 |

| 188        | Re | ferenc     | ces                                                                                 | 25 |

| 189        |    |            |                                                                                     |    |

| 190        |    |            | List of Appendices                                                                  |    |

| 191        | Ар | -          | x A— Vendor-Agnostic Technology Examples                                            |    |

| 192        |    | A.1        | Platform Integrity Verification                                                     |    |

| 193        |    |            | A.1.1 UEFI Secure Boot (SB)                                                         |    |

| 194        | Ар | pendi      | x B— Intel Technology Examples                                                      | 31 |

| 195        | B.1       | Platform Integrity Verification                                                                 | 31 |

|------------|-----------|-------------------------------------------------------------------------------------------------|----|

| 196        |           | B.1.1 The Chain of Trust (CoT)                                                                  | 31 |

| 197        |           | B.1.2 Supply Chain Protection                                                                   | 35 |

| 198        | B.2       | Software Runtime Protection Mechanisms                                                          | 36 |

| 199<br>200 |           | B.2.1 Return Oriented Programming (ROP) and Call/Jump Oriented Programming (COP/JOP) Attacks    | 36 |

| 201        |           | B.2.2 Address Translation Attacks                                                               | 36 |

| 202        | B.3       | Data Protection and Confidential Computing                                                      | 38 |

| 203        |           | B.3.1 Memory Isolation                                                                          | 38 |

| 204        |           | B.3.2 Application Isolation                                                                     | 39 |

| 205        |           | B.3.3 VM Isolation                                                                              | 40 |

| 206        |           | B.3.4 Cryptographic Acceleration                                                                | 40 |

| 207        |           | B.3.5 Technology Example Summary                                                                | 41 |

| 208        | B.4       | Remote Attestation Services                                                                     | 42 |

| 209        |           | B.4.1 Intel Security Libraries for the Data Center (ISecL-DC)                                   | 42 |

| 210        |           | B.4.2 Technology Summary                                                                        | 42 |

| 211        | Appendix  | x C— AMD Technology Examples                                                                    | 43 |

| 212        | C.1       | Platform Integrity Verification                                                                 | 43 |

| 213        |           | C.1.1 AMD Platform Secure Boot (AMD PSB)                                                        | 43 |

| 214        | C.2       | Data Protection and Confidential Computing                                                      | 43 |

| 215<br>216 |           | C.2.1 Memory Isolation: AMD Secure Memory Encryption (SME)/Transparent Memory Encryption (TSME) | 43 |

| 217        |           | C.2.2 VM Isolation: AMD Secure Encrypted Virtualization (SEV)                                   | 44 |

| 218        | Appendiz  | x D— Acronyms and Abbreviations                                                                 | 45 |

| 219        | Appendi   | x E— Glossary                                                                                   | 49 |

| 220        |           |                                                                                                 |    |

| 221        |           | List of Figures                                                                                 |    |

| 222        | Figure 1: | Notional Example of Remote Attestation Service                                                  | 14 |

| 223        | Figure 2: | Notional Example of TEE Attestation Flow                                                        | 16 |

| 224        | Figure 3: | Notional Example of Orchestrator Platform Labeling                                              | 18 |

| 225        | Figure 4: | Notional Example of Orchestrator Scheduling                                                     | 19 |

| 226        | Figure 5: | Notional Example of Key Brokerage                                                               | 20 |

| 227        | Figure 6: | Notional Example of Workload Image Encryption                                                   | 21 |

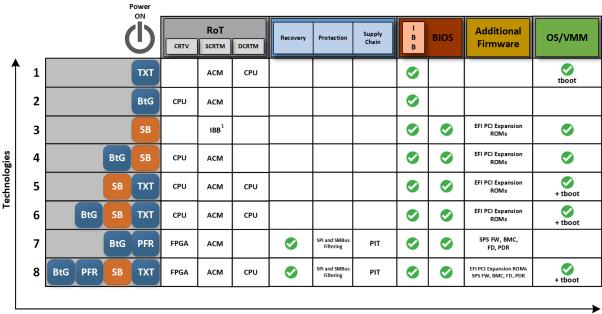

- Figure 8: Firmware and Software Coverage of Existing Chain of Trust Technologies .. 34

- 230

- 231

### 232 **1** Introduction

233 In today's cloud data centers and edge computing, there are three main forces that impact

security: (1) the introduction of billions of connected devices and increased adoption of the cloud

have significantly increased attack surfaces; (2) hacking has become industrialized with

sophisticated and evolving techniques to compromise data; and (3) solutions composed of

237 multiple technologies from different vendors result in a lack of coherent and consistent

implementations of security controls. Given these forces, the foundation for a data center or edge

computing security strategy should have a consolidated approach to comprehensively secure the

entire hardware platform on which workloads and data are executed and accessed.

241 In the scope of this document, the *hardware platform* is a server (e.g., application server, storage

server, virtualization server) in a data center or edge compute facility. The server's hardware

243 platform, also called the *server platform*, represents the first part of the layered security

approach. *Hardware-enabled security*—security with its basis in the hardware platform—can

245 provide a stronger foundation than one offered by software or firmware, which can be modified

with relative ease. Hardware root of trust presents a smaller attack surface due to the small

codebase. Existing security implementations can be enhanced by providing a base-layer,

immutable hardware module that chains software and firmware verifications from the hardware

all the way to the application space or specified security control. In that manner, existing security

250 mechanisms can be trusted even more to accomplish their security goals without compromise,

even when there is a lack of physical security or attacks originate from the software layer.

252 This report explains hardware-based security techniques and technologies that can improve

253 server platform security and data protection for cloud data centers and edge computing. The rest 254 of this report covers the following topics:

- Section 2 provides an overview of hardware platform security.

- Section 3 discusses the measurement and verification of platform integrity.

- Section 4 explores software runtime attacks and protection mechanisms.

- Section 5 considers protecting data in use, also known as confidential computing.

- Section 6 examines remote attestation services, which can collate platform integrity

measurements to aid in integrity verification.

- Section 7 describes a number of cloud use case scenarios that take advantage of

hardware-enabled security.

- Section 8 states the next steps for this report and how others can contribute.

- The References section lists the cited references for this report.

- Appendix A describes vendor-agnostic technology examples.

- Appendix B describes Intel technology examples.

- Appendix C describes technology examples from AMD.

- Appendix D lists the acronym and abbreviations used in the report.

### • Appendix E provides a glossary of selected terms used in the report.

As technology and security capabilities evolve, NIST is continuously seeking feedback from the community on the content of the report and soliciting additional technology example contributions from other companies.

Although this document does not address other platforms like laptops, desktops, mobile devices, or Internet of Things (IoT) devices, the practices in this report can be adapted to support those platforms and their associated use cases.

Please send your feedback and comments to <u>hwsec@nist.gov</u>.

277

### 278 2 Hardware Platform Security Overview

The data center threat landscape has evolved in recent years to encompass more advanced attack

surfaces with more persistent attack mechanisms. With increased attention being applied to highlevel software security, attackers are pushing lower in the platform stack, forcing security

administrators to address a variety of attacks that threaten the platform firmware and hardware.

These threats can result in:

- Unauthorized access to and potential extraction of sensitive platform or user data,

including direct physical access to dual in-line memory modules (DIMMs)

- Modification of platform firmware, such as that belonging to the Unified Extensible

Firmware Interface (UEFI)/Basic Input Output System (BIOS), Board Management

Controller (BMC), Manageability Engine (ME), Peripheral Component Interconnect

Express (PCIE) device, and various accelerator cards

- Supply chain interception through the physical replacement of firmware or hardware with

malicious versions

- Access to data or execution of code outside of regulated geopolitical or other boundaries

- Circumvention of software and/or firmware-based security mechanisms

For example, LoJax, discovered in August 2018, manifests itself in UEFI malware, allowing it to continuously persist in the firmware layer despite operating system (OS) reinstallations, and thus remain invisible to standard kernel-based virus scans [1]. These attacks can be devastating to cloud environments because they often require server-by-server rebuilds or replacements, which can take weeks. Although still rare, these attacks are increasing as attackers become more sophisticated.

300 Workloads subject to specific regulations or containing sensitive data present additional security 301 challenges for multi-tenant clouds. While virtualization and containers significantly benefit 302 efficiency, adaptability, and scalability, these technologies consolidate workloads onto fewer 303 physical platforms and introduce the dynamic migration of workloads and data across platforms. 304 Consequently, cloud adoption results in a loss of consumer visibility and control over the 305 platforms that host virtualized workloads and data, and introduces the usage of third-party 306 infrastructure administrators. Cloud providers and cloud adopters follow a shared responsibility 307 model, where each party has responsibility for different aspects of the overall implementation. 308 Cloud providers can expose information related to infrastructure security and platform capability 309 in order to provide their tenants with security assurances. Furthermore, cloud providers often 310 have data centers that span multiple geopolitical boundaries, subjecting workload owners to 311 complicated legal and regulatory compliance requirements from multiple countries. Hybrid cloud

- 312 architectures, in particular, utilize multiple infrastructure providers, each with their own

- 313 infrastructure configurations and management.

- 314 Without physical control over or visibility into platform configurations, conventional security

- 315 best practices and regulatory requirements become difficult or impossible to implement. With

- 316 new regulatory structures like the European General Data Protection Regulation (GDPR)

- 317 introducing high-stakes fines for noncompliance, having visibility and control over where data

- 318 may be accessed is more important than ever before. Top concerns among security professionals

- 319 include the protection of workloads from general security risks, the loss or exposure of data in

- 320 the event of a data breach, and regulatory compliance.

321 Existing mitigations of threats against cloud servers are often rooted in firmware or software, 322 making them vulnerable to the same attack strategies. For example, if the firmware can be 323 successfully exploited, then the firmware-based security controls can most likely be 324 circumvented in the same fashion. Hardware-enabled security techniques can help mitigate these 325 threats by establishing and maintaining *platform trust*—an assurance in the integrity of the 326 underlying platform configuration, including hardware, firmware, and software. By providing 327 this assurance, security administrators can gain a level of visibility and control over where access 328 to sensitive workloads and data is permitted. Platform security technologies that establish 329 platform trust can provide notification or even self-correction of detected integrity failures. 330 Platform configurations can automatically be reverted back to a trusted state and give the

- 331 platform resilience against attack.

- All security controls must have a *root of trust (RoT)*—a starting point that is implicitly trusted.

- Hardware-based controls can provide an immutable foundation for establishing platform

integrity. Combining these functions with a means of producing verifiable evidence that these

integrity controls are in place and have been executed successfully is the basis of creating a

trusted platform. Minimizing the footprint of this RoT translates to reducing the number of

modules or technologies that must be implicitly trusted. This substantially reduces the attack

- 338 surface.

- 339 Platforms that secure their underlying firmware and configuration provide the opportunity for

- 340 trust to be extended higher in the software stack. Verified platform firmware can, in turn, verify

- 341 the OS boot loader, which can then verify other software components all the way up to the OS

- 342 itself and the hypervisor or container runtime layers. The transitive trust described here is

- 343 consistent with the concept of the *chain of trust (CoT)*—a method where each software module

- in a system boot process is required to measure the next module before transitioning control.

- 345 Rooting platform integrity and trust in hardware security controls can strengthen and

- 346 complement the extension of the CoT into the dynamic software category. There, the CoT can be

- 347 extended even further to include data and workload protection. Hardware-based protections

- 348 through CoT technology mechanisms can form a layered security strategy to protect data and

- 349 workloads as they move to multi-tenant environments in a cloud data center or edge computing

- 350 facility.

351 In addition, there are other hardware platform security technologies that can protect data at rest,

in transit, and in use by providing hardware-accelerated disk encryption or encryption-based

353 memory isolation. Many of these capabilities can help mitigate threats from speculative

354 execution and side-channel attacks. By using hardware to perform these tasks, the attack surface

- is mitigated, preventing direct access or modification of the required firmware. Isolating these

- 356 encryption mechanisms to dedicated hardware can allow performance to be addressed and

- 357 enhanced separately from other system processes as well. An example of hardware-based

- 358 isolation is discussed later in the document.

### **359 3 Platform Integrity Verification**

A key concept of trusted computing is verification of the underlying platform's integrity.Platform integrity is typically comprised of two parts:

- 362 • Cryptographic measurement of software and firmware. In this report, the term 363 measurement refers to calculating a cryptographic hash of a software or firmware 364 executable, configuration file, or other entity. If there is any change in an entity, a new measurement will result in a different hash value than the original [2]. By measuring 365 366 software and firmware prior to execution, the integrity of the measured modules and 367 configurations can be validated before the platform launches or before data or workloads 368 are accessed. These measurements can also act as cryptographic proof for compliance 369 audits.

- Firmware and configuration verification. When firmware and configuration measurements are made, local or remote attestations can be performed to verify if the desired firmware is actually running and if the configurations are authorized [3].

Attestation can also serve as the foundation for further policy decisions that fulfill various cloud security use case implementations. For instance, encryption keys can be released to client workloads if a proof is performed that the platform server is trusted and in compliance with policies.

- 377 In some cases, a third part is added to platform integrity:

- Firmware and configuration recovery. If the verification step fails (i.e., the attestations do not match the expected measurements), the firmware and configuration can automatically be recovered to a known good state, such as rolling back firmware to a trusted version. The process by which these techniques are implemented affects the overall strength of the assertion that the measured and verified components have not been accidentally altered or maliciously tampered. Recovery technologies allow platforms to maintain resiliency against firmware attacks and accidental provisioning mistakes [4].

- There are many ways to measure platform integrity. Most technologies center around the aforementioned concept of the CoT. In many cases, a hardware security module is used to store measurement data to be attested at a later point in time. The rest of this section discusses hardware security modules and various chain of trust technology implementations.

### 389 **3.1** Hardware Security Module (HSM)

390 A *hardware security module (HSM)* is "a physical computing device that safeguards and

- 391 manages cryptographic keys and provides cryptographic processing" [5]. Cryptographic

- 392 operations such as encryption, decryption, and signature generation/verification are typically

- 393 hosted on the HSM device, and many implementations provide hardware-accelerated

- 394 mechanisms for cryptographic operations.

- A *trusted platform module (TPM)* is a special type of HSM that can generate cryptographic keys and protect small amounts of sensitive information, such as passwords, cryptographic keys, and cryptographic hash measurements. [3] The TPM is a standalone device that can be integrated with server platforms, client devices, and other products. One of the main use cases of a TPM is

- 399 to store digest measurements of platform firmware and configuration during the boot process.

- 400 Each firmware module is measured by generating a digest, which is then extended to a TPM

- 401 platform configuration register (PCR). Multiple firmware modules can be extended to the same

- 402 PCR, and the TPM specification provides guidelines for which firmware measurements are

- 403 encompassed by each PCR [6].

404 TPMs also host functionality to generate binding and signing keys that are unique per TPM and 405 stored within the TPM non-volatile random-access memory (NVRAM). The private portion of 406 this key pair is decrypted inside the TPM, making it only accessible by the TPM hardware or 407 firmware. This can create a unique relationship between the keys generated within a TPM and a 408 platform system, restricting private key operations to the platform firmware that has ownership 409 and access to the specified TPM. Binding keys are used for encryption/decryption of data, while 410 signing keys are used to generate/verify cryptographic signatures. The TPM provides a random 411 number generator (RNG) as a protected capability with no access control. This RNG is used in 412 critical cryptographic functionality as an entropy source for nonces, key generation, and

- 413 randomness in signatures [6].

- 414 There are two versions of TPMs: 1.2 and 2.0. The 2.0 version supports additional security

- 415 features and algorithms [6]. TPMs also meet the National Institute of Standards and Technology

- 416 (NIST) Federal Information Processing Standard (FIPS) 140 validation criteria and support

- 417 NIST-approved cryptographic algorithms [7].

### 418 **3.2** The Chain of Trust (CoT)

419 The *chain of trust (CoT)* is a method for maintaining valid trust boundaries by applying a

- 420 principle of transitive trust. Each firmware module in the system boot process is required to

- 421 measure the next module before transitioning control. Once a firmware module measurement is 422 made, it is recommended to immediately extend the measurement value to an HSM register for

- 422 made, it is recommended to immediately extend the measurement value to an HSM register for 423 attestation at a later point in time [6]. The CoT can be extended further into the application

- 424 domain, allowing for files, directories, devices, peripherals, etc. to be measured and attested.

- 425 Every CoT starts with an RoT module. It can be composed of different hardware and firmware

- 426 components. For several platform integrity technologies, the RoT core firmware module is

- 427 rooted in immutable read-only memory (ROM) code. However, not all technologies define their

- 428 RoTs in this manner [6]. The RoT is typically separated into components that verify and

- 429 measure. The core root of trust for verification (CRTV) is responsible for verifying the first

- 430 component before control is passed to it. The core root of trust for measurement (CRTM) is the

- 431 first component that is executed in the CoT and extends the first measurement to the TPM. The

- 432 CRTM can be divided into a static portion (SCRTM) and dynamic portion (DCRTM). The

- 433 SCRTM is composed of elements that measure firmware at system boot time, creating an

- 434 unchanging set of measurements that will remain consistent across reboots. The DRTM allows a

- 435 CoT to be established without rebooting the system, permitting the root of trust for measurement

- 436 to be reestablished dynamically.

- 437 An RoT that is built with hardware protections will be more difficult to change, while an RoT

- 438 that is built solely in firmware can easily be flashed and modified.

- 439 Various platform integrity technologies build their own CoTs. Please refer to the following

- 440 technology examples in the appendices for more information:

- 441 <u>UEFI Secure Boot (SB)</u>

- 442 Intel Trusted Execution Technology (TXT)

- Intel Boot Guard

- Intel Platform Firmware Resilience (PFR)

- 445 Intel Technology Example Summary

- 446 <u>AMD Platform Secure Boot</u>

### 447 **3.3 Supply Chain Protection**

- 448 Organizations are increasingly at risk of supply chain compromise, whether intentional or

- 449 unintentional. Managing cyber supply chain risks requires, in part, ensuring the integrity, quality,

- 450 and resilience of the supply chain, its products, and its services. Cyber supply chain risks may 451 include counterfeiting, unauthorized production, tampering, theft, and insertion of malicious or

- 451 include counterleting, unauthorized production, tampering, theit, and insertion of malicious or 452 otherwise unexpected software and hardware, as well as poor manufacturing and development

- 452 otherwise unexpected software and nardware, as well as poor in 453 practices in the cyber supply chain [8] [9] [10].

- 454 Special technologies have been developed to help ascertain the authenticity and integrity of

- 455 platform hardware, including its firmware and configuration. These technologies help ensure that

- 456 platforms are not tampered with or altered from the time that they are assembled at the

- 457 manufacturer site to the time that they arrive at a consumer data center ready for installation.

- 458 Verification of these platform attributes is one aspect of securing the supply chain.<sup>1</sup> Some

- 459 technologies include an additional feature for locking the boot process or access to these

- 460 platforms until a secret is provided that only the consumer and manufacturer know.

- 461 Please refer to the following technology examples in the appendices for more information:

- 462 Intel Transparent Supply Chain (TSC)

- Intel PFR with Protection in Transit (PIT)

- 464

<sup>&</sup>lt;sup>1</sup> For more information on supply chain security, see the National Cybersecurity Center of Excellence (NCCoE) Supply Chain Assurance project page at <u>https://www.nccoe.nist.gov/projects/building-blocks/supply-chain-assurance</u>.

#### 4 **Software Runtime Protection Mechanisms** 465

466 This section describes various software runtime attacks and protection mechanisms.

#### 467 4.1 Return Oriented Programming (ROP) and Call/Jump Oriented Programming 468 (COP/JOP) Attacks

- 469 ROP attacks focus on utilizing buffer overflows and targeted memory overwrites of return

- 470 addresses in the stack. Attackers redirect return flows by corrupting addresses on the data stack

- 471 to be locations in already-executable code. These small selected sequences of code called

- 472 gadgets result in malicious modifications to the system or the invocation of normally

- 473 unauthorized operations. A common example is a call to the shell executable within the system

- 474 interface [11].

- COP/JOP attacks are similar to ROP attacks, relying on gadget building blocks. They target 475

- indirect jump instructions at the end of a gadget, many of which are intentionally emitted by the 476

- 477 compiler. However, a jump gadget performs a one-directional control flow transfer to its target,

- 478 as opposed to ROP, where gadgets return control back to the stack. This can make it difficult for

- 479 attackers to regain control after executing their gadgets, but solutions to this problem, such as the

- 480 one presented in [11], are beginning to appear.

- 481 Applications can utilize a parallel stack, known as the *shadow stack*, to help mitigate software

- 482 attacks which attempt to modify the control flow. Utilizing special hardware, the shadow stack is

- 483 used to store a copy of return addresses; the address is checked against the normal program stack

- 484 on return operations. If the content differs, an exception is generated, which can help prevent

- 485 malicious code from gaining control of the system with techniques such as ROP. In this way,

- 486 shadow stack hardware can help mitigate some of the most common and exploitable types of

- 487 software bugs.

- 488 Several defenses and preventative measures have been developed within industry to

- 489 accommodate ROP and COP/JOP attacks, including:

- 490 Intel Control-Flow Enforcement Technology (CET) •

#### 491 4.2 Address Translation Attacks

492 Commodity operating systems rely on virtual memory protection models enabled via paging 493 enforced by the processor memory management unit. Operating systems isolate process and

494 kernel memory using page tables managed by systems software, with access permissions such as

- 495 user/supervisor and read/write/execute (RWX). Process and kernel memory accesses are via

- 496 virtual addresses which are mapped to physical memory addresses via address translation 497

- structures. These structures used for address translation are critical to enforcing the isolation

- 498 model.

- 499 Modern operating systems are single address space kernels (as opposed to micro-kernels), which

- 500 provide good performance but have a large attack surface. A vulnerability in the kernel or driver

- 501 can be leveraged to escalate privileges of a malicious process. Kernel read/write primitives can

- 502 be leveraged with Write-What-Where vulnerabilities exploited from flaws discovered in kernel

- 503 code and/or drivers.

- 504 Heuristic defense mechanisms such as Page Table randomization can be bypassed with

- 505 information leaks achieved via malicious read/write primitives. Such information leaks are

- 506 performed by chaining together a set of system calls (*syscalls*). For example, one syscall can

- allocate RWX pool memory, and a second can exploit an arbitrary memory write to overwrite the

- address translation structures. Two types of attacks can utilize this methodology for nefarious

- 509 purposes. First, an attacker can redirect a virtual address in use to attacker-controlled contents

- 510 (many times set up in user-space memory). Second, an attacker can create a malicious alias

- 511 mapping which references desired physical memory with attacker-chosen permissions (e.g.,

- 512 read/write [RW] access to a page via an alias mapping that was originally read-only). It is

- 513 important for address translation protection mechanisms to block both of these types of attacks.

- 514 In addition to protecting the integrity of address translation structures, processors can also detect

- 515 and block any execution or data access setup by lower privilege code from a higher privilege

- 516 access. These protections establish boundaries, requiring code to execute with only the necessary

- 517 permissions and forcing elevated permission requests when needed.

- 518 Several defenses and preventative measures have been developed within industry to

- 519 accommodate memory page-table attacks, including the following:

- Intel Hypervisor Managed Linear Address Translation (HLAT)

- 521 Intel Supervisor Mode Execution Prevention (SMEP) and Supervisor Mode Access

522 Prevention (SMAP)

- 523 <u>AMD Supervisor Mode Execution Prevention (SMEP) and Supervisor Mode Access</u>

524 <u>Prevention (SMAP)</u>

- 525

#### 5 **Data Protection and Confidential Computing** 526

527 With the increase in adoption of consumer-based cloud services, virtualization has become a 528 necessity in cloud data center infrastructure. Virtualization simulates the hardware that multiple 529 cloud workloads run on top of. Each workload is isolated from others so that it has access to only 530 its own resources, and each workload can be completely encapsulated for portability [12] [13]. 531 Conventional virtual machines (VMs) have an isolated kernel space running all aspects of a 532 workload alongside the kernel. Today, the virtualized environment has been extended to include 533 containers and full-featured workload orchestration engines. Containers offer application 534 portability by sharing an underlying kernel, which drastically reduces workload-consumed 535 resources and increases performance.

- 536 While containers can provide a level of convenience, vulnerabilities in the kernel space and

- 537 shared layers can be susceptible to widespread exploitation, making security for the underlying

- 538 platform even more important. With the need for additional protection in the virtualized

- 539 workspace, an emphasis has been placed on encrypting data both at rest and while in use. At-rest

- 540 encryption provides protection for data on disk. This typically refers to an unmounted data store

- 541 and protects against threats such as the physical removal of a disk drive. Protecting and securing

- 542 cloud data while in use, also referred to as confidential computing, utilizes hardware-enabled

- 543 features to isolate and process encrypted data in memory so that the data is at less risk of 544 exposure and compromise from concurrent workloads or the underlying system and platform

- 545 [14]. This section describes technologies that can be leveraged for providing confidential

- 546 computing for cloud and edge.

- 547 A trusted execution environment (TEE) is an area or enclave protected by a system processor.

- 548 Sensitive secrets like cryptographic keys, authentication strings, or data with intellectual property

- 549 and privacy concerns can be preserved within a TEE, and operations involving these secrets can

- 550 be performed within the TEE, thereby eliminating the need to extract the secrets outside of the

- 551 TEE. A TEE also helps ensure that operations performed within it and the associated data cannot

- 552 be viewed from outside, not even by privileged software or debuggers. Communication with the

- 553 TEE is designed to only be possible through designated interfaces, and it is the responsibility of

- 554 the TEE designer/developer to define these interfaces appropriately. A good TEE interface limits

- 555 access to the bare minimum required to perform the task.

#### 556 5.1 **Memory Isolation**

- 557 There are many technologies that provide data protection via encryption. Most of these solutions

- 558 focus on protecting the respective data while at rest and do not cover the fact that the data is 559

- decrypted and vulnerable while in use. Applications running in memory share the same platform

- 560 hardware and can be susceptible to attacks either from other workloads running on the same 561 hardware or from compromised cloud administrators. There is a strong desire to secure

- 562 intellectual property and ensure that private data is encrypted and not accessible at any point in

- 563 time, particularly in cloud data centers and edge computing facilities. Various hardware

- 564 technologies have been developed to encrypt content running in platform memory.

- 565 Please refer to the following technology examples in the appendices for more information:

- Intel TME and Multi-Key Total Memory Encryption (MKTME)

- <u>AMD Secure Memory Encryption (SME)/Transparent Memory Encryption (TSME)</u>

### 568 **5.2** Application Isolation

569 Application isolation utilizes a TEE to help protect the memory reserved for an individual 570 application. The trust boundary associated with the application is restricted to only the central 571 processing unit (CPU). Future generations of these techniques will allow entire applications to be 572 isolated in their own enclaves rather than only protecting specific operations or memory. By 573 using separate application enclaves with unique per-application keys, sensitive applications can 574 be protected against data exposure, even to malicious insiders with access to the underlying 575 platform. Implementations of application isolation will typically involve developer integration of 576 a toolkit within the application layer, and it is the developer's responsibility to ensure secure 577 TEE design.

- 578 Please refer to the following technology examples in the appendices for more information:

- Intel Software Guard Extensions (SGX)

### 580 **5.3 VM Isolation**

- 581 As new memory and execution isolation technologies become available, it is more feasible to

- 582 isolate entire VMs. VMs already enjoy a degree of isolation due to technologies like hardware-

- assisted virtualization, but the memory of each VM remains in the clear. Some existing memory

- 584 isolation technologies require implicit trust of the virtual machine manager (VMM). Isolation

- technologies in future platform generations will remove the VMM from the trust boundary and

- allow full encryption of VM memory with per-VM unique keys, protecting the VMs from not

- 587 only malicious software running on the hypervisor host but also rogue firmware.

- 588 VM isolation can be used to help protect workloads in multi-tenant environments like public and

- 589 hybrid clouds. Isolating entire VMs translates to protection against malicious insiders at the

- 590 cloud provider, or malware exposure and data leakage to other tenants with workloads running

- on the same platform. Many modern cloud deployments use VMs as container worker nodes.

- 592 This provides a highly consistent and scalable way to deploy containers regardless of the

- <sup>593</sup> underlying physical platforms. With full VM isolation, the virtual workers hosting container

- 594 workloads can be effectively isolated without impacting the benefits of abstracting the container

- 595 from the underlying platform.

- 596 Please refer to the following technology examples in the appendices for more information:

- 597 Intel Trust Domain Extensions (TDX)

- 598 <u>AMD Secure Encrypted Virtualization (SEV)</u>

### 599 **5.4 Cryptographic Acceleration**

- 600 Encryption is quickly becoming more widespread in data center applications as industry adopts

- 601 more standards and guidelines regarding the sensitivity of consumer data and intellectual

- 602 property. Because cryptographic operations can drain system performance and consume large

- amounts of compute resources, the industry has adopted specialized hardware interfaces called

- 604 *cryptographic accelerators*, which offload cryptographic tasks from the main processing unit

- 605 onto a separate coprocessor chip. Cryptographic accelerators often come in the form of pluggable

- 606 peripheral adapter cards.

- 607 Please refer to the following technology examples in the appendices for more information:

- Intel Advanced Encryption Standard New Instructions (AES-NI)

- Intel QuickAssist Technology (QAT) with Intel Key Protection Technology (KPT)

- 610 AMD Advanced Encryption Standard

- 611

### 612 6 Remote Attestation Services

613 Measuring a server's firmware/configuration and extending these measurements to a hardware interface can help keep track of which firmware is running on a platform. Some platform 614 615 integrity technologies can even perform local attestation and enforcement of firmware and configuration on a server. However, data centers are usually made up of thousands of servers, 616 617 and keeping track of them and their respective firmware is an overwhelming task for an operator. 618 A remote service can address this by collating server information and measurement details. 619 Cryptographic signatures can be used to ensure the integrity of transferred measurement data. 620 Furthermore, the remote service can be used to define allowlist policies, specifying which 621 firmware versions and event measurements are acceptable for servers in a particular data center 622 environment. This service would verify or attest each server's collected data against these 623 policies, feeding the results into a policy orchestrator to report, alert, or enforce rules based on 624 the events.

- 625 A remote attestation service can provide additional benefits besides verifying server firmware.

- 626 Specifying allowlist policies for specific firmware versions can allow data center administrators

- 627 to easily invalidate old versions and roll out new upgrades. In some cases, certain hardware

- 628 technologies and associated capabilities on platforms can be discoverable by their specific event

- 629 log measurements recorded in an HSM. The information tracked in this remote attestation

- 630 service can even be exposed through the data center administration layer directly to the

- 631 enterprise user. This would give endpoint consumers hardware visibility and the ability to

- 632 specify firmware requirements or require platform features for the hardware on which their

- 633 services are running.

- 634 The key advantage to remote attestation is the enforcement of compliance across all hardware

- 635 systems in a data center. The ability to verify against a collective allowlist as opposed to a local

- 636 system enforcing a supply chain policy provides operators more flexibility and control in a

- 637 cryptographically secured manner. These enforcement mechanisms can even be combined to

- 638 provide stronger security policies.

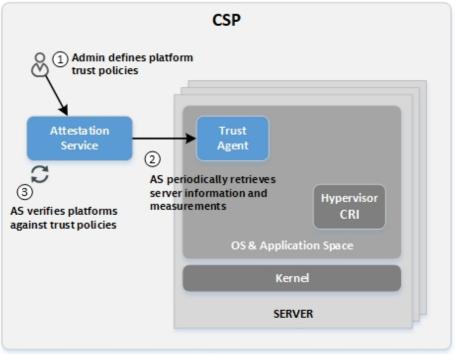

### 639 6.1 Platform Attestation

- 640 Figure 1 shows a remote attestation service (AS) collecting platform configurations and integrity

- 641 measurements from data center servers at a cloud service provider (CSP) via a trust agent service

- running on the platform servers. A cloud operator is responsible for defining allowlisted trust

- 643 policies. These policies should include information and expected measurements for desired

- 644 platform CoT technologies. The collected host data is compared and verified against the policies,

- and a report is generated to record the relevant trust information in the AS database.

### Platform Verification

646

### 647

### Figure 1: Notional Example of Remote Attestation Service

648 Platform attestation can be extended to include application integrity or the measurement and

verification of the hypervisor container runtime interface (CRI) and applications installed on

bare-metal servers. During boot time, an application agent on the server can measure operator-

651 specified files and directories that pertain to particular applications. An allowlist trust policy can

be defined to include these expected measurements, and this policy can be included in the overall

653 trust assessment of the platform in the remote AS. By extending measurements to a platform

TPM, applications running on the bare-metal server can be added to the CoT. The components of

655 the trust agent and application agent can be added to the policy and measured alongside other

applications to ensure that the core feature elements are not tampered with. For example, a

657 typical Linux implementation of the application agent could run inside initrd, and measurements

made on the filesystem could be extended to the platform TPM.

659 An additional feature commonly associated with platform trust is the concept of *asset tagging*.

660 Asset tags are simple key value attributes that are associated with a platform like location,

661 company name, division, or department. These key value attributes are tracked and recorded in a

662 central remote service, such as the AS, and can be provisioned directly to a server through the

trust agent. The trust agent can then secure these attribute associations with the host platform by

writing hash measurement data for the asset tag information to a hardware security chip, such as

the platform TPM NVRAM. Measurement data is then retrieved by the AS and included in the

666 platform trust report evaluation.

667 Please refer to the following technology examples in the appendices for more information:

• Intel Security Libraries for the Data Center (ISecL-DC)

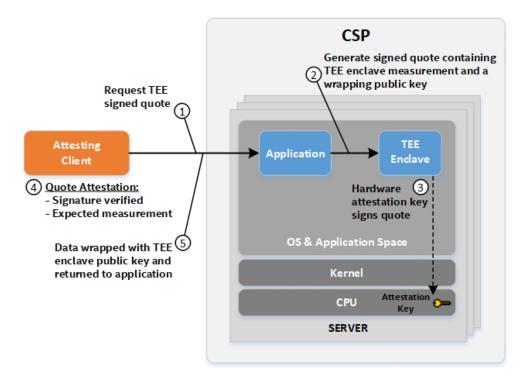

### 669 6.2 TEE Attestation

670 There are instances when the high assurance that the output of the processing in a TEE can be

671 trusted should be extended to an external attesting client. This is achieved thanks to a TEE

attestation flow. *TEE attestation* involves the generation of a verifiable cryptographic quote of

673 the enclave by the TEE. The quote is then sent to the attesting client, which can validate the 674 signature of the quote. If the signature is valid, the attesting client concludes that the remote code

- 675 is running in a genuine TEE enclave.

- 676 A quote usually contains the measurement of the TEE enclave, as well as data related to the

- authenticity of the TEE and the compliant version of it. The measurement is a digest of the

- 678 content of the enclave (e.g., code and static data) and other information. The measurement

- obtained at build time is typically known to the attesting client and is compared against a

- 680 measurement contained in the quote that is actively taken during runtime. This allows the

- attesting client to determine that the remote code has not been tampered with. A quote may also

- 682 contain the enclave's developer signature and platform trusted computing base (TCB)

- 683 information. The authenticity and version of the TEE are verified against TEE provider

- 684 certificates that are accessible to the tenant or attesting client.

- The quote may also contain the public key part of an enclave key pair or a secure hash of the

- 686 public/private key part if there is a limitation on the size of the quote. In the latter case, the

- 687 public key part must be communicated along with the quote. The public key allows the attesting

- 688 client to wrap secrets that it wants to send to the enclave. This capability allows the attesting

- 689 client to provision secrets directly to the TEE enclave without needing to trust any other software

- 690 running on the server.

- 691 Figure 2 shows an example TEE attestation flow.

693

Figure 2: Notional Example of TEE Attestation Flow

### **695** 7 Cloud Use Case Scenarios Leveraging Hardware-Enabled Security

696 This section describes a number of cloud use case scenarios that take advantage of the hardware-

697 enabled security capability and trust attestation capability integrated with the operator698 orchestration tool to support various security and compliance objectives.

### 699 **7.1 Visibility to Security Infrastructure**

700 A typical attestation includes validation of the integrity of platform firmware measurements.

701 These measurements are unique to a specific BIOS/UEFI version, meaning that the attestation

report provides visibility into the specific firmware version currently in use, in addition to the

703 integrity of that firmware. Attestation can also include hardware configuration and feature

support information, both by attesting feature support directly and by resulting in different

- 705 measurements based on which platform integrity technologies are used.

- 706 Cryptographically verifiable reports of platform integrity and security configuration details (e.g.,

- 707 BIOS/UEFI versions, location information, application versions) are extremely useful for

- 708 compliance auditing. These attestation reports for the physical platform can be paired with

- workload launch or key release policies, providing traceability to confirm that data and

- vorkloads have only been accessed on compliant hardware in compliant configurations with

- 711 required security technologies enabled.

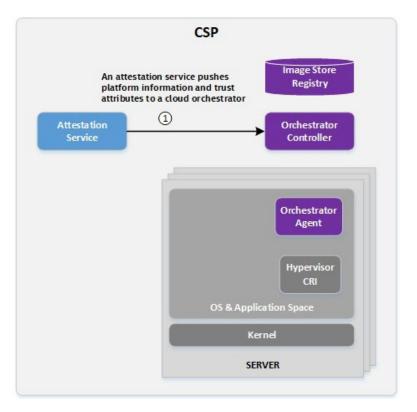

### 712 **7.2 Workload Placement on Trusted Platforms**

- 713 Platform information and verified firmware/configuration measurements retained within an

- attestation service can be used for policy enforcement in countless use cases. One example is

- 715 orchestration scheduling. Cloud orchestrators, such as Kubernetes and OpenStack, provide the

- ability to label server nodes in their database with key value attributes. The attestation service

- can publish trust and informational attributes to orchestrator databases for use in workload

- 718 scheduling decisions. Figure 3 illustrates this.

### 720

Figure 3: Notional Example of Orchestrator Platform Labeling

In OpenStack, this can be accomplished by labeling nodes using custom traits. Workload images can be uploaded to an image store containing metadata that specifies required trait values to be

associated with the node that is selected by the scheduling engine. In Kubernetes, nodes can be

124 labeled in etcd via node selector or node affinity. Custom resource definitions (CRDs) can be

written and plugged into Kubernetes to receive label values from the attestation service and

associate them with nodes in the etcd. When a deployment or container is launched, node

selector or node affinity attributes can be included in the configuration yaml to instruct

Kubernetes to only select nodes that have the specified labels. Other orchestrator engines and

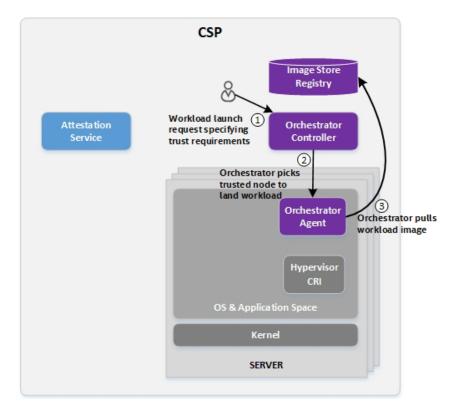

flavors can be modified to accommodate a similar use case. Figure 4 illustrates how an

730 orchestrator can be configured to only launch workloads on trusted platforms or platforms with

731 specified asset tag attributes.

733

Figure 4: Notional Example of Orchestrator Scheduling

### 734 7.3 Asset Tagging and Trusted Location

735 Trusted geolocation is a specific implementation of the aforementioned trusted asset tag feature 736 used with platform attestation. Key attribute values specifying location information are used as

used with platform attestation. Key attribute values specifying location information are used as asset tags and provisioned to server hardware, such as the TPM. In this way, location information

asset tags and provisioned to server hardware, such as the TPM. In this way, location informatican be included in platform attestation reports and therefore consumed by cloud orchestrators,

infrastructure management applications, policy engines, and other entities [15]. Orchestration

vising asset tags can be used to segregate workloads and data access in a wide variety of

scenarios. Geolocation can be an important attribute to consider with hybrid cloud environments

subject to regulatory controls like GDPR, for example. Violating these constraints by allowing

access to data outside of specific geopolitical boundaries can trigger substantial penalties.

744 In addition to location, the same principle can apply to other sorts of tag information. For

example, some servers might be tagged as appropriate for storing health information subject to

746 Health Insurance Portability and Accountability Act (HIPAA) compliance. Data and workloads

requiring this level of compliance should only be accessed on platforms configured to meet those

748 compliance requirements. Other servers may be used to store or process information and

749 workloads not subject to HIPAA requirements. Asset tags can be used to flag which servers are

appropriate for which workloads beyond a simple statement of the integrity of those platforms.

751 The attestation mechanisms help ensure that the asset tag information is genuine, preventing easy

752 subversion.

753 Outside of specific regulatory requirements, an organization may wish to segregate workloads by

department. For example, human resources and finance information could be restricted to

- platforms with different security profiles, and big data workloads could be required to run on

- 756 platforms tagged for performance capabilities. For cloud orchestration platforms that do not

- natively support discovery or scheduling of workloads based on specific platform features, asset

- tags can provide a mechanism for seamlessly adding such a capability. For example, workloads that require Intel SGX can be orchestrated to only run on platforms that support the SGX

- that require Intel SGX can be orchestrated to only run on platforms that support the SGX

platform feature, even if the cloud platform does not natively discover support for SGX. The

- 760 platform feature, even if the cloud platform does not natively discover support for SGX. The 761 open-ended user-configurable asset tag functionality allows virtually any level of subdivision of

- 761 open-ended user-configurable asset tag functionality allows virtually any level of subdivision of 762 resources for business, security, or regulatory needs

- resources for business, security, or regulatory needs.

### 763 7.4 Workload Confidentiality

- 764 Consumers who place their workloads in the cloud or the edge are typically forced to accept that

- their workloads are secured by their service providers without insight or knowledge as to what

- security mechanisms are in place. The ability for end users to encrypt their workload images can

- 767 provide at-rest cryptographic isolation to protect consumer data and intellectual property. Key

- control is integral to the workload encryption process. While it is preferable to transition key

- storage, management, and ownership to the endpoint consumer, an appropriate key release policy

- must be defined that includes a guarantee from the service provider that the utilized hardware

- platform and firmware are secure and uncompromised.

- There are several key management solutions (KMSs) in production that provide services to

- create and store keys. Many of these are compliant with the industry-standardized Key

- 774 Management Interoperability Protocol (KMIP) and can be deployed within consumer enterprises.

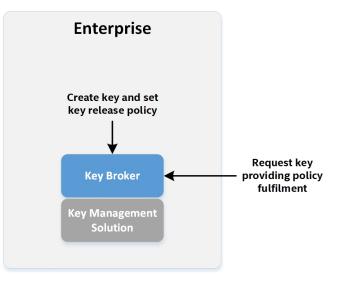

- The concept is to provide a thin layer on top of the KMS called a *key broker*, as illustrated in

- Figure 5, that applies and evaluates policies to requests that come into the KMS. Supported

- requests to the key broker include key creation, key release policy association, and key request

- by evaluating associated policies. The key release policy can be any arbitrary set of rules that

- must be fulfilled before a key is released. The policy for key release is open-ended and meant to

- be easily extendible, but for the purpose of this discussion, a policy associated with platformtrust is assumed.

- 781 trust is assumed.

Figure 5: Notional Example of Key Brokerage

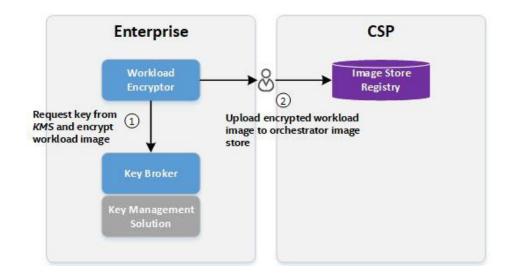

- 784 Once the key policy has been determined, a KMS-created and managed key can be used to

- encrypt a workload image, as shown in Figure 6. The enterprise user may then upload the

- 786 encrypted image to a CSP orchestrator image store or registry.

Figure 6: Notional Example of Workload Image Encryption

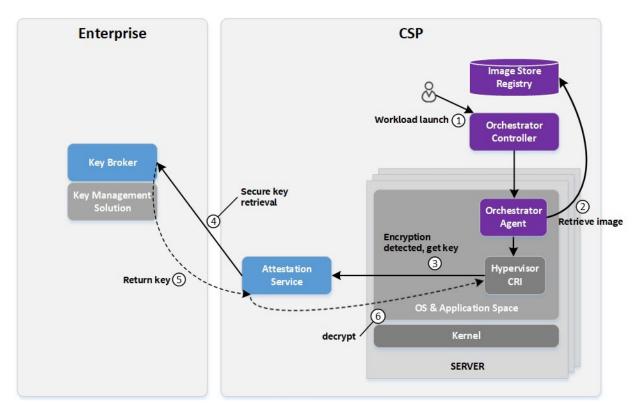

789 The key retrieval and decryption process is the most complex piece of the workload

confidentiality story, as Figure 7 shows. It relies on a secure key transfer between the enterprise

and CSP with an appropriate key release policy managed by the key broker. The policy for key release discussed here is based on platform trust and the valid proof thereof. The policy can also