# NBS TECHNICAL NOTE 681

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

QC 100 .U5753 No.681 1976 c.2

## PERIODICALS

JOURNAL OF RESEARCH reports National Bureau of Standards research and development in physics, mathematics, and chemistry. It is published in two sections, available separately:

#### Physics and Chemistry (Section A)

Papers of interest primarily to scientists working in these fields. This section covers a broad range of physical and chemical research, with major emphasis on standards of physical measurement, fundamental constants, and properties of matter. Issued six times a year. Annual subscription: Domestic, \$17.00; Foreign, \$21.25.

#### • Mathematical Sciences (Section B)

Studies and compilations designed mainly for the mathematician and theoretical physicist. Topics in mathematical statistics, theory of experiment design, numerical analysis, theoretical physics and chemistry, logical design and programming of computers and computer systems. Short numerical tables. Issued quarterly. Annual subscription: Domestic, \$9.00; Foreign, \$11.25.

DIMENSIONS/NBS (formerly Technical News Bulletin)—This monthly magazine is published to inform scientists, engineers, businessmen, industry, teachers, students, and consumers of the latest advances in science and technology, with primary emphasis on the work at NBS. The magazine highlights and reviews such issues as energy research, fire protection, building technology, metric conversion, pollution abatement, health and safety, and consumer product performance. In addition, it reports the results of Bureau programs in measurement standards and techniques, properties of matter and materials, engineering standards and services, instrumentation, and automatic data processing.

Annual subscription: Domestic, \$9.45; Foreign, \$11.85.

#### NONPERIODICALS

Monographs—Major contributions to the technical literature on various subjects related to the Bureau's scientific and technical activities.

Handbooks—Recommended codes of engineering and industrial practice (including safety codes) developed in cooperation with interested industries, professional organizations, and regulatory bodies.

Special Publications—Include proceedings of conferences sponsored by NBS, NBS annual reports, and other special publications appropriate to this grouping such as wall charts, pocket cards, and bibliographies.

Applied Mathematics Series—Mathematical tables, manuals, and studies of special interest to physicists, engineers, chemists, biologists, mathematicians, computer programmers, and others engaged in scientific and technical work.

National Standard Reference Data Series—Provides quantitative data on the physical and chemical properties of materials, compiled from the world's literature and critically evaluated. Developed under a world-wide

The following current-awareness and literature-survey bibliographies are issued periodically by the Bureau: Cryogenic Data Center Current Awareness Service

A literature survey issued biweekly. Annual subscription: Domestic, \$20.00; foreign, \$25.00.

Liquefied Natural Gas. A literature survey issued quarterly. Annual subscription: \$20.00.

Superconducting Devices and Materials. A literature

program coordinated by NBS. Program under authority of National Standard Data Act (Public Law 90-396).

NOTE: At present the principal publication outlet for these data is the Journal of Physical and Chemical Reference Data (JPCRD) published quarterly for NBS by the American Chemical Society (ACS) and the American Institute of Physics (AIP). Subscriptions, reprints, and supplements available from ACS, 1155 Sixteenth St. N. W., Wash. D. C. 20056.

Building Science Series—Disseminates technical information developed at the Bureau on building materials, components, systems, and whole structures. The series presents research results, test methods, and performance criteria related to the structural and environmental functions and the durability and safety characteristics of building elements and systems.

Technical Notes—Studies or reports which are complete in themselves but restrictive in their treatment of a subject. Analogous to monographs but not so comprehensive in scope or definitive in treatment of the subject area. Often serve as a vehicle for final reports of work performed at NBS under the sponsorship of other government agencies.

Voluntary Product Standards—Developed under procedures published by the Department of Commerce in Part 10, Title 15, of the Code of Federal Regulations. The purpose of the standards is to establish nationally recognized requirements for products, and to provide all concerned interests with a basis for common understanding of the characteristics of the products. NBS administers this program as a supplement to the activities of the private sector standardizing organizations.

Federal Information Processing Standards Publications (FIPS PUBS)—Publications in this series collectively constitute the Federal Information Processing Standards Register. Register serves as the official source of information in the Federal Government regarding standards issued by NBS pursuant to the Federal Property and Administrative Services Act of 1949 as amended, Public Law 89-306 (79 Stat. 1127), and as implemented by Executive Order 11717 (38 FR 12315, dated May 11, 1973) and Part 6 of Title 15 CFR (Code of Federal Regulations).

Consumer Information Series—Practical information, based on NBS research and experience, covering areas of interest to the consumer. Easily understandable language and illustrations provide useful background knowledge for shopping in today's technological marketplace.

NBS Interagency Reports (NBSIR)—A special series of interim or final reports on work performed by NBS for outside sponsors (both government and non-government). In general, initial distribution is handled by the sponsor; public distribution is by the National Technical Information Service (Springfield, Va. 22161) in paper copy or microfiche form.

Order NBS publications (except NBSIR's and Bibliographic Subscription Services) from: Superintendent of Documents, Government Printing Office, Washington, D.C. 20402.

# **BIBLIOGRAPHIC SUBSCRIPTION SERVICES**

survey issued quarterly. Annual subscription: \$20.00. Send subscription orders and remittances for the preceding bibliographic services to National Bureau of Standards, Cryogenic Data Center (275.02) Boulder, Colorado 80302.

Electromagnetic Metrology Current Awareness Service Issued monthly. Annual subscription: \$24.00. Send subscription order and remittance to Electromagnetics Division, National Bureau of Standards, Boulder, Colo. 80302.

# A Satellite-Controlled Digital Clock

t. Technical lote no. 281

J. V. Cateora D. D. Davis D. W. Hanson

Time and Frequency Division Institute for Basic Standards National Bureau of Standards Boulder, Colorado 80302

U.S. DEPARTMENT OF COMMERCE, Elliot L. Richardson, Secretary James A. Baker, III, Under Secretary Dr. Betsy Ancker-Johnson, Assistant Secretary for Science and Technology

NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Acting Director

**Issued June 1976**

NATIONAL BUREAU OF STANDARDS TECHNICAL NOTE 681 Nat. Bur. Stand. (U.S.), Tech Note 681, 46 pages (June 1976)

CODEN: NBTNAE

CONTENTS

| 1.  | INTRODUCTION |                    |                                                                                   |    |  |

|-----|--------------|--------------------|-----------------------------------------------------------------------------------|----|--|

| 2.  | SYS          | SYSTEM DESCRIPTION |                                                                                   |    |  |

|     | 2.1          | FORMA              | r                                                                                 | 3  |  |

|     | 2.2          | TIME (             | CODE DISTRIBUTION                                                                 | 3  |  |

|     | 2.3          | TIME (             | CODE GENERATION                                                                   | 6  |  |

|     | 2.4          | TIME (             | CODE RECEPTION                                                                    | 6  |  |

| 3.  | DIG          | ITAL CLO           | OCK DESCRIPTION                                                                   | 10 |  |

|     | 3.1          | DIGIT              | AL CLOCK CIRCUITRY                                                                | 14 |  |

|     | 3.2          | SOFTW              | ARE LISTING                                                                       | 20 |  |

|     | 3.3          | DIGIT              | AL CLOCK PERFORMANCE                                                              | 20 |  |

| 4.  | CONCLUSION   |                    |                                                                                   | 40 |  |

| 5.  | REFI         | ERENCES            |                                                                                   | 41 |  |

|     |              |                    | FIGURES                                                                           |    |  |

| FIG | URE .        | 1                  | SMS/GOES COVERAGE                                                                 | 2  |  |

| FIG | URE 2        | 2                  | INTERROGATION MESSAGE AND TIME CODE FORMATS                                       | 4  |  |

| FIG | URE (        | 3                  | TIME CODE DISTRIBUTION                                                            | 5  |  |

| FIG | URE 4        | 4                  | TIME CODE GENERATION AND CONTROL EQUIPMENT                                        | 7  |  |

| FIG | URE !        | 5                  | RECEIVER BLOCK DIAGRAM                                                            | 8  |  |

| FIG | URE (        | 5                  | TIME DELAY THROUGH A GEOSTATIONARY SATELLITE AT 115° WEST LONGITUDE               | 8  |  |

| FIG | URE '        | 7a                 | TYPICAL DELAY DIURNALS FOR THE EASTERN SATELLITE WITH WALLOPS ISLAND TRANSMITTING | 9  |  |

| FIG | URE '        | 7b                 | TYPICAL DELAY DIURNALS FOR THE WESTERN SATELLITE WITH WALLOPS ISLAND TRANSMITTING | 9  |  |

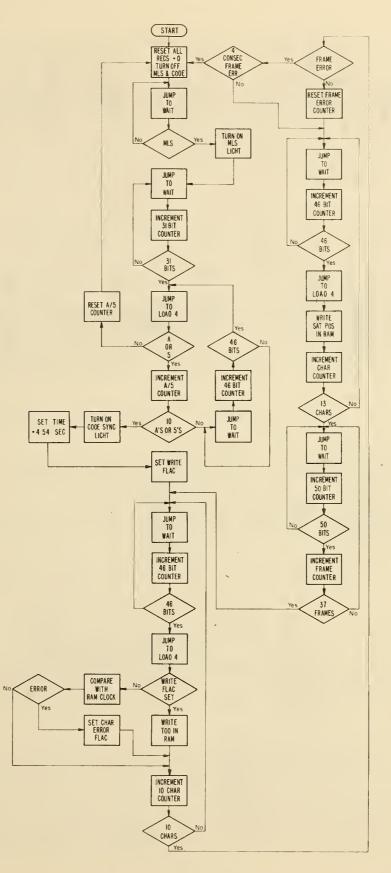

| FIG | URE 8        | Ba                 | SOFTWARE FLOW CHART                                                               | 11 |  |

| FIG | URE 8        | Bb                 | SOFTWARE FLOW CHART (CONTINUED)                                                   | 12 |  |

| FIG | URE 9        | ∂a                 | RAM MAP                                                                           | 15 |  |

| FIG | URE 9        | Эb                 | REGISTER MAP                                                                      | 15 |  |

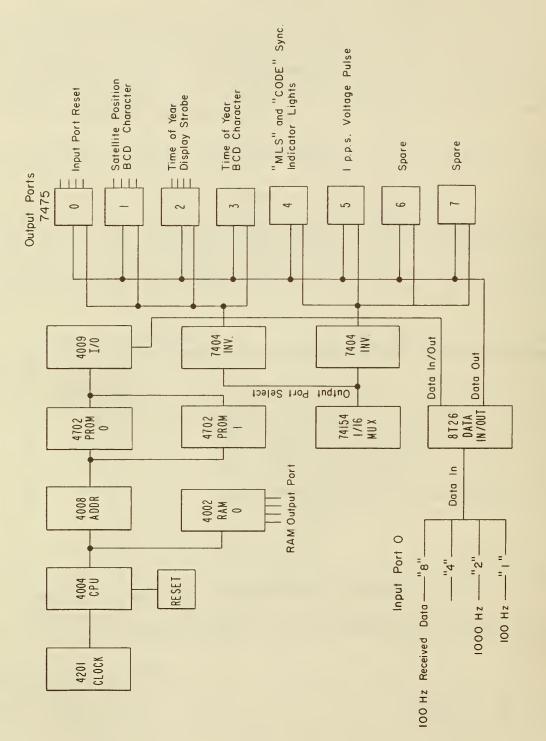

| FIG | URE :        | 10                 | DIGITAL CLOCK BLOCK DIAGRAM                                                       | 16 |  |

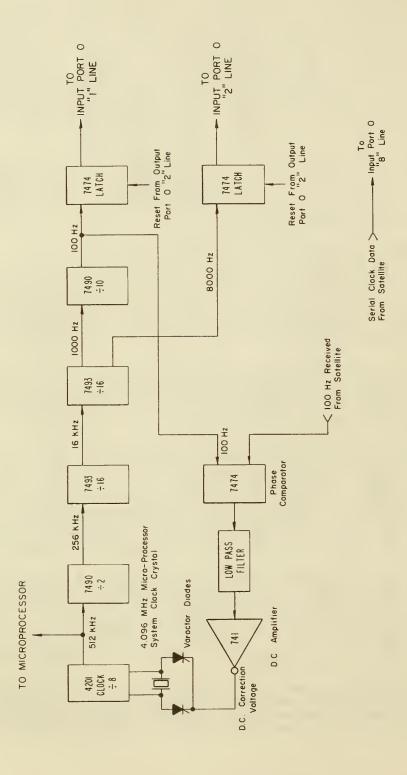

| FIG | URE :        | 11                 | MICROPROCESSOR CLOCK PHASE LOCKED TO DATA CLOCK                                   | 18 |  |

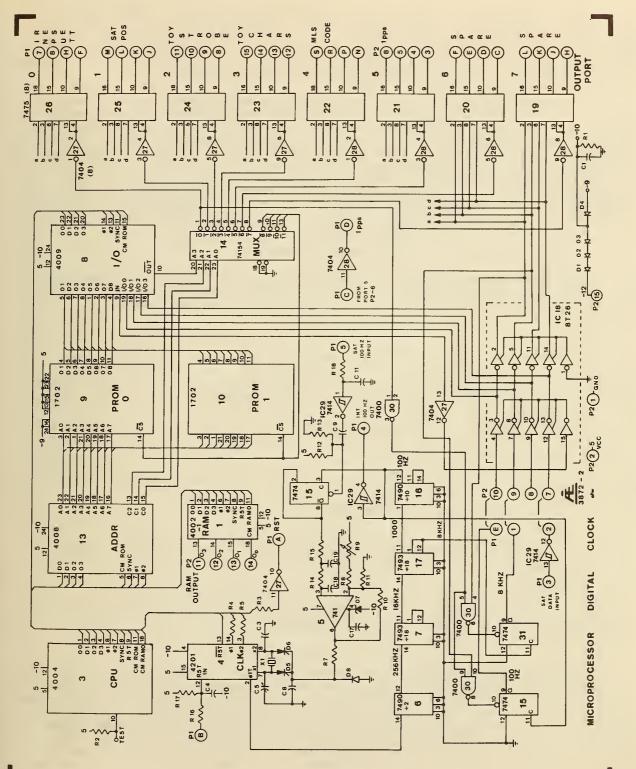

| FIG | URE :        | 12                 | DIGITAL CLOCK SCHEMATIC                                                           | 19 |  |

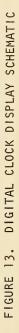

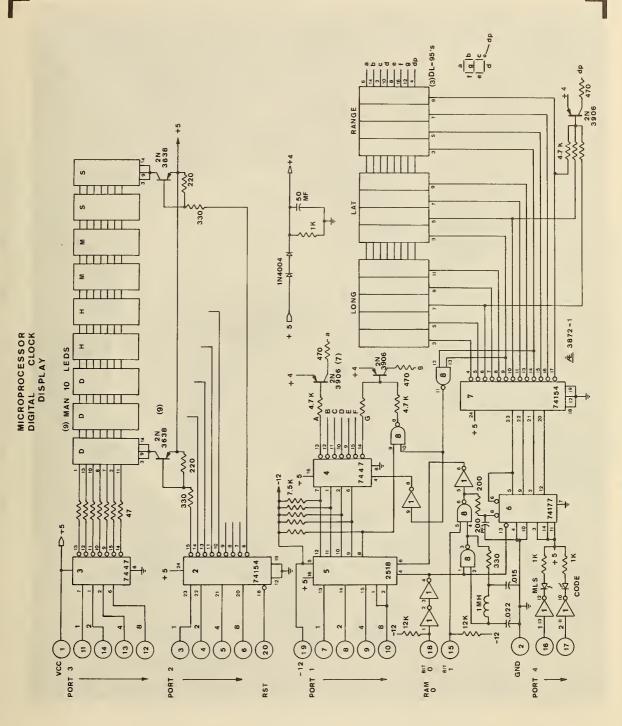

| FIG | URE .        | 13                 | DIGITAL CLOCK DISPLAY SCHEMATIC                                                   | 21 |  |

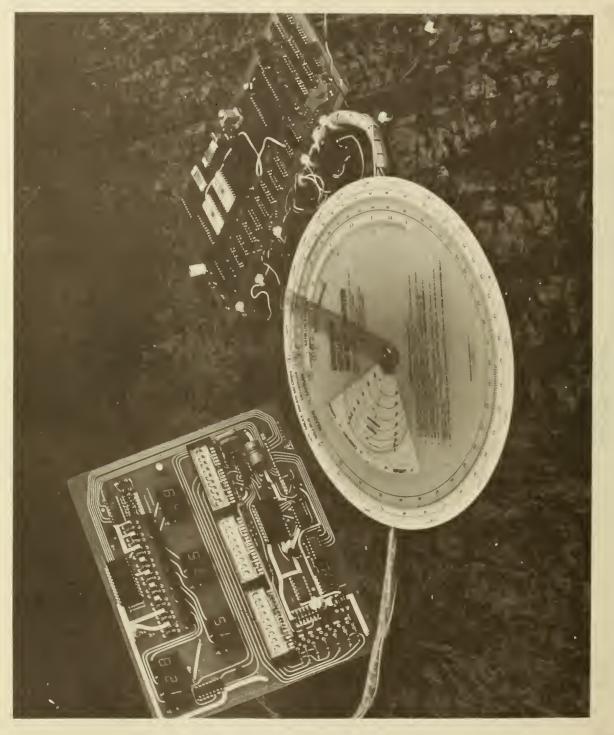

| FIG | URE .        | 14                 | DIGITAL CLOCK, DISPLAY, AND PATH DELAY SLIDE RULE                                 | 22 |  |

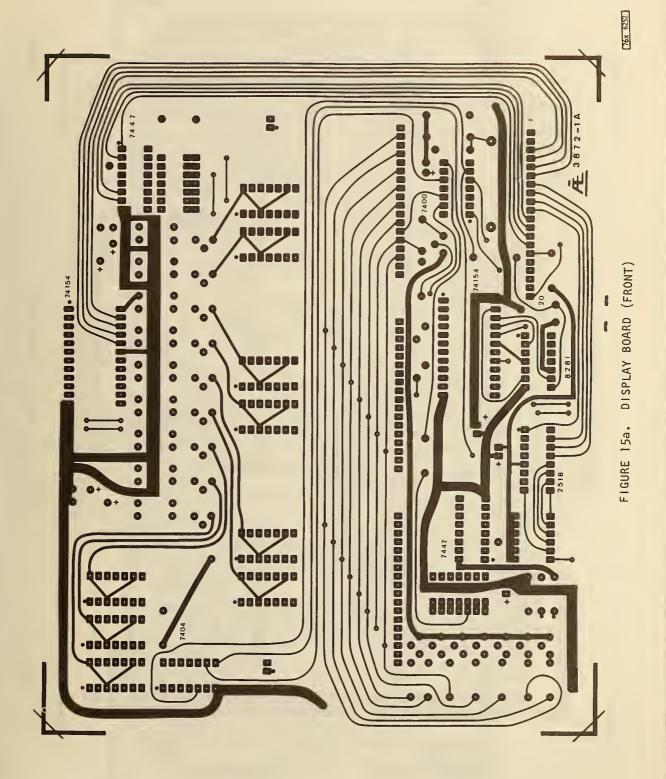

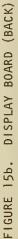

| FIGURE | 15a | DISPLAY BOARD (FRONT)                       | 23 |  |

|--------|-----|---------------------------------------------|----|--|

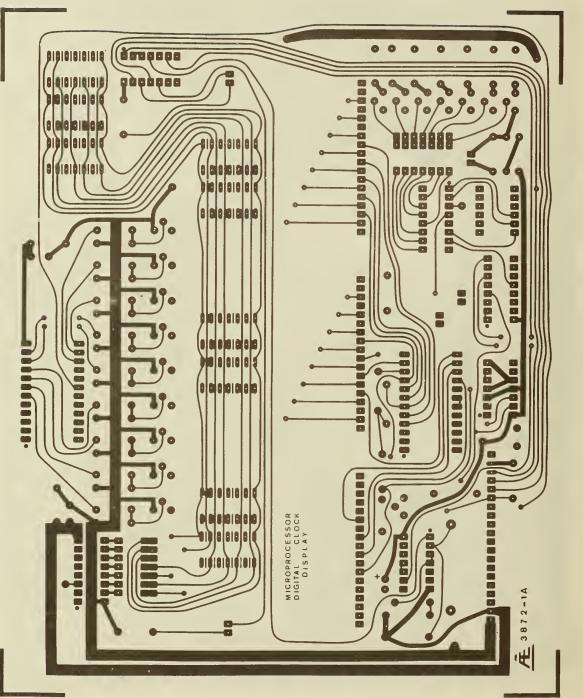

| FIGURE | 15b | DISPLAY BOARD (BACK)                        |    |  |

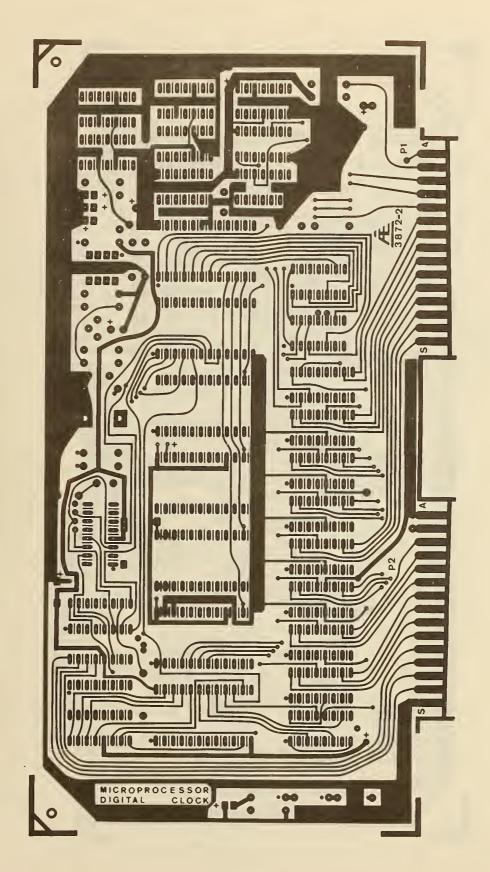

| FIGURE | 15c | CLOCK BOARD (FRONT)                         |    |  |

| FIGURE | 15d | CLOCK BOARD (BACK)                          |    |  |

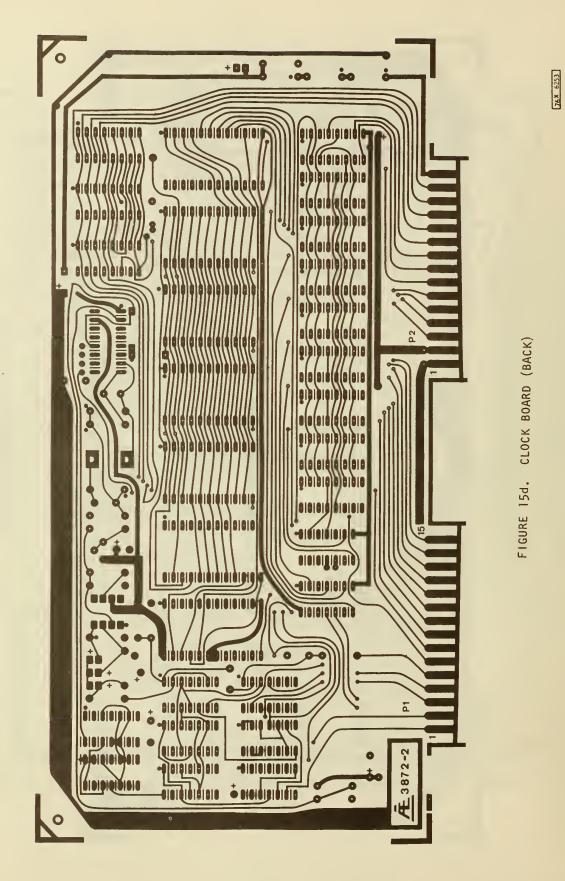

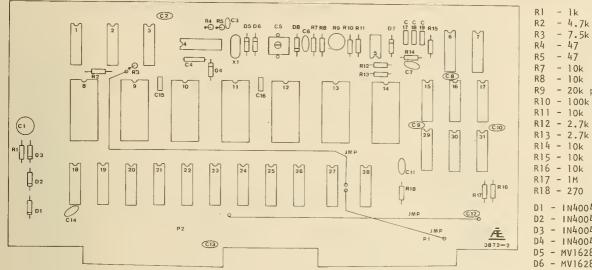

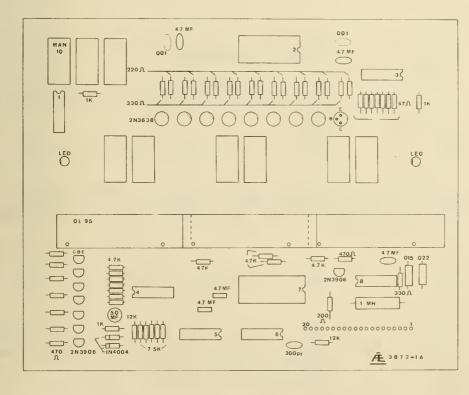

| FIGURE | 15e | CLOCK BOARD COMPONENT LAYOUT                | 27 |  |

| FIGURE | 15f | DISPLAY BOARD COMPONENT LAYOUT              | 27 |  |

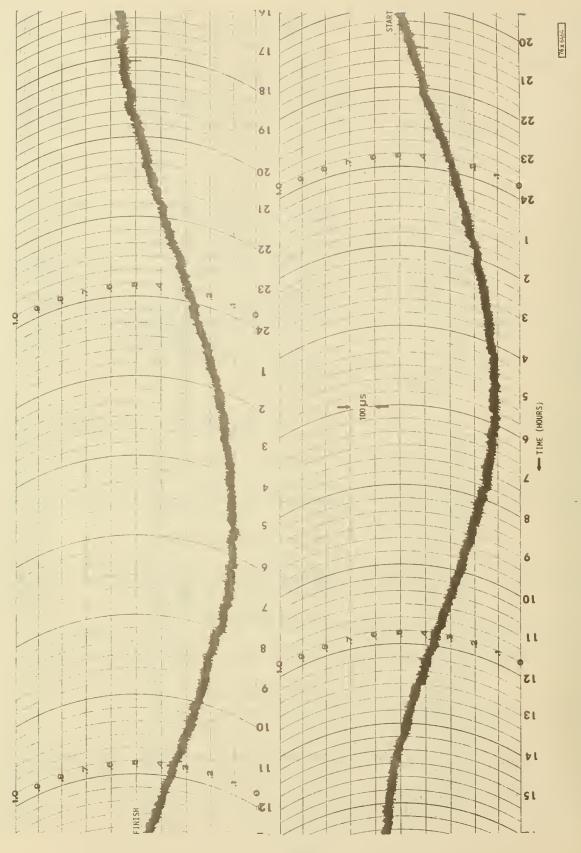

| FIGURE | 16  | UTC(NBS) - SATELLITE CLOCK (MICROPROCESSOR) | 36 |  |

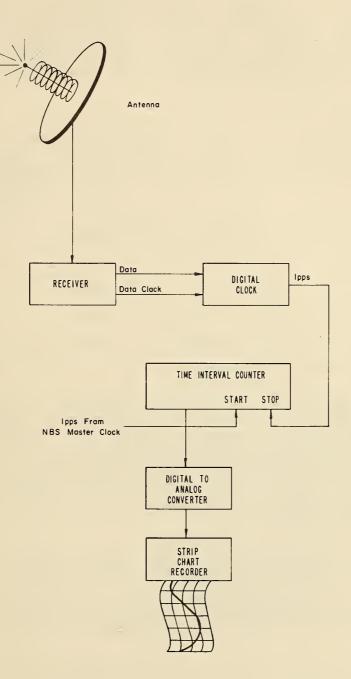

| FIGURE | 17  | DIGITAL CLOCK PERFORMANCE MEASUREMENT SETUP | 37 |  |

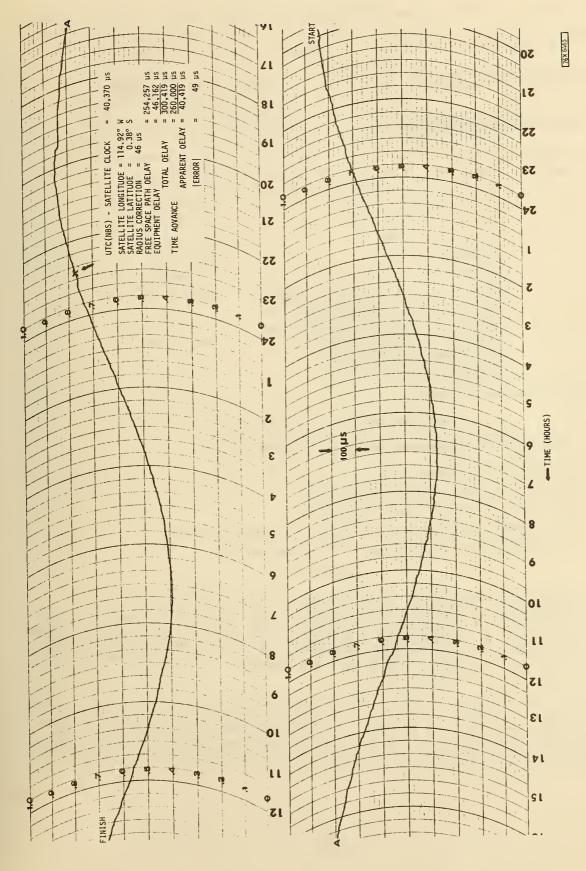

| FIGURE | 18  | UTC(NBS) - SATELLITE CLOCK (TTL)            | 39 |  |

#### A SATELLITE-CONTROLLED DIGITAL CLOCK

J. V. Cateora, D. D. Davis, and D. W. Hanson

A digital clock, resettable and controlled by the time code relayed by NOAA'S SMS/GOES satellites, is discussed. The clock's design is based upon a four-bit microprocessor and uses the redundancy of the data to improve its performance. Satellite position is included in the clock's display for delay corrections to the received time.

A discussion of the generation, distribution, and reception of the time code is also included to aid the explanation of the clock's operation and performance.

Key Words: Clock; microprocessor; satellite; time; time code.

#### 1. INTRODUCTION

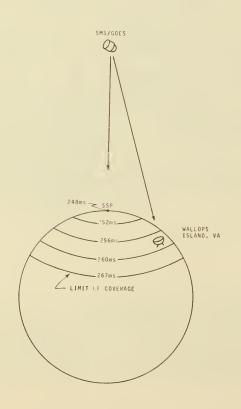

This report describes a digital clock developed by the National Bureau of Standards (NBS) which is controlled by a time code transmitted from the National Oceanic and Atmospheric Administration's (NOAA's) meteorological satellites. The first two satellites launched in this series are known as the Synchronous Meteorological Satellites (SMS) with all others following designated as Geostationary Operational Environmental Satellites (GOES). Long-range plans for these NOAA Satellites call for the positioning of one satellite at approximately 135 degrees West Longitude, another at 75 degrees West Longitude, and a third to be an in-orbit spare. The approximate coverage of these satellites is shown in figure 1. As these satellites deteriorate with age, replacement satellites will be launched. This planned configuration of satellites is expected to be in effect by early 1976. During most of 1975, one satellite was operated from 115 degrees West Longitude, an intermediate point between the two planned locations mentioned.

The time code is used by NOAA in a data collection program where the SMS/ GOES satellites relay data from remote observing platforms such as buoys, automatic weather stations, ships, aircraft, and balloons to a processing facility. Many of these platforms will use the time code to date the data as they are collected or to time order their data transmissions to the satellites. NBS designed and implemented the time code for these satellites. To insure compatibility of the time code with the data collection platforms (DCP), NBS designed a digital clock using a simple low-cost microprocessor. The microprocessor approach to the digital clock design was taken because it offered the lowest cost and provided the flexibility to include or delete functions through software changes rather than hardware redesign.

The microprocessor-based digital clock described in this report has a number of interesting and innovating features. It uses a priori information to improve the effective bit error rate experienced in the satellite link. It also provides the information needed to compute the propagation path delay corrections to the received signals. The total system performance has indicated a 20  $\mu$ s precision with accuracies better than 100  $\mu$ s. The digital clock, once set by the satellite time code, continues to keep time with or without reference to the satellite signal.

The parts cost for the digital clock without the power supply is less than \$200 at the time of this writing. Power input is approximately 7 watts or 160 mA at -10 volts dc and 1 ampere at 5 volts dc.

#### 2. SYSTEM DESCRIPTION

This section describes the time code system including its generation, distribution, format, and reception. The reception of the time code is described assuming the use of a receiver which was developed under a NOAA contract. This receiver is part of the Data Collection Platform Radio Set (DCPRS) designed for

32 2 . 3 A- 3° ELEVATION ANGLE 42. ELEVATION ANGLE ķ 0 5 7 ه • 73 20 ł , •51 •06 4 + 80° #ESI . . . . . # - 80 EAST t -65. -200 ;0 ÷., 22 •0; ٥<u>۶</u> 000 T æ ł 32 2 8 SQ 2 : H1005 HINON 40. 3

FIGURE 1. SMS/GOES COVERAGE

unattended operation over long periods of time, severe environments, and low power consumption. Obvious improvements can be achieved if the receiver is designed as a timing receiver and the above mentioned requirements relaxed. Because no other receiver existed at this time, all references to reception assume the use of this receiver.

# 2.1 FORMAT

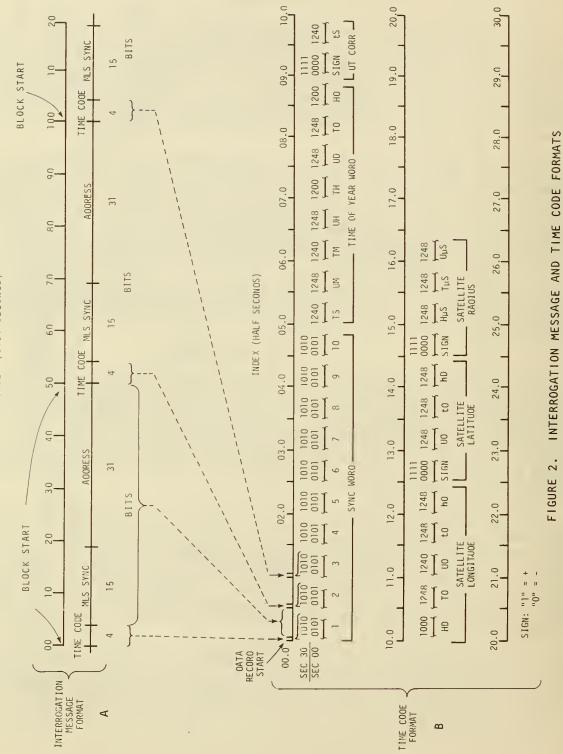

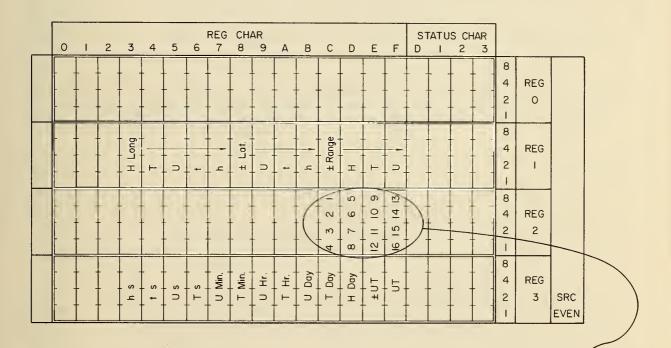

The time information, a digital time code, is multiplexed into an interrogation message format relayed by the SMS/GOES satellites. The interrogation message is used to activate a transfer of a DCP's collected data to NOAA's Wallops Island, Virginia, facilities via the SMS/GOES satellites. The format consists of a 15-bit maximum-length sequence (MLS) for message synchronization immediately followed by 31 bits comprising a (31, 21) binary Bose-Chaudhuri-Hocquenghem (BCH) code. Four additional bits preceed each MLS sequence beginning on the 0.5 second and comprise a binary coded decimal (BCD) character of the time code.

Figure 2a shows the interrogation message format: Four time code bits followed by 15 bits of the message synchronization word and 31 bits of the address word. The pattern is repeated every 0.5 second, at a 100 bits per second rate. The leading edge of the first bit to every time code character defines the UTC 1/2 second mark. Figure 2b is the time code format; four bits are extracted from the interrogation frame every half second for 30 seconds. The first 40 bits is the time code synchronization message consisting of 10 BCD character A's beginning on the UTC minute mark and 10 BCD 5's beginning at the UTC half minute mark.

Following the code synchronization message are 10 BCD characters of the time code followed by 13 BCD characters representing the satellite's current position in geocentric longitude and latitude and its radial departure from a reference orbit expressed in microseconds.

## 2.2 TIME CODE DISTRIBUTION

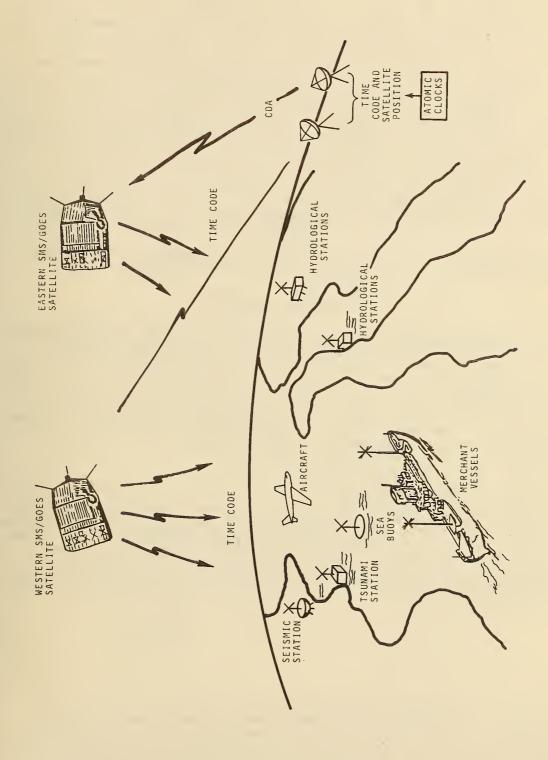

The interrogation message is sent to the SMS/GOES spacecraft at S-Band from Wallops Island, Virginia, and is retransmitted to the earth through a global antenna at approximately 469 MHz. The Manchester coded message phasemodulates the carrier ±60 degrees. The interrogation message is received mainly by data collection platform radio sets (DCPRS) which provide the communication interface with rain and river gauges, ships, buoys, seismograph stations, tide gauges, and tsunami detectors. The DCPRS recovers the data and a data clock from the received interrogation message, the data clock being used for symbol synchronization.

When a DCPRS is addressed, its stored data are transmitted to the SMS for relay to the Wallops Island Command and Data Acquisition Station (CDA). In some cases, such as the monitoring of seismic activities, it is desirable to label the data with the date of occurrence. Attempts to use internal clocks set by infrequent clock carries or by reception of HF or LF radio signals are expensive, labor intensive, and subject to an unacceptable failure rate. The time-of-year code in the interrogation format eliminates these problems and provides the SMS/GOES DCS user with a cheap, reliable, and simple system for data labeling or any other time ordered function required at remote sites or in difficult environments.

Figure 3 illustrates the time code distribution. Derived from atomic clocks located at the CDA in Wallops Island, Virginia, the time code is combined with the current satellite position, multiplexed with the interrogation address and sync word and transmitted to the satellites at S-Band. The satellites transpond the signal back to earth at approximately 469 MHz where it is received by the DCPRS's.

INDEX (0.01 SECONOS)

-4-

#### 2.3 TIME CODE GENERATION

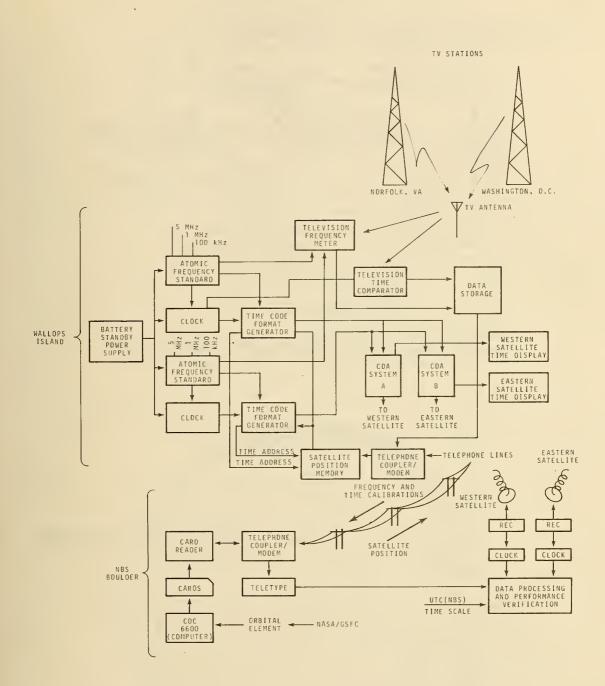

NBS has installed at the CDA at Wallops Island, Virginia, equipment to generate the time code and maintain Coordinated Universal Time (UTC) to within a few microseconds of the master clock at NBS in Boulder, Colorado. Figure 4 is a block diagram of the equipment. There are two atomic frequency standards each driving a clock and format generator making two independent systems. Each system provides the time code and satellite position to DCS racks A and B for multiplexing into the interrogation channels of the two SMS/GOES satellites. All components of each system are backed with rechargeable batteries with sufficient capacity to operate four hours without primary power. Should a failure be experienced in one of the time reference systems the other can be switched in until it is repaired. The frequency of the atomic frequency standards can be compared to the NBS frequency standard in Boulder, Colorado, using a frequency meter operating on television signals. This comparison is accomplished by NBS staff at routine intervals. Satellite position is computed at NBS Boulder from orbital elements issued by NASA's Goddard Space Flight Center and sent to Wallops Island by telephone. An automatic answering system connects the telephone line to a memory bank which stores the positions in the form of a large table valid for 128 hours for the two satellites. The time code format gener-ator addresses the memory with the date (days, hours, and minutes) and fetches the currently valid position for multiplexing into the interrogation message.

The interrogation channels on both satellites are monitored continuously in Boulder. Any failure or drift of the clocks at Wallops Island is automatically noted for appropriate action.

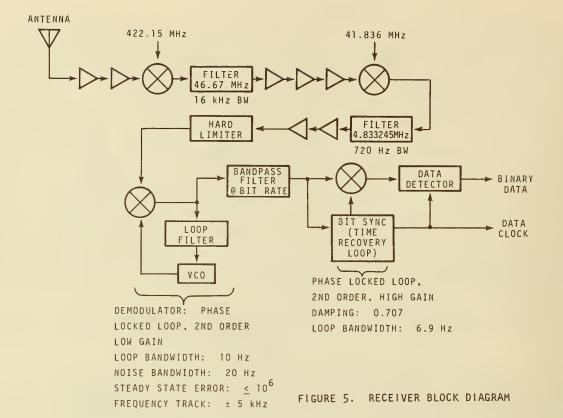

#### 2.4 TIME CODE RECEPTION

The interrogation channel is received by the DCPRS which usually consists of a receiver and transmitter. A block diagram of the receiver is shown in figure 5. The transmitter section of the DCPRS has been left out since it has no bearing on this discussion. The demodulator consists of a phase lock loop with a 10 Hz loop bandwidth and a timing recovery loop to derive the data clock<sup>1</sup> for symbol synchronization. The demodulator provides outputs of data and data clock, the two inputs to the digital clock. The signals from the satellite occupy a bandwidth of 400 Hz, and have a signal level of approximately -139 dBm at the output of an isotropic antenna. A DCPRS receiver and digital clock has been successfully and reliably operated using both linearly and circularly polarized antennas with gains as low as 3 dB.

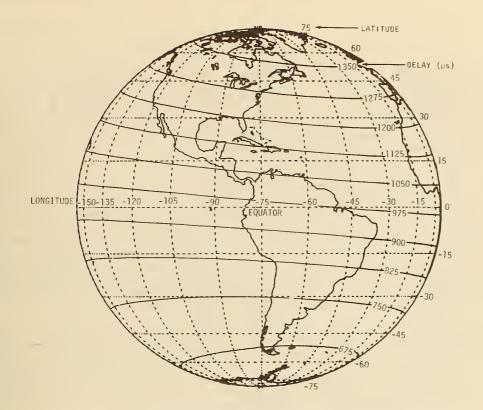

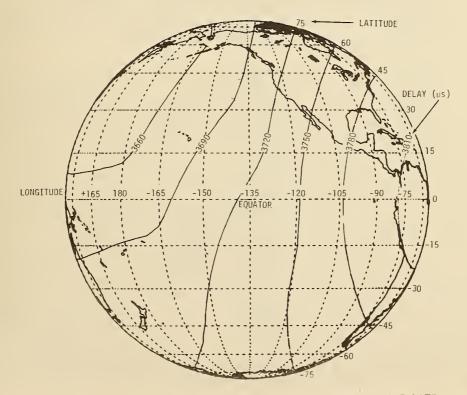

The signal delay from Wallops Island to the earth's surface via the SMS/ GOES satellites is nominally 260,000 µs. This delay is a function of distance from the subsatellite point as shown in figure 6. As a first order correction for delay, the time signals are advanced by 260,000 µs at Wallops Island thereby forcing them to be nearly on time when arriving at the earth's surface. Since the satellite is not in a perfect geostationary orbit, that is, it has some inclination and eccentricity, the delay experienced at any one point has a diurnal component. The magnitude of the diurnal is also position dependent. Typical peak-to-peak values of the diurnals for the Eastern and Western satellites are shown in figures 7a and 7b.

<sup>&</sup>lt;sup>1</sup>The data clock is a sequence of alternating ones and zeros used for symbol synchronization. The RAM clock measures the accumulation of time. The micro-processor clock is the oscillator governing the function of the microprocessor. The digital clock refers to the system (microprocessor, software, I/0, and display) used to maintain time referenced to the time code from the satellite.

FIGURE 4. TIME CODE GENERATION AND CONTROL EQUIPMENT

# FIGURE 6. TIME DELAY THROUGH A GEOSTATIONARY SATELLITE AT 115° WEST LONGITUDE

FIGURE 7a. TYPICAL DELAY DIURNALS FOR THE EASTERN SATELLITE WITH WALLOPS ISLAND TRANSMITTING

FIGURE 7b. TYPICAL DELAY DIURNALS FOR THE WESTERN SATELLITE WITH WALLOPS ISLAND TRANSMITTING

# 3. DIGITAL CLOCK DESCRIPTION

The digital clock was built to interface with NOAA's DCPRS's as they existed in early 1974. A microprocessor design was chosen because of its potential low cost and simplicity. The microprocessor design replaced a previous random logic design amounting to 80 integrated circuit packages. Special features and properties of time messages were used in the microprocessor design. For example, each successive time-code frame differs only by 30 seconds, the length of the frame. Thus the messages have a large degree of redundancy. This fact was used to, in effect, increase the signal-to-noise ratio or lower the bit error rate. The a priori information was used as follows: The microprocessor stores the time-of-year in random access memory (RAM) and continually updates itself by counting the 100 Hz data clock. During every time-code frame received from the satellite the microprocessor compares its RAM time with the new time message. If there is agreement, everything is assumed to be in order. If there is disagreement, the microprocessor will continue to assume that the RAM clock has the correct time, but after four consecutive time frame disagreements the RAM clock is assumed to be in error. The microprocessor will then reset its RAM clock to the next time code message providing the satellite time is being received as evidenced by the presence of the MLS and time code synchronization word. This procedure is referred to as an error bypass capability.

The 100 Hz data clock from the receiver is also subject to noise introducing additional zero crossings that can be interpreted by the microprocessor as 0.01 second increments in time. To minimize the effect of this noise and provide a reliable and continuous 100 Hz to count even without the satellite signal, the microprocessor system crystal oscillator is divided down to 100 Hz and phase locked to the received data clock. The phase locked 100 Hz is then used as the time base for the microprocessor time-of-year (TOY) clock.

The two above mentioned procedures have used the cyclic nature of the data and data clock to improve the performance of the digital clock.

The satellite ephemeris is displayed as received. Consequently, it is susceptible to more error than the TOY. One can only look for consistency in the display from frame to frame. The display is updated at the 00 and 30 seconds. Two successive frames of the same data insure the correct satellite position data is being displayed.

To fully understand the details of the operation of the digital clock, it is well to review the basic tasks it accomplishes. A thorough familiarity with the format of the interrogation channel is important to this understanding. Repeated reference to the software flow chart, figures 8a and 8b would also be helpful. We begin the explanation by assuming that the digital clock has just been connected to the receiver and is receiving the interrogation channel properly. The digital clock has available to it the data and the data clock. It must look at the data clock for a negative going transition to identify when to sense the data and acquire one bit of information. In other words, it acquires symbol synchronization by looking at the data clock. When the proper data clock transition is recognized, it samples the data and stores the sampled bit in memory, an index register of the CPU. In fact, the last 15 bits of data have been stored in index registers. After each bit is received and stored, the last 15 bits stored are examined for the MLS (100010011010111). If the latest stored 15 bits match the sequence stored in program memory, MLS synchronization is declared. The microprocessor now knows the location of the four bits in every interrogation frame constituting a time code BCD character. The microprocessor then loads these four bits every half second into an index register and examines it to determine if it is part of the time code synchronization word, a BCD A or 5 depending on whether the frame is in the first or second half of the minute. When 10 consecutive A's or 5's are found, time code synchronization is declared. The next four bits to be loaded are the tens of seconds (TS) of the time code, then unit minutes (UM), tens of minutes (TM), etc., for the next ll 1/2 seconds or 21 four bit characters finishing with the units of microseconds of the satellite distance. These data are all written into RAM memory.

# FIGURE 8a. SOFTWARE FLOW CHART

FIGURE 8b. SOFTWARE FLOW CHART (CONTINUED)

The microprocessor now counts bits and frames until it arrives at the TS character of the next frame. It does not search for MLS or code sync again since total synchronization may be maintained by simply counting the 100 Hz time base over to the beginning of the next time code frame. On the second pass of a time code frame the microprocessor only compares the newly arrived character of the TOY with the corresponding internal RAM character. Should this comparison fail anywhere in the TOY frame it will be counted as a frame error. If four consecutive frame errors occur, the microprocessor will begin a new search for MLS and time code sync. When successfully achieved the satellite TOY will be written into the RAM clock, resetting the RAM clock. If the microprocessor does not find MLS and time code synchronization it will not disturb the RAM clock. This prevents the RAM clock from being reset when no satellite signal is present.

The RAM clock consists of characters representing days, hours, minutes, seconds, tenths of seconds, and hundredths of seconds. The data clock is derived at Wallops Island from an atomic clock. Each cycle of the data clock represents 1/100 of an atomic second and is counted by the microprocessor to update its RAM clock. The microprocessor has its system oscillator phase locked to the incoming data clock. If the data clock is lost, the internal oscillator will continue to provide the 0.01 s count to keep the RAM clock accurate.

The RAM clock, excluding the 0.1 s and 0.01 s digits, is multiplexed for display by LED's under microprocessor control. The satellite position is loaded into RAM memory every frame as received. At the 00 and 30 second RAM storage of position is transferred to an external shift register and multiplexed to LED's under independent control. Consequently, if the satellite signal is lost, the satellite position will also disappear from the display.

The program for controlling the microprocessor occupies two 8 bit x 256 programmable Read Only Memories (pROMs), that is, 512 eight-bit bytes. The actual program requires about 460 bytes.

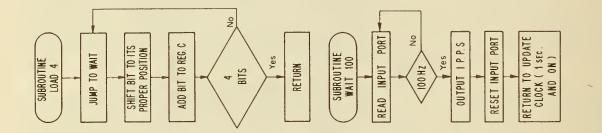

The program consists of a main program called START of about 210 bytes, subroutine WAIT of about 175 bytes, subroutine SPOS of about 25 bytes, subroutine LOAD4 of about 30 bytes and subroutine WAIT100 of about 20 bytes.

The main program START first establishes "MLS" sync by comparing the latest 15 bits received with the 15 bits of the known MLS pattern stored in pROM. This locates the correct starting point in the bit stream to start looking for BCD characters, that is, identifies the BCD characters of the time code.

Next, START looks for 10 "A" or 10 "5" characters in order to establish "CODE" or frame sync. Every 30 seconds the code contains either ten 1010<sub>2</sub> (BCD character "A") patterns starting at 00 s or ten 0101<sub>2</sub> (BCD "5") patterns starting at 30 s. Once "CODE" sync has been established the next BCD character received will be tens of seconds. Establishment of "MLS" and "CODE" sync is indicated by lights on the digital clock's display board.

When the digital clock is first turned on, and after both sync words are found, the received TOY and satellite position are written into RAM by START. In subsequent passes of the received code only position information is written into RAM unless discrepancies are found between the received TOY and the TOY stored in RAM.

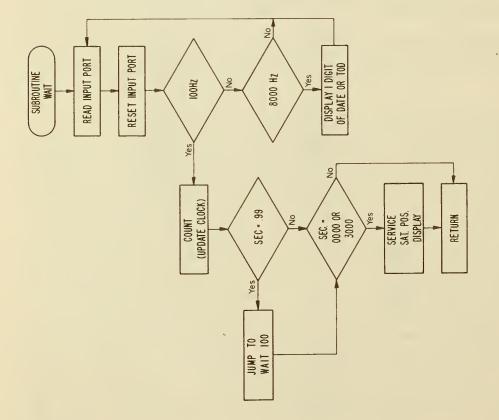

Subroutine WAIT is called by START to find data bits as they appear at the input port. When one is found, WAIT increments the RAM clock by 0.01 s. WAIT also contains the coding for displaying the TOY. When an 8000 Hz transition is sensed at the input port, WAIT displays one digit of the TOY.

Subroutine SPOS is called by WAIT after the RAM clock has been updated and the time is 0.00 or 30.00 s. When called, SPOS loads the satellite position characters from RAM into the position display hardware which otherwise runs independently of the microprocessor. LOAD4 is called by main program START to reconstruct a BCD character from four data bits. LOAD4 calls WAIT to locate the necessary four bits and stores the built-up BCD character in an index register reserved for this purpose.

WAIT100 is a subroutine of 18 bytes whose only purpose is to keep the clock's 1 pps as nearly on time as possible. It is called by WAIT when time is .99 s and waits only for the next .01 s pulse to occur, the instant when the 1 pps should be output, and ignores any 8000 Hz pulses for display. As soon as the .01 s pulse is sensed by WAIT100 it outputs the 1 pps. If a scheme such as WAIT100 were not used, the microprocessor could sense an 8000 Hz pulse and be occupied by performing its display function when the .01 s pulse, signaling a change in unit seconds, occurs and could not output the 1 pps until many program steps later. The use of WAIT100 keeps the 1 pps on time within about 30 µs. Without WAIT100 the 1 pps occurs randomly within 400 µs of being on time.

A complete listing of the program appears on pages 28 through 35. Figures 9a and 9b show the microprocessor's register maps. Figure 10 shows a logical block diagram of the program.

#### 3.1 DIGITAL CLOCK CIRCUITRY

The 4004 Central Processing Unit (CPU), 4702A programmable Read Only Memory (pROM), 4002 Random Access Memory (RAM), 4008 Address Latch and 4009 Input/Output Multiplexers, 4201 Clock Generator, and TTL random logic packages form the microprocessor digital clock (see figure 10). The 4000 family of MOS microprocessor chips was chosen primarily because they are low cost four-bit devices and well suited for handling four-bit characters. The 4004 CPU was selected because of its low cost, easy availability and its proven history of use.

The microprocessor has one four-line input port, to which the received satellite signals are connected and eight four-line output ports which are assigned as follows:

| Output Port | Function                               |

|-------------|----------------------------------------|

| 0           | Input port reset                       |

| 1           | Satellite position BCD character       |

| 2           | Time-of-Year display strobe            |

| 3           | Time-of-Year BCD character             |

| 4           | "MLS" and "CODE" sync indicator lights |

| 5           | l pulse per second voltage pulse       |

| 6           | spare                                  |

| 7           | spare                                  |

One RAM output Port is also used to disable the satellite position display clock while the satellite position display is being serviced.

The hardware is divided between two circuit boards. One board contains the microprocessor along with its input and output circuitry. The other board contains seven-segment Light Emitting Diodes (LED's) and associated TTL random logic to display the 22 time-of-year and satellite position characters. The 9 time-of-year LED's are multiplexed one digit at a time at approximately an 8000 Hz rate under microprocessor control. The 13 satellite position characters are stored in a hex-32 shift register and multiplexed by a free-running hardware clock at about a 60 kHz rate. The satellite position display is updated by the microprocessor every half minute at 00 and 30 seconds. This combination of display methods was chosen to avoid LED flicker associated with multiplexing 22 characters under the control of a processor with many other sequential tasks.

| EVEN | B 4 2 I                              | REG.<br>PAIR | 8 4 2 1                                            | qqo |

|------|--------------------------------------|--------------|----------------------------------------------------|-----|

| E    | 31 and 46 Counter                    | P7           | 31 and 46 Counter                                  | F   |

| с    | Reconstruct BCD Char                 | P6           | IO A/S Counter, Write Flag,<br>Frome Error Counter | D   |

| Δ    | RAM Chor Write Select,<br>37 Counter | P5           | RAM Char Write Select,<br>37 Counter               | 8   |

| в    | Save Data in "2" Bit                 | P4           | TOY Char. Error                                    | 9   |

| 6    | TOY Output Port Select               | Р3           | TOY Choracter                                      | 7   |

| 4    | Multiplex Port Setect                | P2           | Multiplex Counter                                  | 5   |

| 2    | General Use                          | PI           | Generol Use                                        | 3   |

| 0    | Generol Use                          | PO           | General Use                                        | I   |

FIGURE 9a. RAM MAP

FIGURE 95. REGISTER MAP

MLS SYNC PATTERN /

FIGURE 10. DIGITAL CLOCK BLOCK DIAGRAM

The Manchester encoded TOY and position data phase modulates the 469 MHz carrier ±60 degrees. Fron this are derived a 100 Hz data clock and serial binary data. The microprocessor's basic clock is 4.096 MHz which is frequency divided by 8x2x16x16x10 (=40960) to provide a frequency of 100 Hz. This 100 Hz signal is phase compared with the 100 Hz data clock and a voltage proportional to the phase difference is fed back to a pair of varactor diodes in parallel with the 4.096 MHz microprocessor clock crystal to phase lock the 4.096 MHz clock to the recovered data clock. Figure 11 is a block diagram of the phase lock loop and microprocessor input circuitry. The phase lock loop and input port arrangement is important because if the satellite signal is lost for any reason or for any length of time, the 100 and 8000 Hz signals will still be present as they are now being derived from the crystal controlled microprocessor will continue to update its RAM clock with the accuracy of the microprocessor's system clock. The satellite position information is not updated under these conditions and will be lost.

The microprocessor's one input port is connected as shown in figure 12. The 100 Hz satellite data clock is fed to the input port's "1" line through a 7474 latch. The "2" line is fed the 8000 Hz, through a latch also, derived from the frequency divider chain operating on the 4.096 MHz microprocessor clock. The input port "4" line is not used and the "8" line is connected to the received 100 Hz serial binary data.

The microprocessor, through software program control, samples the input port "1" line connected to the 100 Hz satellite data clock. If a 100 Hz transition is sensed the program updates an internal BCD clock stored in RAM by 0.01 s. The RAM clock is in the form of 11 4 bit BCD characters representing DDD, HH, MM, SS, ts, hs, that is, Day, Day, Day, Hour, Hour etc., down to .1s, .01 s. The .01 s update of the RAM clock and the appropriate carries ripple up to the tens of hours BCD character. The characters representing days are set by actually reading the received code into RAM.

The sensing of a 100 Hz transition at the input port "1" line also triggers the storage of data present at the "8" line as one bit of the four bits of a BCD charater. Four 100 Hz data clock transitions, sensed at the appropriate time, will therefore cause the RAM clock to be updated and one BCD character representing TOY or satellite position to be saved.

After looking for a 100 Hz transition, and whether or not one is found, the microprocessor next attempts to sense an 8000 Hz transition at the input port's "2" line. If an 8000 Hz transition is sensed, one digit of the date will be displayed on a 7-segment LED display character. If no 8000 Hz transition is sensed the microprocessor loops back and continues attempting to find either a 100 or an 8000 Hz transition. Basically then, the microprocessor spends its time looking for one of two conditions, a 100 or an 8000 Hz transition and then either updates its RAM clock or displays a character. Although the RAM clock contains BCD characters representing .01 and .1 s they are not displayed.

The microprocessor continuously compares the received TOY characters with the TOY characters stored in RAM. If four consecutive comparison frame errors occur the next received TOY character is rewritten into RAM and will be displayed. Four consecutive frame errors were chosen as the criterion for resetting the RAM clock to lessen the possibility of a noisy or marginal received signal causing an unintentional time reset. Experience with the digital clock under noisy signal conditions has shown this to be a good choice, but not necessarily the optimum strategy for all environments.

Display of TOY is accomplished by a 7-segment decoder on the display board which receives the BCD data and time-of-day characters from output port #3 and drives the display segments. The associated multiplex count from output port #2 is decoded by a 1 to 16 multiplexer with 2N3638 transistors driving the LED strobe inputs.

FIGURE 11. MICROPROCESSOR CLOCK PHASE LOCKED TO DATA CLOCK

.

-18-

76 X 5248

FIGURE 12. DIGITAL CLOCK SCHEMATIC

Figure 13 shows the wiring diagram of the display board. Figure 14 shows the clock, display, and a "delay slide rule." This slide rule is used to compute the delays from Wallops Island, VA, to the user's location via the satellite using the satellite position data contained in the time code format. See references 1-3 for more detail on the design and use of this slide rule. Figures 15a - 15f provide board layout and component location information.

The satellite position display consists of a hex-32 shift register which stores the 13 satellite position characters plus three blank characters twice over. The 32 characters are then clocked out of the shift register in sequence by a hardware clock on the display board that runs independently of the microprocessor. The output of the shift register goes into a 7-segment decoder and the 13 position characters are displayed. The position display runs by itself and receives attention from the microprocessor only at 00 and 30 s when the hex-32 shift register is reloaded. Presently the satellite position changes only each half hour and the shift register receives the same satellite position information 60 consecutive times. However, in the future it may become desirable to update the position information at a higher rate.

#### 3.2 SOFTWARE LISTING

Pages 28-35 show a listing of the digital clock's software. The program was punched into standard 80 column data processing cards only as a convenient method of documentation. The format of the listing is as follows:

Column

| 1     | Hexadecimal page or ROM chip number                                |  |  |

|-------|--------------------------------------------------------------------|--|--|

| 2     | Blank                                                              |  |  |

| 3-4   | Hexadecimal instruction address within ROM chip                    |  |  |

| 5     | Blank                                                              |  |  |

| 6-7   | Hexadecimal microprocessor instruction                             |  |  |

| 8     | Blank                                                              |  |  |

| 9-18  | 1 to 10 character label                                            |  |  |

| 19    | Blank                                                              |  |  |

| 20-22 | 1 to 3 character operation mnemonic                                |  |  |

| 23    | Blank                                                              |  |  |

| 24-33 | 1 to 10 character operand (data, register, condition, label, etc.) |  |  |

| 34-37 | Blank                                                              |  |  |

| 38-80 | Comments                                                           |  |  |

Some 4004 instructions require two bytes in which case the second line of the instructions may contain data or a jump address.

# 3.3 DIGITAL CLOCK PERFORMANCE

The digital clock has been in operation for many months in a number of locations but at this time only NBS at Boulder has explored its full potential. The chart shown in figure 16 illustrates the long-term performance of the digital clock. The chart represents the time difference between the NBS master clock and a 1 pps from the digital clock and was obtained using the equipment shown in figure 17. The chart shows a peak-to-peak noise of less than 40  $\mu$ s. The chart also shows the delay diurnal with a peak-to-peak value of approximately 450  $\mu$ s. This chart was made during November 1975, when the satellite's inclination was approximately 1/2 degree.

The accuracy of the digital clock is dependent upon the correct assignment of path and equipment delays. The receiver and digital clock delays were studied

76× 6251

FIGURE 15c. CLOCK BOARD (FRONT)

FIGURE 15e. CLOCK BOARD COMPONENT LAYOUT

FIGURE 15F. DISPLAY BOARD COMPONENT LAYOUT

| $R_{3} = 7.5k$ $R_{4} = 47$ $R_{5} = 47$ $R_{7} = 10k$ $R_{9} = 20k \text{ pot}$ $R_{10} = 100k$ $R_{11} = 10k$ $R_{12} = 2.7k$ $R_{13} = 2.7k$ $R_{13} = 2.7k$ $R_{14} = 10k$ $R_{15} = 10k$ $R_{16} = 10k$ $R_{17} = 1M$                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| R18 - 270<br>D1 - IN4004<br>D2 - IN4004<br>D3 - IN4004<br>D4 - IN4004<br>D5 - MV1628<br>D6 - MV1628<br>D7 - IN4004<br>D8 - IN4004<br>X1 - 4.096 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| C1 - 47 $\mu$ f 16V<br>C2 - 4.7 $\mu$ f tant.<br>C3 - 22 pf silver<br>C4 - 1 $\mu$ f<br>C5 - 5.5-18 $\mu$ f<br>C6 - 0.1 $\mu$ f 10V<br>C7 - 4.7 $\mu$ f tant.<br>C8 - 4.7 $\mu$ f tant.<br>C9001 $\mu$ f<br>C10 - 4.7 $\mu$ f tant.<br>C11 - 0.1 $\mu$ f 10V<br>C12 - 4.7 $\mu$ f tant.<br>C13 - 4.7 $\mu$ f tant.<br>C14 - 4.7 $\mu$ f tant.<br>C15 - 4.7 $\mu$ f tant.<br>C15 - 4.7 $\mu$ f tant.<br>C16 - 4.7 $\mu$ f tant.<br>C16 - 4.7 $\mu$ f tant.<br>C17 - 4.7 $\mu$ f tant.<br>C18 - 4.7 $\mu$ f tant.<br>C19 - 4.7 $\mu$ f tant. | mica |

| 40 <sup>5</sup> 014<br>10<br>10<br>10                                                                                                                  | TION .                                                   |                                           |                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P P P P                                                                                                                                                | MNEMO                                                    | DNIC                                      | COMMENTS                                                                                                                                                      |

| 0 01<br>0 02 F0 S<br>0 03 22<br>0 04 00<br>0 05 24<br>0 06 00<br>0 07 26                                                                               | FART CLE<br>Fim<br>0<br>Fim<br>9<br>Fir                  | 0<br>P2<br>0<br>P3                        | NBS SATELLITE CONTROLLED DIGITAL GLOCK,<br>TIME OF YEAR AND SATELLITE POSITION<br>IN THIS VERSION THE 1 HZ OUTPUT IS<br>CONTROLLED TO WITHIN 30 MICRO SECONDS |

| 0 08 00<br>0 09 28<br>0 0A 00<br>0 0B 2A<br>0 0C 00<br>0 00 2C<br>0 0E 00<br>0 0F 2E<br>0 10 00<br>0 11 20                                             | 0<br>FIM<br>0<br>FIM<br>0<br>FIM<br>0<br>FIM<br>0<br>FIM | 0<br>P5<br>9<br>P6<br>0<br><b>P7</b><br>0 | SET INDEX REGISTERS 2 THRU F = 0                                                                                                                              |

| 0 12 40<br>0 13 21<br>0 14 DF<br>0 15 62<br>0 16 40<br>0 17 20<br>0 18<br>0 19<br>0 1A<br>0 18<br>0 19<br>0 1A<br>0 1B<br>0 1C<br>0 1D<br>0 1E<br>0 1F | 4<br>SRC<br>LDM<br>WRR<br>JUN                            | 0<br>P û<br>F                             | TURN OFF MLS AND CODE SYNC LIGHTS                                                                                                                             |

| 0 20<br>0 21 51 AM<br>J 22 00<br>0 23 22                                                                                                               | NOTHER JMS                                               | TIAW                                      | GO TO WAIT AND STAY UNTIL A 100 OF AN 8000<br>HZ TRANSITION OCCURS                                                                                            |

| 0 24 2C<br>0 25 F0<br>0 26 23 SE<br>0 27 E9                                                                                                            | 2<br>CLB                                                 | С                                         | SELECT RAM D/REG 2/CHARS C THRU F WHERE<br>15 BIT MLS SYNC PATTERN WILL BE STORED AS<br>THE BITS ARE RECEIVED                                                 |

| 0 28 F6<br>0 29 E0<br>0 2A 73                                                                                                                          | RAR<br>WRM<br>ISZ                                        |                                           | SHIFT RAM CHARS C THRU F (MLS) RIGHT ONE<br>BIT TO MAKE ROOM FOP A NEWLY RECEIVED BIT                                                                         |

| 0 20 09 #                                                                                                                                              | THIS DATA IS<br>ADDRESSES ARE                            | THE SAME AS<br>ERN AND THIS               | PATTERN AND IS STORED HERE BECAUSE THESE ROM<br>THE RAM CHARACTER ADDRESSES OF THE RECEIVED<br>SIMPLIFIES THEIR COMPARISON LATER AT ADD. 046                  |

| 0 32 E9<br>0 33 F6<br>0 34 F1<br>0 35 F5<br>0 36 E0<br>0 37 F0                                                                                         | RDM<br>RAR<br>CLC<br>RAL<br>WRM<br>CLB                   |                                           | CHAR F STILL SELECTED IN RAM SETS 16TH<br>BIT OF 4 MLS RECEIVED CHARACTERS = 0                                                                                |

| 0 38 A8<br>0 39<br>0 3A<br>0 38 F5                                                                                                                     | LD<br>RAL                                                | Rð                                        | REG 8 CONTAINS A DATA BIT IN ITS 2 POSITION<br>THIS WAS STORED IN REG 8 BY WAIT WHEN A 100<br>HZ TRANSITION WAS SENSED AND A JUMP TO<br>COUNT OCCURRED        |

| 0 3C F5<br>0 3D 20<br>0 3E 2C<br>0 3F 21                                                                                                               | RAL<br>FIM<br>2<br>SRC                                   | С                                         | SHIFT DATA BACK TO THE 8 POSITION READY TO<br>ADD TO RAM<br>SELECT RAM D/REG 2/CHAR C                                                                         |

AON ADU NEWEST BIT RECEIVED TO 8 POSITION OF 0 40 EB WRM CHARACTER C, I.E. STORE IT IN RAM 0 41 E0 SRC PO 0 42 21 OK PUT CONTENTS OF ADDRESS OC INTO P1 FIN P1 0 43 32 0 44 FC CLE PUT CONTENTS OF R3 (= E) INTO ACCUMULATOR 0 45 A3 LO R3 SBM SUBTRACT RAM CHAR & FROM ACCUMULATOR 0 46 £8 JCN A1 - ANOTHER ISZ R1 - OK FIM PC 0 47 10 0 48 21 0 49 71 IF CHAR C = (ACCUMULATOR) INCREMENT R1 AND JUMP TO OK TO TEST NEXT RAM CHARACTER AGAINST DATA 0 4A 42 0 48 20 IF THIS POINT IS REACHED MLS MATCHES --4 0 SRC PC 0 46 40 TURN ON MES LIGHT 0 40 21 LDM E 0 4E OE WER 0 4F E2 0 50 2E FIM P7 SET UP P7 TO COUNT 31 CALLS TO WAIT 1 E 0 51 1E JMS -- WAIT ISZ RE 0 52 51 AGAIN MAKE 31 CALLS TO WAIT TO SKIP 31 BITS 0 53 00 BETWEEN MES AND GUD CHARACTER 0 54 72 0 55 52 - AGAIN ISZ RE 0 56 7F 0 57 52 - AGAIN LDM 6 XCH RO INITIALIZE 10 A/5 COUNTER 0 58 D6 0 59 BD JMS -- LOAD4 JUN -CALL LOAD4 TO MAKE 4 CALLS TO WAIT TO GET ONE BCO CHARACTER 0 5A 51 9 58 E0 ù 5C 40 0 50 68 - CODE SYNC FIM P7 0 SE 2E MORE SET UP TO MAKE 46 CALLS TO WAIT 0 5F 20 2 D 0 60 51 MORE+2 JMS -- WAIT 0 61 00 ISZ E SKIP 46 BITS BETWEEN BOD CHARACTERS -- ONCE - MORE+2 MLS SYNC IS ESTABLISHED FRAME SYNC AND CODE 0 62 7E ISZ E 0 63 60 0 64 7F PECEIVING IS DONE BY SKIPPING BITS BETWEEN ISZ F - MORE+2 JMS -BCD CHARACTERS ũ 65 60 GIT NEXT ECD CHARACTER 0 66 51 0 67 E0 - LOAD4 0 68 F0 CODE SYNC CLB SET UP TEST FOR A OR 5 CHARACTER, THAT IS Look for frame sync FIM PC 0 69 20 A 5 0 6A A5 LD PD LOAD THE CHARACTER A INTO THE ACCUMULATOR 0 6B A0 SUB RC 0 60 90 JCN AC 0 60 14 JUMP TO CONTINUE IF CONTENTS OF PC = - CONTINUE CHARACTER A 0 6E 78 0 6F FC CLE 0 70 A1 LO R1 LOAD CHAPACTER 5 INTO ACCUMULATOR SUE RU 0 71 90 JCN AD JUMP TO CUNTINUE IF CONTENTS OF RC = 5 0 72 14 - CONTINUE 0 73 78 0 74 06 LOM 6 XCH RU RESET THE 10 A/5 COUNTER TO 6, I.E. GET 0 75 ED JUN -READY TO COUNT 18 AS OR 10 55 AND GO BACK 8 76 40 TO START 0 77 02 - START 0 78 70 CONTINUE ISZ RU GO TO MORE IF NOT 10 AS OR 10 55 FOUND 0 79 5E - MORE FIM PC CODE SYNC IS ESTABLISHED IF THIS POINT IS REACHED J 7A 20 REACHED TURN ON CODE SYNC LIGHT (KEEP MLS LIGHT ON ALSO) 0 78 40 4 0 SRC P9 0 7C 21 ALSO) LOH C 0 70 OC 0 7E E2 WRR 0 7F

0 80 00 LUM 0 RO IS NOW USED FOR THE WRITE TIME OF YEAR 0 81 80 XCH HU (TOY) FLAG --- SET IT = 0 FIM P1 3 82 22 0 83 33 3 3 SELECT TOY .01 SECOND CHARACTER IN RAM SPC P1 0 84 23 0 85 04 LON 4 0 86 EC WRM WFITE HUNUREDTH SECOND CHARACTER = 4 IN RAM 0 P7 63 INC R3 3 88 23 SKC P1 0 49 05 LOP 5 0 8A E6 WRE WPITE JENTH SECOND CHARACTER = 5 IN PAM 3 88 63 INC FS 0 80 23 SRC P1 C 8D D4 EDM 4 D PE EC WEN WHITE UNIT SECOND CHARACTER = 4 IN RAM 6 8F 46 - NUL 0 90 AD - J/C 0 91 0 92 FINDING 10 AS OR 10 55 CONSTITUTES CODE 0 93 SYNC, THAT IS LOCATES START OF TOY COLL --2 94 CODE SYNC OCCURS AT 4.54 AND 34.54 SECOND 0 95 THEREFORE SET UNIT SECOND = 40 06 TINTHS SECOND = 5 0 97 HUNGRIDTHS SECOND = 40 98 0 99 0 9A 9 9B 0 90 1 90 9 9E C 9F 0 AO 2A IICO FIM PS SET UP TO SELECT RAY DIREG SICHARS 6 THRU F 3 0 0 A1 36 TIME OF YEAR (TOY) C A2 DC LUM C SET PS, TOY CHARACTER ERROR FLAG = 0 0 A3 80 XCH PA A A4 2E NEXTIO FIM P7 SET JP 46 BIT COUNTER 6 A5 26 2 D JNS -0 A6 51 AGAIN10 0 A7 05 -WAIT 0 A8 7E SKIP 46 BITS DETWEEN BOD CHARACTERS ISZ RE 0 A9 AE AGAIN10 -ISZ OF U AA 7F O AB A6 AGAIN10 -0 AC 51 GET NEXT TIME OF YEAR CHARACTER JMS -0 AD EO LOAU4 -O AE AD LD RD TEST WRITE FLAG (R0) -- IF NOT = 0 JUMP TO 0 AF 10 JCN A1 0 80 06 -COMPARE COMPARE -- ELSE WRITE TOY INTO RAM 0 01 20 SRC P5 0 92 AC LU RU WFILE TOY CHARACTERS INTO RAM 0/REG 3/ CHARACTERS C THRU F 0 83 EG WEN ISZ RB INCREMENT AND TEST FOR 10 TOY CHARACTERS 0 84 76 PETURN REAU AND WRITTEN INTO RAM OR COMPARED 0 65 A4 -NEXT10 0 86 A9 LD R9 0 87 10 TEST R9 (TOY CHAR ERROR FLAG) TO SEL IF AT JCN A1 LEAST ONE TOY CHARACTER ERROR OCCURRED 0 88 80 - INCRENENT 0 89 00 LUM C DURING THE LAST FRAME. IF IT OID -- GO TO 0 8A 8C XCH PC INDREMENT TO INCREMENT FRAME ERROR COUNTER 3 BB 40 ELSE RESET FRAME ERROR COUNTER TO BE ABLE - MUL 0 90 08 - ISAT TO COUNT 4 CONSECUTIVE FRAME ERRORS 0 BD 6D INCREMENT INC RD 0 BE AD LD RD INCREMENT TOY CHAR ERROR COUNTER 0 8F

0 CO 14 JEN AE 0 C1 02 - START IF RD = 0 THEN 4 CONSECUTIVE FRAME ERRORS 0 C2 40 JUN -OCCULRED -- GO BACK TO START -- ELSE GO ON 0 C3 D8 - ISAT TO RECEIVE SATELLITE POSITION INFORMATION 1 C4 0 C5 0 C6 28 COMPARE SRC P5 ARRIVE HERE IF WRITE FLAG (RD) IS NOT = 0 0 C7 AC LD RC TO COMPARE TOY CHARACTER IN RC WITH TOY 0 C8 E8 SBM CHARACTER IN RAM 0 C9 F1 CLC 0 CA 14 JCN AU C CB B4 - RETURN GO TO RETURN IF TOD CHARACTER IS THE SAME 0 CC D1 LOM 1 CD 89 2 XCH R9 SET 99, CHAR ERROR FLAG =1 AND GO TO RETURN 3 CE 40 IF TOY CHARACTER IS NOT THE SAME JUN -3 CF 84 - RETURN 0 00 0 D1 0 02 0 03 3 04 0 05 0 06 0 07 0 D8 2A ISAT FIM P5 INITIALIZE 13 WORD COUNT AND SELECT OF 0 09 13 1 3 RAM D/REG 1/CHARACTERS 3 THRU F SATELLITE 0 DA 2E NEXT13 FIN P7 POSITION 0 08 20 2 D INITIATE 46 BIT COUNTER 0 DC 51 AGAIN13 JMS -0 00 00 - WAIT 0 DE 7E ISZ Re SKIP 46 61TS BETWEEN SAT. POS. CHARACTERS 0 DF DC AGAIN13 -0 E0 7F ISZ RF 0 E1 DC ----AGAIN13 0 E2 51 JMS -GET NEXT SATELLITE POSITION CHARACTER 0 E3 E0 LOAD4 -0 E4 26 SPC P5 0 E5 AC LO RC WRITE SAT. POS. CHAR. INTO RAM 0 E6 E0 WRM 9 F7 78 INCREMENT SAT. POS. CHAR. ADDRESS IN RAM ISZ RH 0 68 DA - NEXT13 0 E9 40 JUN -WHEN THIS POINT IS REACHED 13 SAT. POS. 0 EA F0 0 F J CHARACTERS HAVE BEEN RECEIVED AND WRITTEN -6 EB INTO RAM 0 EC 0 ED 0 EE 0 EF 0 F0 2A FIN P5 INITIALIZE FOR 37 FRAME COUNT J F1 BD R n 0 F2 2F NEXT37 FIM P7 INITIALIZE FOR 50 BIT COUNT 9 F3 EC Ε С 0 F4 51 AGAINSC JMS -0 F5 0C WAIT -0 F6 7F ISZ RE 0 F7 F4 SKIP 50 BITS IN A FRAME -AGAIN50 0 F8 7F ISZ RF 0 F9 F4 -AGAIN50 0 FA 7A ISZ RA 0 F8 F2 -NEXT37 SKIP 37 FRAMES BETWEEN END OF SATELLITE 0 FC 78 ISZ RR POSITION AND START OF TIME OF YEAR 0 FD F2 - NIXT37 0 FE 40 0 FF A0 JUN -GU BACK TO RECEIVE TIME OF YEAR AGAIN ITOD -

-31-

.

1 CO FO WAIT GLB CLEAR ACCUMULATOR AND CARRY 1 01 22 FIM P1 1 02 00 0 0 SELECT IN/OUT PORT NO. 0 FOR INPUT AND 1 03 23 SRC P1 RESET 1 34 EA RDR 1 05 F6 RAR 1 06 12 JGN G1 IF 198 HZ IS PRESENT JUMP TO COUNT 1 07 30 - COUNT 1 08 1 89 F6 RAP ROTATE 3300 HZ INTO CARRY POSITION JCN C1 1 0A 12 - DISPLAY 1 08 0F IF 8000 HZ IS PRESENT JUMP TO DISPLAY 1 GC 41 JUN -1 CD OC - WAIT CONTINUE LOOKING FOR 100 OR 8030 HZ 1 GE TRANSITION 1 OF D2 DISPLAY LOM 2 RESET 8600 HZ 1 10 E2 WRF LO R7 1 11 A7 1 12 10 JCN A1 TEST IF RZ, RAM TOY CHAR ADDRESS IS NOT = 0 1 13 18 - NZERO 1 14 26 FIM P3 1 15 35 3 5 IF R7 = 0 RESET RAM CHIP/REG/CHAR SELECT FIM P2 AND FESET MUX STROBE AND MUX OUTPUT PORT 1 16 24 1 17 25 2 5 FOR TIME OF YEAR CHARACTER SRC P3 1 18 27 NZERO 1 19 00 LDM D WRITE BLANK DATA (BLANK = NOT G = F) WRE 1 1A E2 1 18 25 SRC P2 1 1C A5 LO R5 WFITE OUT TIME OF YEAR STROBE 1 10 F4 C MA 1 15 E2 WRR SRC P3 1 1F 27 1 20 E9 RDN CMA 1 21 F4 WHITE OUT TIME OF YEAR CHARACTER 1 22 E? WRR 1 23 67 INC P7 INDREMENT RAM TOY CHARACTER AOORESS 1 24 65 INC R5 INCREMENT STROBE 1 25 41 JUN -1 26 00 - WAIT GO BACK AND WAIT FOR ANOTHER 100 OR 8000 HZ 1 27 TRANSITION 1 28 1 29 1 2A 1 2B B6 COUNT XCH R3 SAVE INPUT PORT NO. C IN R8 TEMPORARILY LDM 1 WPITE OUT 1 TO RESET 130 HZ LATCH ON 1 20 01 WRA OUTPUT PORT NO. 6 1 20 E2 1 2E 22 FIM P1 2 0 SRC P1 POINT TOY STROBE AT DISPLAY OIGIT .NO. 0 1 2F 20 1 30 23 WHEN 8000 HZ OCCURS TO MINIHIZE DISPLAY FLICKER -- PREVENTS A DIGIT FROM STAYING ON 1 31 DF LDM F 1 32 E2 WRP WHILE CLOCK IS BEING UPDATED XCH R8 1 33 B8 RESTORE INPUT PORT NO.9 DATA TO ACCUMULATOR 1 34 F1 CLC CLEAR 100 HZ FROM CARRY 1 35 F6 RAR GLEAR 8000 HZ (IF PRESENT) 1 36 F1 CLC 1 37 88 SAVE OATA IN R8 2 BIT POSITION XCH R8 1 38 22 SELECT RAM DIREG 3/CHAR 3 THRU F, THAT IS FIM P1 1 39 33 3 START WITH TOY .01 SECOND CHARACTER 3 SRC P1 1 3A 23 1 3B E9 RDM READ .01 SECONO CHARACTER INTO ACCUMULATOR 1 36 F? IAC INCREMENT RAM CLOCK BY .31 SECOND IF CY=1 OR ACCUMULATOR IS GREATER THAN 9 1 3D F8 DAA 1 3E EC WRM SET ACCUMULATOR = ACCUMULATOR + 6 WRITE .01 S BACK INTO SAME RAM LOCATION 1 3F 63 INC R3

-32-

| 1 40 23<br>1 41 F7<br>1 42 EB<br>1 43 FB<br>1 44 E0<br>1 45 12              | ADM<br>DAA<br>WRN<br>JCN C1                            | INGREMENT RAM CHARAGTER ADDRESS<br>CLEAK ACCUMULATOR, MOVE CARRY TO 1 POSITION<br>OF ACCUMULATOR, CLEAR CARRY<br>AUD .1 S IN RAM TO CARRY FROM .01 S<br>CHARACTER IN RAM DECIMAL ADJUST ACCUM.                                                                       |

|-----------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 46 60<br>1 47 20<br>1 48 90                                               |                                                        | IF SY FROM $\cdot$ 1 SECOND = 1 BONT TEST FOR 9S<br>BECAUSE AFTER THE SUBTRACTION CY IS CLEARED                                                                                                                                                                      |

|                                                                             | SUB RE                                                 | TENTHS SECOND STILL IN ACCUMULATOR TEST<br>For tenths second = 9                                                                                                                                                                                                     |

| 1 50 E9<br>1 51 20<br>1 52 90                                               |                                                        | REAU .01 SECOND INTO ACCUMULATOR AND TEST<br>FOR .01 SECOND = 9                                                                                                                                                                                                      |

| 1 54 1C<br>1 55 58<br>1 56 41<br>1 57 B0<br>1 58 F1 NOTNINE<br>1 59 20      | - NOTNINE<br>JUM -<br>- WAIT100                        | IF •1 AND •J1 SECOND = •99 JUMP TO SPECIAL<br>WAIT ROUTINE WHICH ONLY WAITS FOR 100 HZ<br>TPANSITION ELSE OUTPUT 0 TO PORT NO• 5                                                                                                                                     |

| 1 5A 5C<br>1 5B 21<br>1 5C DF<br>1 5O E2<br>1 5E                            | 5 3                                                    | OUTPUT F (NEG. LOGIC 0) TO PORT NO. 5                                                                                                                                                                                                                                |

| 1 5F<br>1 60 63 USEC<br>1 61 23<br>1 62 F7<br>1 63 EE<br>1 64 FC<br>1 65 EC | SPC P1<br>TCC<br>ADM                                   | SELECT UNIT SECOND CHARACTER IN RAM<br>ADJ UNIT SECOND CHARACTER IN RAM TO CARRY<br>FROM TENTHS SECOND IN ACCUMULATOR<br>WRITE UNIT SECOND CHARACTER INTO RAM                                                                                                        |

| 1 66 63<br>1 67 23<br>1 68 F7<br>1 69 E8                                    | INC R3<br>SRC P1<br>TCC<br>ADM                         | SELECT TENS OF SECOND CHARACTER IN RAM                                                                                                                                                                                                                               |

| 1 6A EO<br>1 6B DA<br>1 6C EE<br>1 60 1A<br>1 6E 71<br>1 6F DO<br>1 70 EC   | LDM 10<br>ADM<br>JCN C0                                | WRITE TENS OF SECOND CHARACTER INTO RAM<br>ACCUMULATOR STILL CONTAINS TENS OF SECOND<br>ADD 10 IF TENS OF SECOND WAS A 6.THEN A<br>CARRY OCCURS IF SO SET TENS SECOND = 0<br>AND ADD THE CARRY TO UNIT MINUTES. IF TENS<br>SECOND CARRY = 0 THEN SET TENS SECOND = 0 |

| 1 71 63 MINUTE<br>1 72 23<br>1 73 F7<br>1 74 E8                             | INC RJ<br>SPC P1<br>TCC<br>AUM                         | SELECT UNIT MINUTE CHARACTER IN RAM                                                                                                                                                                                                                                  |

| 1 75 FR<br>1 76 E0<br>1 77 63<br>1 78 23                                    | DAA<br>WRM<br>INC R3<br>SRC P1                         | OF SECOND<br>WRITE UNIT MINUTES INTO RAM<br>SFLECT TENS OF MINUTES CHARACTER IN RAM                                                                                                                                                                                  |

| 1 79 F7<br>1 7A £6<br>1 7B E0<br>1 7C DA<br>1 7D EB<br>1 7E 1A<br>1 7F 82   | TCC<br>ADM<br>WPM<br>LDM 10<br>ADM<br>JCN C6<br>- HOUR | ADD TENS OF MINUTE CHARACTER IN RAM TO<br>CARKY FROM UNIT MINUTES IN ACCUMULATOR AND<br>WPITE TENS OF MINUTES INTO RAM<br>IF TENS OF MINUTES = 6 CARRY OVER TO UNIT<br>HOURS<br>JUMP TO HOUR IF TENS OF MINUTES CARRY = 0                                            |

1 80 00 LOM 0 1 81 E0 WRM INC R3 1 82 63 HOUR SRC P1 1 83 23 1 84 F7 1CC 1 85 EB ADM DAA 1 86 F8 1 87 ED WRM WRITE UNIT HOUR INTO RAM 1 88 63 INC R3 1 89 23 SRC P1 SELLOT TENS OF HOURS CHARACTER IN RAM 1 8A F7 TCC 1 8B EB ADM 1 8C E0 WRM WPITE TENS OF HOURS INTO RAM 1 80 FC CLD 1 8E 22 FIM P1 1 8F 35 3 5 1 90 23 SRC P1 1 91 E9 RDM READ UNIT SECOND INTO ACCUMULATOR 1 92 14 JCN A0 1 93 95 - TEST03 IF UNIT SECOND = 0 GO TEST FOR TENS OF 1 94 60 JUE SECOND = D OR 3 -- LLSE RETURN 1 95 22 TEST03 FIM P1 1 96 36 3 5 1 97 23 SRC P1 1 98 E9 READ TENS OF SECOND INTO ACCUMULATOR MAG 1 99 14 JUN AG 1 9A A2 - TENTHS FIM P1 1 98 22 1 90 30 ß IF TENS OF SECOND = 0 OP 3 GO TEST TENTHS 3 1 90 92 SECOND = 0 -- ELSE RETURN SUB RZ 1 9E 14 JCN AG 1 9F A2 TENTHS -1 A0 F0 CLC 1 A1 CG 391 FIM P1 1 A2 22 TENTHS 1 A3 34 3 4 1 A4 23 SPC P1 A5 E9 ROH IF TENTHS OF SECOND = 0 GO TEST FOR 1 A6 14 JCN AC HUNDRED THS OF SECONDS = 0 -- ELSE RETURN 1 A7 A9 HUNDFEDTHS 1 -A8 C C 89E 1 1 A9 22 HUNDREDTHS FIM P1 1 AA 33 3 3 SRC P1 IF HUNDPEDTHS SECOND = 0 GO SERVICE 1 AB 23 1 AC E9 SATELLITE POSITION DISPLAY -- ELSE RETURN RDM 1 AD 14 JCN AS 1 AE C4 - SPOS 1 AF CC 33L 1 BO FO WAIT100 SPECIAL WAIT ROUTINE TO KEEP 1HZ ON TIME CL5 1 61 20 FIM PC 1 82 00 3 C SLECT IN/OUT PORT NO.D FUR INPUT AND RESET SRC PE 1 63 21 1 84 EA READ **R**DR 1 85 F6 RAF IF 100 HZ IS NOT PRESENT GO BACK AND WAIT 1 86 1A JCN CC 1 87 84 - READ SOME MORE -- ELSE OUTPUT 1 HZ FIM PO 1 88 20 1 89 50 5 G SRC P0 OUTPUT E (NEG. LOGIC 1) TO PORT NO. 5 1 BA 21 1 BB DE LOM E 1 BC E2 WRP 1 80 01 LDN 1 WRITE OUT 1 TO RESET 100 HZ LATCH ON 1 BE E2 WRR OUTPUT PORT NO. 6 1 BF FO CLB

| 1 60 41                  | JUN -            |                                                                                     |

|--------------------------|------------------|-------------------------------------------------------------------------------------|

| 1 C1 60<br>1 C2          | - USEC           | GO BACK TO PROCESS UNIT SECONDS                                                     |

| 1 G3<br>1 C4 20 SPOS     |                  | SET UP SELECT OF RAM DZREG 1ZCHARACTERS 3                                           |

| 1 C5 13                  | 1 3              | THRU F, SATELLITE POSITION                                                          |

| 1 C6 21<br>1 C7 D1       | SRC PG<br>LDM 1  | WRITE A 1 TO RAM OUTPUT PORT TO TURN OFF                                            |

| 1 C8 E1                  |                  | OF A DUTET STOP STOP OF OOK                                                         |

| 1 C9 22<br>1 CA 1E       | FI∺ P1<br>1 E    | SET UP OUTPUT PORT NO. 1 SELECT AND P3                                              |

| 1 CB 21 RPAM             | SRC PG           |                                                                                     |

| 1 CC E9<br>1 CD 23       | RUM<br>SRC P1    | READ A SATELLITE POSITION CHAP FROM RAM                                             |

| 1 CE F4                  | CMA              |                                                                                     |

| 1 CF E2<br>1 D0 21       | WFR<br>SRC PL    | WPITE OUT A SATELLITE POSITION CHARACTER TO<br>OUTPUT PORT NUMBER 1                 |

| 1 01 03                  | LDN 3            |                                                                                     |

| 1 02 E1<br>1 03 D1       | WMP<br>Lom 1     | WRITE A 2 TO RAM OUTPUT PORT TO CLOCK DATA<br>INTO 2518 SHIFT REGISTER BUT A 1 MUST |

| 1 D4 E1                  | WYP              | STILL BE GOING OUT TO KEEP SHIFT REGISTERS                                          |

| 1 D5 71<br>1 C6 CB       | ISZ K1<br>- REAN | CLUCK OFF<br>INUPEMENT SATELLITE POSITION CHAR AUDPESS                              |

| 1 07 73                  | ISZ R3           | FILL HEX-32 SHIFT REGISTER (2518) TWICE,                                            |

| 1 08 CB<br>1 C9 D0       | - REAM<br>Lon o  | THAT IS, $2*(13 \text{ CHAR} + 3 \text{ BLANKS}) = 32 \text{ CHAR}$                 |

| 1 DA E1<br>1 DB CO       |                  | NEITE A C TO FAM OUTPUT PORT TO TURN SHIFT<br>RESISTERS CLOCK BACK ON               |

| 1 DC                     | BBL              | REGISTERS GLUCK BACK UN                                                             |

| 1 DD<br>1 OE             |                  |                                                                                     |

| 1 DF                     |                  |                                                                                     |

| 1 EO DO LOADA<br>1 E1 80 | LOM G<br>Xoh Ro  | CLEAR RC IN PREPARATION TO RECONSTRUCT BCD<br>Character in RC                       |

| 1 E2 51                  | JMS -            |                                                                                     |

| 1 E3 00<br>1 E4 A6       | - WAIT<br>LD R5  | GO TO WAIT TO GET BOD CHARACTER 1 BIT                                               |

| 1 E5 F1<br>1 E6 F6       | CLC<br>ZAR       | MON. WATA DIT TO 4 DOSTITOU AND APD TO DO                                           |

| 1 E7 8C                  | ADD PL           | MOVE DATA BIT TO 1 POSITION AND ADD TO RC                                           |

| 1 E8 BC<br>1 E9 51       | XCH RC<br>JMS -  | GET BOD CHARACTER 2 BIT                                                             |

| 1 EA GO                  | - WAIT           |                                                                                     |

| 1 EB A8<br>1 FC 8C       | LD R5<br>ADD RC  | DATA BIT IS ALREADY IN 2 POSITION JUST                                              |

| 1 ED BC                  | XCH RC           | ADD IT TO RC                                                                        |

| 1 EE 51<br>1 FF 00       | JMS -<br>- WAIT  | GET BOU CHARACTER 4 BIT                                                             |

| 1 FO A8<br>1 F1 F1       | LO Rº<br>CLC     |                                                                                     |

| 1 F2 F5                  | RAL              | MOVE DATA BIT TO 4 POSITION AND ADD 10 RC                                           |

| 1 F3 8C<br>1 F4 EC       | ADD RC<br>XCH RC |                                                                                     |

| 1 F5 51                  | JMS −            | GET BOD CHARACTER 8 BIT                                                             |

| 1 F6 00<br>1 F7 A8       | - WAIT<br>LD RS  |                                                                                     |

| 1 F8 F1<br>1 F9 F5       | CLC<br>RAL       |                                                                                     |

| 1 FA F5                  | RAL              | MOVE DATA BIT TO 8 POSITION AND ADD TO RC                                           |

| 1 FB 8C<br>1 FC BC       | ADD EC<br>XCH RC |                                                                                     |

| 1 FD C0                  | BCL              |                                                                                     |

| 1 FE<br>1 FF             |                  |                                                                                     |

|                          |                  |                                                                                     |

FIGURE 16. UTC(NBS) - SATELLITE CLOCK (MICROPROCESSOR)

## FIGURE 17. DIGITAL CLOCK PERFORMANCE MEASUREMENT SETUP

separately. The digital clock's delay was measured to be -5074 µs with no significant variation over an observed time of a few weeks. The delay is rather artificial since it is a function of software and can be set to any value by instruction. As an example the software can be adjusted to effectively remove delay from the digital clock. The receiver's delay was measured as a function of signal level and modulation index with the results shown below. The manufacturer specified the receiver's operating range to be between -100 and -130 dBm. The receiver delay for different modulation index was also investigated.

| Input Signal<br>Level |             | Delay (µs)<br>Modulation Index |                  |

|-----------------------|-------------|--------------------------------|------------------|

| (dBm)                 | <u>±50°</u> | ±60 <sup>0</sup>               | ±70 <sup>0</sup> |

| -100                  | ~           | 10,874                         |                  |

| -105                  |             | 10,844                         |                  |

| -110                  | 10,838      | 10,829                         | 10,814           |

| -115                  |             | 10,800                         |                  |

| -120                  |             | 10,748                         |                  |

| -125                  |             | 10,697                         |                  |

| -130                  | 10,626      | 10,598                         | 10,576           |

The delay versus signal level over the full manufacturer's specified range amounted to nearly 300  $\mu$ s with rather small sensitivity to modulation index. The receiving system variability implies problems when attempting to achieve a 100  $\mu$ s time synchronization. A change in antenna gain, local interference adding to the receiver's total power input, or receiver gain changes can cause problems. The reason for the receiver's delay sensitivity is believed due to the absence of automatic gain control (AGC). A limiter was used in the second IF only. It must be remembered that this receiver was optimized to enhance an ability not directly related to time recovery. Simple modifications should stabilize its delay considerably.

A discussion of path delay correction will be based on the results shown in figure 18 taken in the same manner as that of figure 16, but using a clock which counts the 100 Hz transitions using only TTL circuitry rather than under microprocessor software control. The resolution of the TTL approach is better than 10  $\mu$ s whereas the microprocessor, using 4 machine cycles (instructions 1B4 through 1B7), had a peak-to-peak variation of approximately 40  $\mu$ s. In either case the following discussion is valid. The equipment delay in this case was 46,162  $\mu$ s, most of this due to the clock using TTL only for 100 Hz transition counting.

In figure 18, at point X, the time interval counter indicates UTC(NBS) - Satellite Clock =  $40370 \ \mu$ s. The satellite clock also for point X provides the satellite's position as:

| Satellite | Longitude | 114.92 <sup>0</sup> W |

|-----------|-----------|-----------------------|

| Satellite | Latitude  | - 0.38 <sup>0</sup>   |

| Satellite | Radius    | 46 µs                 |

|                        |                                                       | Longitude             | La              | titude              |

|------------------------|-------------------------------------------------------|-----------------------|-----------------|---------------------|

| NBS/Boulder            | , CO                                                  | 105.26 <sup>0</sup> W | 4               | 0.00 <sup>0</sup> N |

| Wallops Isl            | and, VA                                               | 75.46 <sup>0</sup> W  | 3               | 7.85 <sup>0</sup> N |

| Using the delay slide  | rule, the path                                        | delays are comp       | uted to be      | :                   |

| Wallop                 | s Island to SMS                                       | 52                    | <b>128839</b> µ | S                   |

| SMS2 t                 | o NBS/Boulder                                         |                       | <b>125418</b> μ | S                   |

| Total                  | Path Delay                                            |                       | <b>254257</b> μ | S                   |

| Equipm                 | ent Delay                                             |                       | <b>46162</b> μ  | S                   |