NBS Technical Note 1221

# **NBS Wideband Sampling Wattmeter**

G. N. Stenbakken, O. B. Laug, T. H. Kibalo, B. A. Bell, and A. G. Perrey

he National Bureau of Standards<sup>1</sup> was established by an act of Congress on March 3, 1901. The Bureau's overall goal is to strengthen and advance the nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research to assure international competitiveness and leadership of U.S. industry, science and technology. NBS work involves development and transfer of measurements, standards and related science and technology, in support of continually improving U.S. productivity, product quality and reliability, innovation and underlying science and engineering. The Bureau's technical work is performed by the National Measurement Laboratory, the National Engineering Laboratory, the Institute for Computer Sciences and Technology, and the Institute for Materials Science and Engineering.

## The National Measurement Laboratory

Provides the national system of physical and chemical measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; provides advisory and research services to other Government agencies; conducts physical and chemical research; develops, produces, and distributes Standard Reference Materials; provides calibration services; and manages the National Standard Reference Data System. The Laboratory consists of the following centers:

# The National Engineering Laboratory

Provides technology and technical services to the public and private sectors to address national needs and to solve national problems; conducts research in engineering and applied science in support of these efforts; builds and maintains competence in the necessary disciplines required to carry out this research and technical service; develops engineering data and measurement capabilities; provides engineering measurement traceability services; develops test methods and proposes engineering standards and code changes; develops and proposes new engineering practices; and develops and improves mechanisms to transfer results of its research to the ultimate user. The Laboratory consists of the following centers:

# The Institute for Computer Sciences and Technology

Conducts research and provides scientific and technical services to aid Federal agencies in the selection, acquisition, application, and use of computer technology to improve effectiveness and economy in Government operations in accordance with Public Law 89-306 (40 U.S.C. 759), relevant Executive Orders, and other directives; carries out this mission by managing the Federal Information Processing Standards Program, developing Federal ADP standards guidelines, and managing Federal participation in ADP voluntary standardization activities; provides scientific and technological advisory services and assistance to Federal agencies; and provides the technical foundation for computer-related policies of the Federal Government. The Institute consists of the following divisions:

# The Institute for Materials Science and Engineering

Conducts research and provides measurements, data, standards, reference materials, quantitative understanding and other technical information fundamental to the processing, structure, properties and performance of materials; addresses the scientific basis for new advanced materials technologies; plans research around cross-cutting scientific themes such as nondestructive evaluation and phase diagram development; oversees Bureau-wide technical programs in nuclear reactor radiation research and nondestructive evaluation; and broadly disseminates generic technical information resulting from its programs. The Institute consists of the following Divisions:

- Basic Standards<sup>2</sup>

- Radiation Research

- Chemical Physics

- Analytical Chemistry

- Applied Mathematics

- Electronics and Electrical Engineering<sup>2</sup>

- Manufacturing Engineering

- Building Technology

- Fire Research

- Chemical Engineering<sup>3</sup>

- Information Systems Engineering

- Systems and Šoftware Technology

- Computer Security

- Systems and Network Architecture

- Advanced Computer Systems

- Ceramics

- Fracture and Deformation<sup>3</sup>

- Polymers

- Metallurgy

- Reactor Radiation

<sup>&</sup>lt;sup>2</sup>Some divisions within the center are located at Boulder, CO 80303. <sup>3</sup>Located at Boulder, CO, with some elements at Gaithersburg, MD

Research Information Center National Bureau of Standards Gaithersburg, Maryland 20899

> NBSC CC100 .USM53 MO.1001 987 C2

NBS Technical Note 1221

# **NBS Wideband Sampling Wattmeter**

G. N. Stenbakken, O. B. Laug, T. H. Kibalo, B. A. Bell, and A. G. Perrey

Electrosystems Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Gaithersburg, MD 20899

May 1987

U.S. Department of Commerce Malcolm Baldrige, Secretary

National Bureau of Standards Ernest Ambler, Director National Bureau of Standards Technical Note 1221 Natl. Bur. Stand. (U.S.), Tech. Note 1221 103 pages (May 1987) CODEN: NBTNAE U.S. Government Printing Office Washington: 1987 For sale by the Superintendent of Documents, U.S. Government Printing Office, Washington, DC 20402

## Table of Contents

|      | p                                    | age                  |

|------|--------------------------------------|----------------------|

| List | of Figures                           | v                    |

| List | of Tables                            | vi                   |

| Prog | ram Listings                         | vi                   |

| 1.   | INTRODUCTION                         | 1                    |

| 2.   | SYSTEM DESCRIPTION                   | 3                    |

|      | 2.1. Basic Sampling Principles       | 3                    |

|      | 2.1.1. Sampling Errors               | 3                    |

|      | 2.2. Theory of Operation             | 6<br>8<br>11         |

|      | 2.4.1. Pascal Routines               | 11                   |

|      | 2.5. Specifications                  | 12                   |

| 3.   | OPERATING THE SAMPLING WATTMETER     | 12                   |

|      |                                      | 12<br>16             |

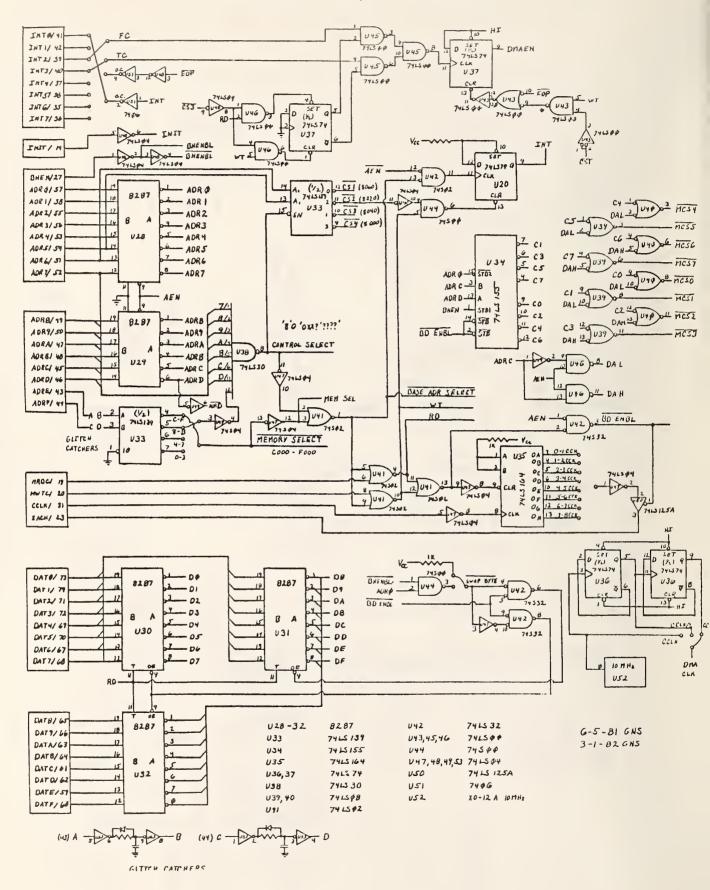

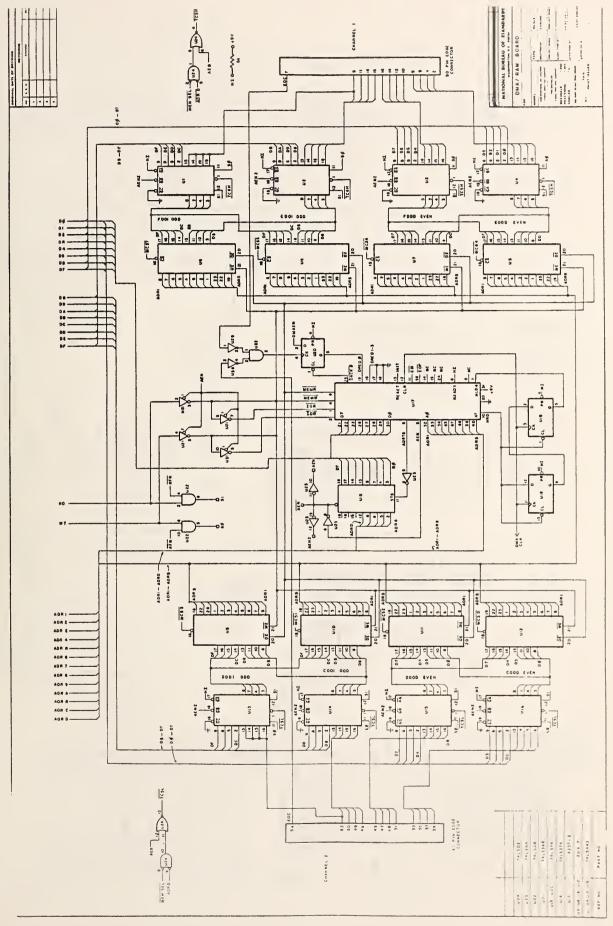

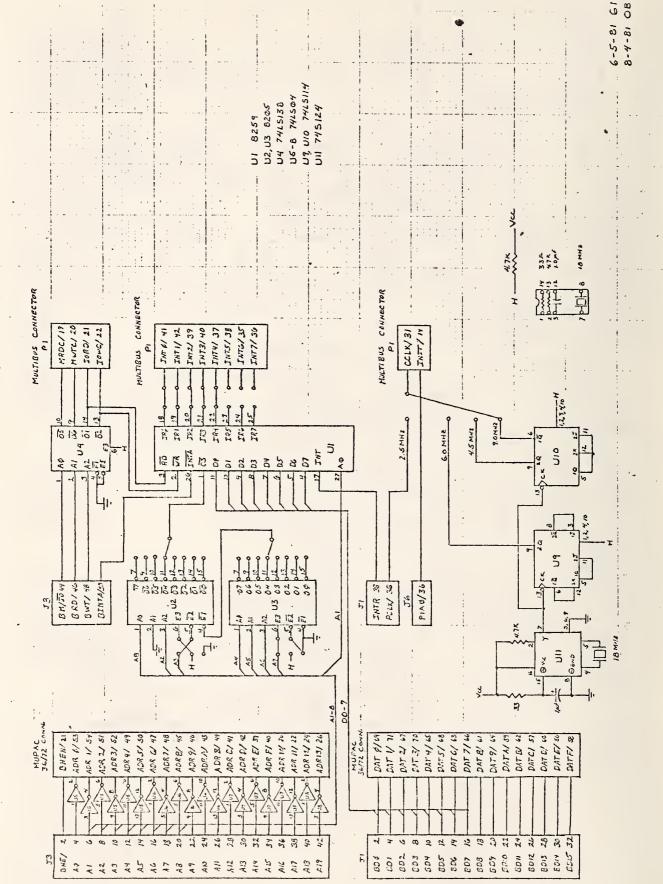

| 4.   | HARDWARE                             | 20                   |

|      | 4.1. Amplifier/Data Converter Module | 20                   |

| 6    | 4.1.2. Analog Isolation              | 21<br>23<br>23<br>24 |

|      | 4.2. Summation Interval Control      | 26                   |

|      |                                      | 26<br>27             |

|      | 4.3. Differential Time Delay         | 31                   |

|      |                                      | 31<br>33             |

## page

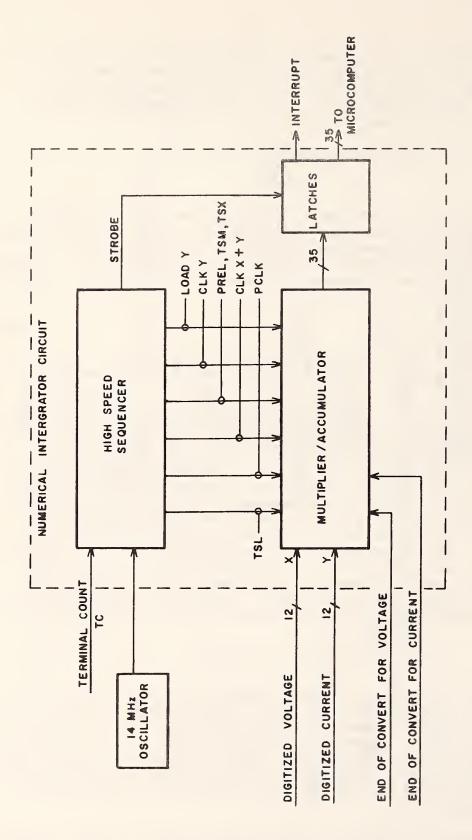

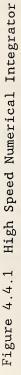

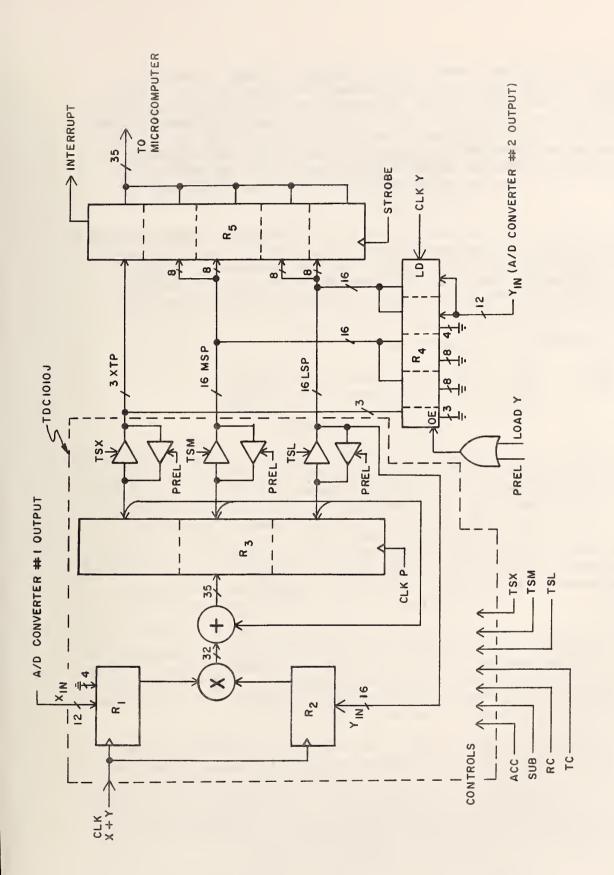

|      | 4.4.  | High Sp                                        | peed Numerical                                       | Integra    | ator | r. |      |   |   | • |   | • |   |             |        |   |        | • |             |             |        | 35                         |

|------|-------|------------------------------------------------|------------------------------------------------------|------------|------|----|------|---|---|---|---|---|---|-------------|--------|---|--------|---|-------------|-------------|--------|----------------------------|

|      |       | 4.4.1.<br>4.4.2.<br>4.4.3.                     | Overview<br>Multiplier-Ac<br>High Speed Se           | cumulato   | or   | •  |      |   |   |   |   |   |   |             |        |   |        |   |             |             |        | 35<br>35<br>38             |

|      | 4.5.  | Direct                                         | Memory Access                                        | Circuit    | ry   |    | • •  |   |   |   |   | • |   | •           |        |   | •      |   |             |             |        | 41                         |

|      |       | 4.5.1.<br>4.5.2.                               | Overview<br>Circuit Descr                            |            |      |    |      |   |   |   |   |   |   |             |        |   |        |   |             |             |        | 41<br>41                   |

|      | 4.6.  | Microc                                         | omputer and Me                                       | emory .    | •    | •  |      | • |   |   |   |   |   |             | •      |   |        | • | •           |             |        | 44                         |

|      |       | 4.6.1.<br>4.6.2.                               | Microcomputer<br>Memory                              |            |      |    |      |   |   |   |   |   |   |             |        |   |        |   |             |             |        | 44<br>44                   |

|      | 4.7.  | Keyboa                                         | rd and Display                                       | • • • •    | •    | •  | • •  |   | • | • |   | • |   |             |        |   |        |   | •           |             |        | 45                         |

|      |       | 4.7.1.<br>4.7.2.<br>4.7.3.                     | Overview<br>Keyboard Elec<br>Display                 | tronics    | •    | •  |      | • |   | • | • |   | • |             | •      | • | •      |   |             |             |        | 45<br>45<br>45             |

| 5.   | SOFTW | ARE                                            |                                                      |            |      |    |      | • |   |   |   |   |   |             |        |   |        |   |             | •           | •      | 48                         |

|      | 5.1.  | Main C                                         | ontrol                                               |            |      |    |      | • |   |   | • |   |   | •           |        |   | •      |   |             |             |        | 48                         |

|      | 5.2.  | Pascal                                         | Procedures .                                         |            |      | •  | • •  | • | • | • | • | • |   | •           |        | • | •      | • | •           | •           |        | 50                         |

|      |       | 5.2.1.<br>5.2.2.<br>5.2.3.<br>5.2.4.<br>5.2.5. | DoKey<br>Parameter Set<br>SetDMA<br>Disp<br>Test NSA | ting .<br> | •    | •  | •••• | • |   |   |   |   |   | •<br>•<br>• | •<br>• |   | •<br>• |   | •<br>•<br>• | •<br>•<br>• | •<br>• | 50<br>53<br>60<br>61<br>62 |

|      | 5.3.  | Assemb                                         | ly Language Ro                                       | outines    |      |    |      | • | • |   | • |   | • |             | •      |   |        |   |             |             |        | 64                         |

| 5.   | CALIB | RATION T                                       | ESTS                                                 |            | •    |    |      | • |   | • | • |   |   |             |        |   |        |   | •           | •           |        | 64                         |

| 7.   | REFER | ENCES .                                        |                                                      |            | •    |    |      |   |   |   |   |   |   |             |        |   |        |   |             |             |        | 71                         |

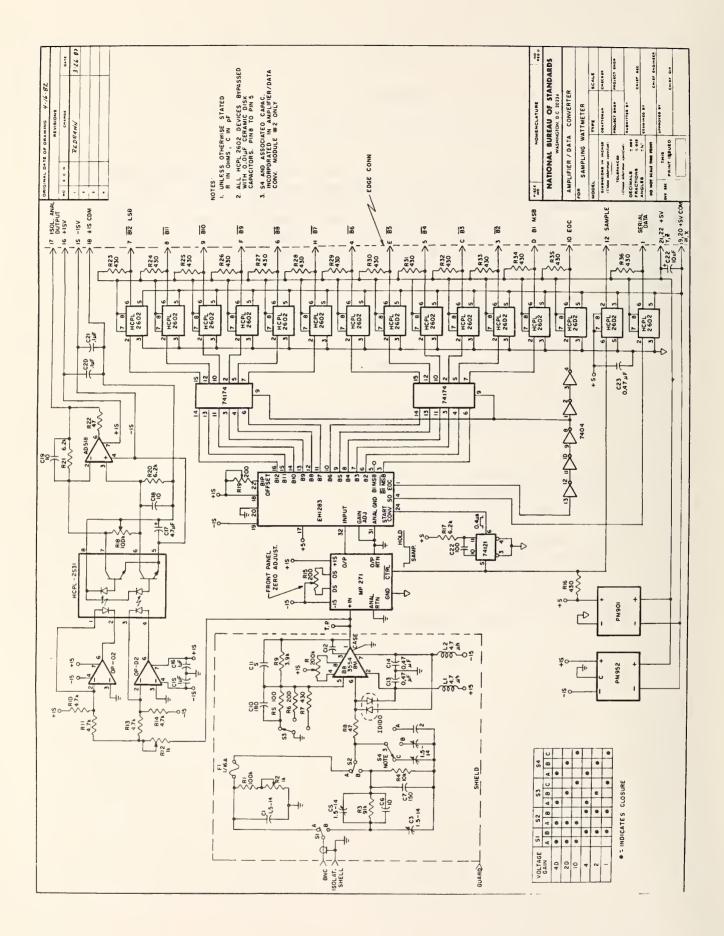

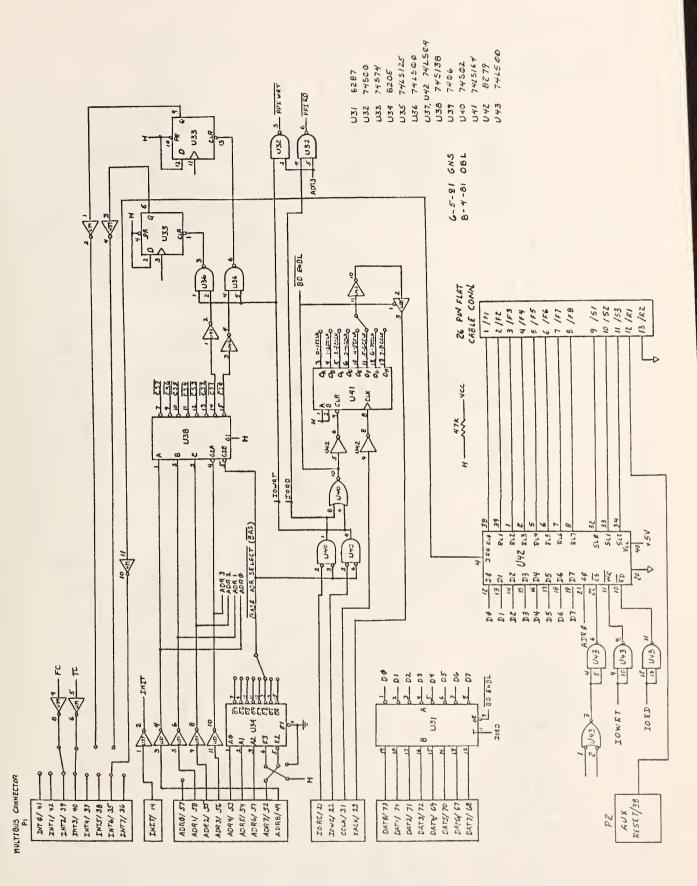

| Abbe | endix | A - Deta                                       | iled Circuit D                                       | iagrams    |      |    |      |   |   |   |   |   |   |             |        |   |        |   |             |             |        | A1                         |

| Abbe | endix | B - Pasc                                       | al Programs .                                        |            |      | •  |      |   |   |   |   |   |   |             |        |   |        |   |             |             |        | B1                         |

Į

# List of Figures

| ÷ | 0 | $\sim$ | ~ |

|---|---|--------|---|

| μ | a | В      | e |

| Sampling of Voltage and Current Sinewaves for Measuring     | 4                       |

|-------------------------------------------------------------|-------------------------|

|                                                             |                         |

|                                                             | 9                       |

| Block Diagram of the NBS wideband Sampling wattmeter        | 9                       |

|                                                             | 13                      |

| 32-Character Alphanumeric Display                           | 13                      |

| Simplified Schematic of Amplifier/Data Converter            | 22                      |

| Floating Measurement System Showing Effect of Common-Mode   |                         |

| Signal                                                      | 25                      |

| Summation Interval Control Circuitry                        | 28                      |

| Timing Diagram for Summation Interval Control               | 29                      |

|                                                             |                         |

| Sample Convert Command Pulse Generator Circuit with         |                         |

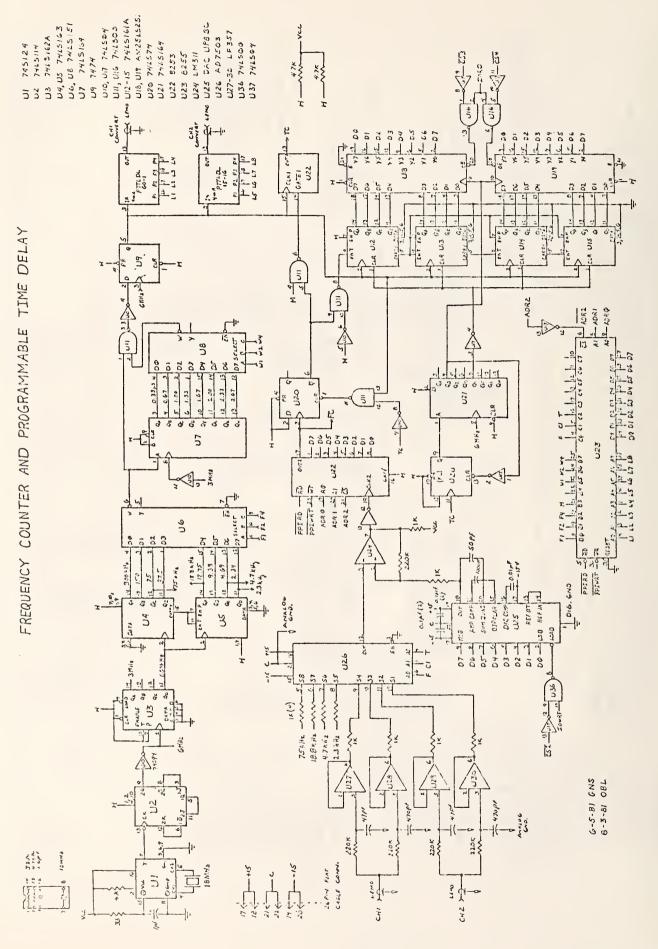

| Programmable Differential Time Delay                        | 34                      |

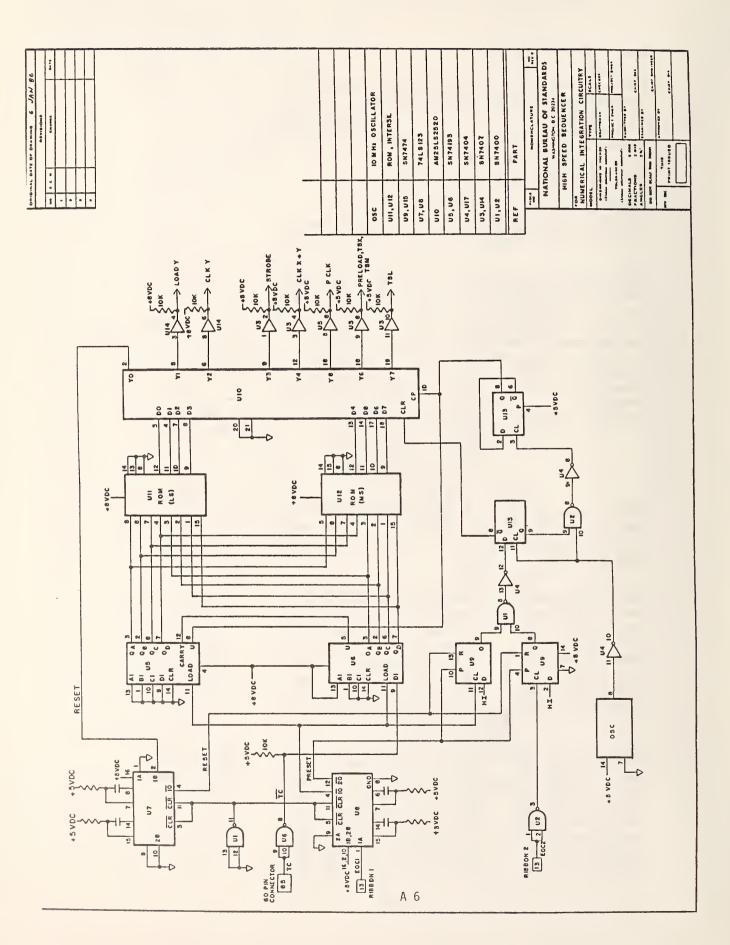

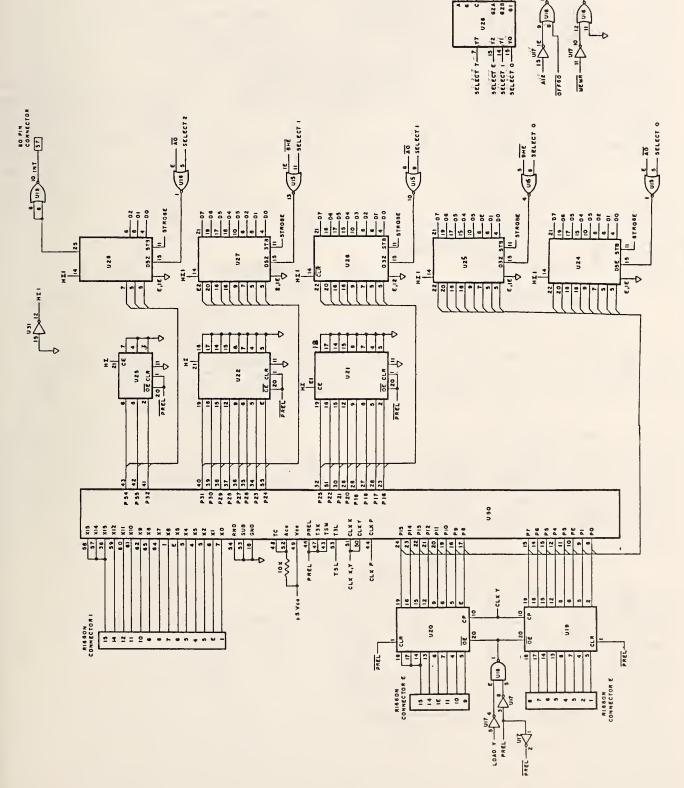

| High Speed Numerical Integrator                             | 36                      |

| Multiplier-Accumulator Circuit                              | 37                      |

| High Speed Sequencer for Multiplier-Accumulator             | 40                      |

|                                                             |                         |

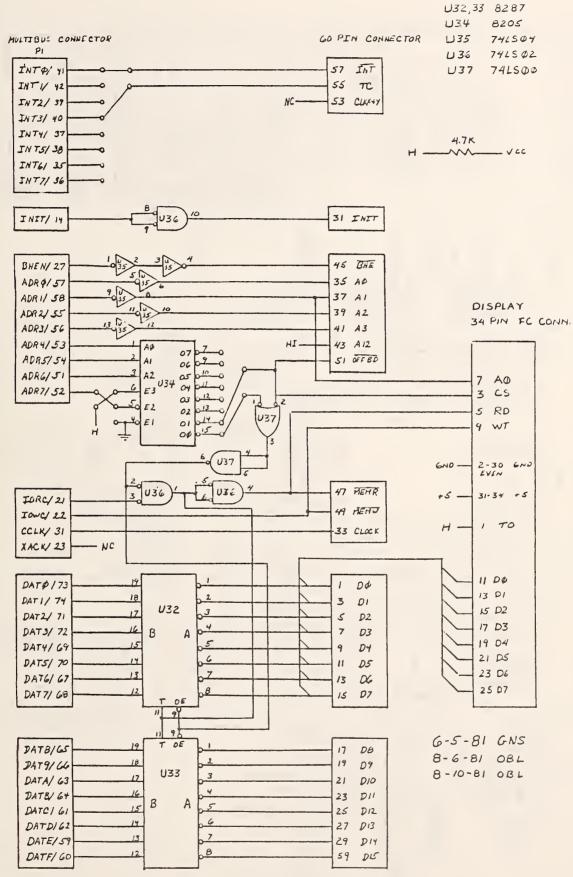

| Direct-Memory-Access Control Circuitry                      | 42                      |

| Keyboard Circuitry                                          | 46                      |

|                                                             |                         |

|                                                             |                         |

|                                                             |                         |

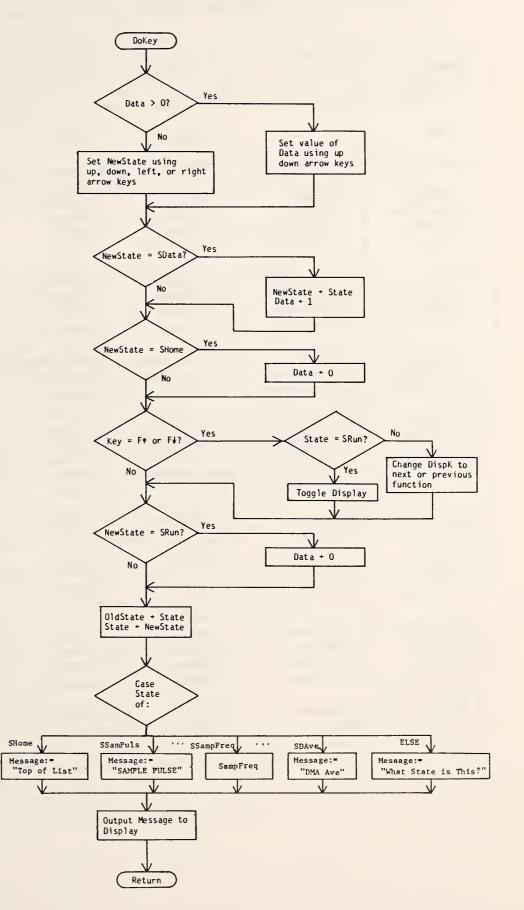

| Flow Chart for Procedure DoKey                              | 51                      |

|                                                             |                         |

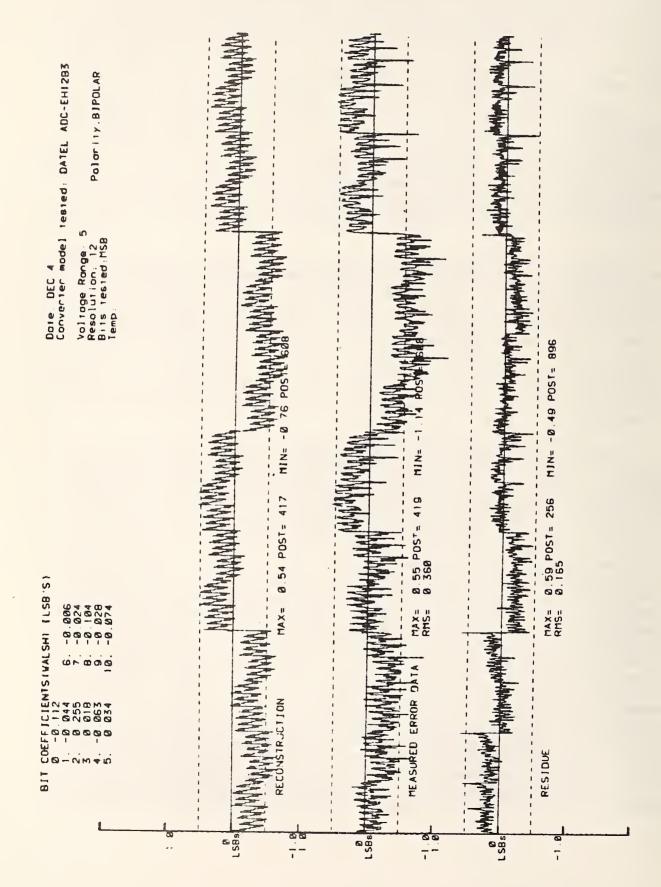

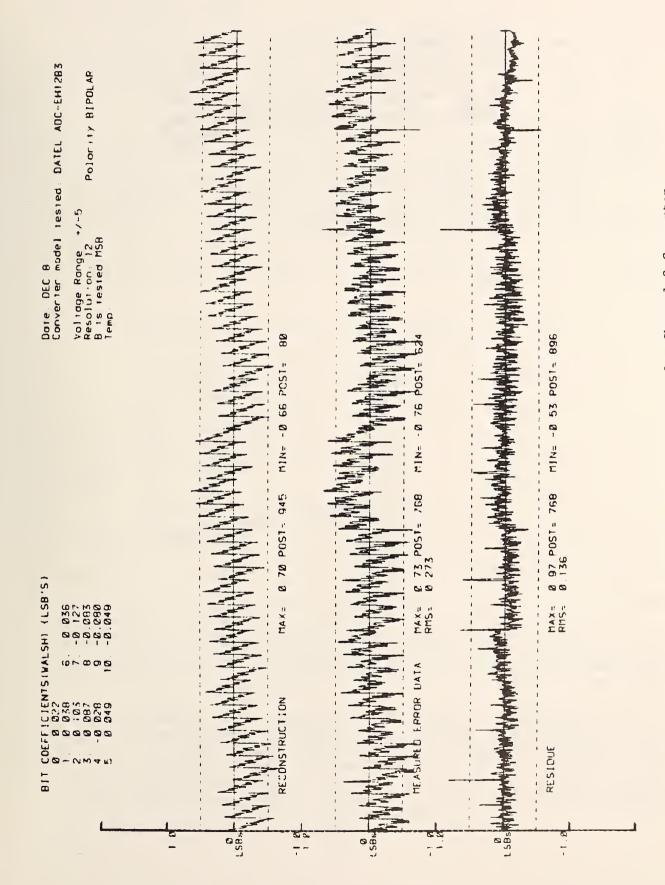

| A/D Converter Code Errors for Channel 1 Converter           | 66                      |

| A/D Converter Code Errors for Channel 2 Converter           | 67                      |

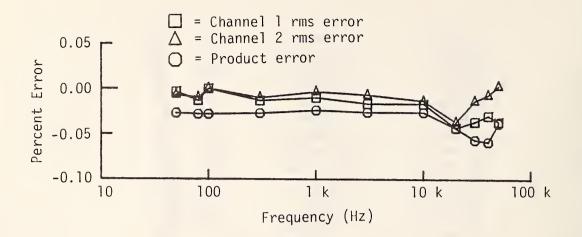

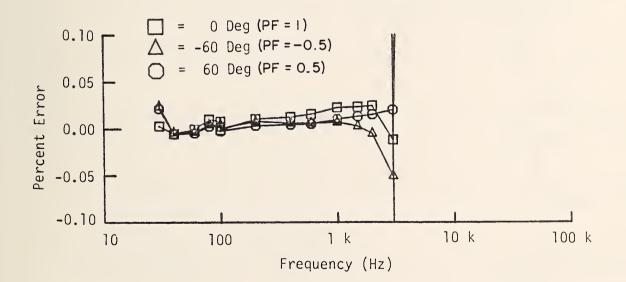

| Frequency Response of the NBS Wideband Sampling Wattmeter,  |                         |

|                                                             | 68                      |

| Difference Between NBS Sampling Wattmeter and Thermal       |                         |

| Wattmeter in Percent of Full Scale While Measuring Power    |                         |

| in Signals with 120 V and 5 A and with Power Factors of     |                         |

|                                                             | 69                      |

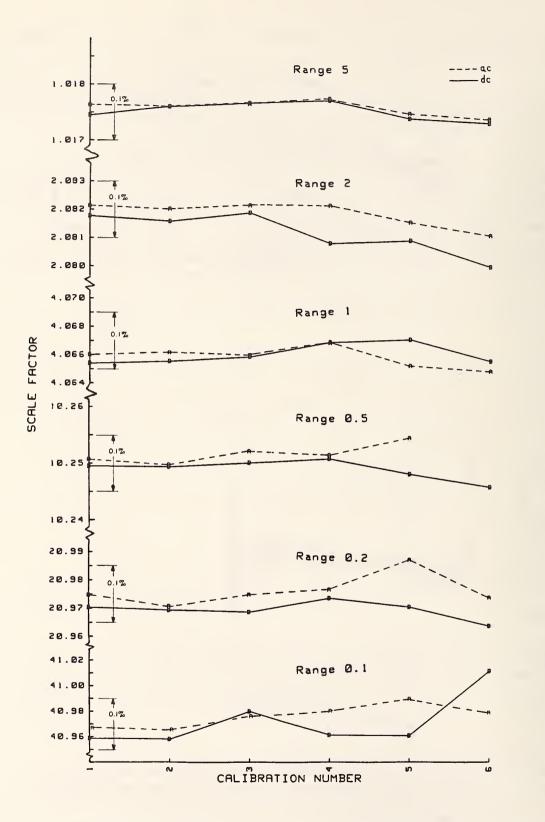

| Calibration Test Data of dc and 100 Hz Scale Factor Gain    |                         |

| for Ranges of Amplifier 1 from April 1983 to January 1985 . | 70                      |

|                                                             | Simple Sinusoidal Power |

## List of Tables

page

page

| Table 3.1.1<br>Table 3.1.2<br>Table 3.1.3                               | Parameter Selection Menu and Default Values                                                   | 15<br>17<br>18                         |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------|

| Table 4.2.1<br>Table 4.2.2<br>Table 4.3.1                               | Control Signals of Interval Control Source                                                    | 30<br>30<br>31                         |

| Table 4.3.2<br>Table 4.3.3<br>Table 4.3.4<br>Table 4.3.5<br>Table 4.3.6 | Sample Frequency Control                                                                      | 32<br>32<br>32<br>32<br>32<br>32<br>32 |

| Table 4.4.1<br>Table 4.4.2<br>Table 4.4.3                               | High Speed Numerical Integrator Sequences                                                     | 39<br>39<br>41                         |

| Table 4.6.1<br>Table 4.6.2                                              | Microcomputer Memory Map                                                                      | 44<br>45                               |

| Table 5.2.1<br>Table 5.2.2<br>Table 5.2.3<br>Table 5.2.4                | Present State and Next State for the Four Arrow Keys Parameters with a Small Number of Values | 52<br>54<br>55<br>58                   |

| Table 6.1.1                                                             | Differential Time Delays for Amplifiers                                                       | 68                                     |

## Program Listings

| Listing 5.2.1 PB | ROCEDURE   | SampFreq .  | • • • • •  | • • • •  | • • | • | • |     |   |   | • | • | 54 |

|------------------|------------|-------------|------------|----------|-----|---|---|-----|---|---|---|---|----|

| Listing 5.2.2 PH | ROCEDURE   | SetIVal and | PROCEDURE  | DelaySmp | •   | • | • |     | • | • |   |   | 56 |

| Listing 5.2.3 PH | ROCEDURE : | SetCh1Scale | and PROCED | URE SetR |     |   | • |     | • | • | • | • | 58 |

| Listing 5.2.4 PH | ROCEDURE   | SetDMA      |            |          | ••• | • | • | ••• | • |   | • | • | 60 |

| Listing 5.2.5 PH | ROCEDURE   | DispPwr and | PROCEDURE  | Disp .   |     | • | • |     |   |   |   | • | 62 |

| Listing 5.2.6 PH | ROCEDURE ' | TestNSA     |            |          |     | • | • |     |   | • |   |   | 63 |

NBS WIDEBAND SAMPLING WATTMETER G. N. Stenbakken, O. B. Laug, T. H. Kibalo B. A. Bell, and A. G. Perrey

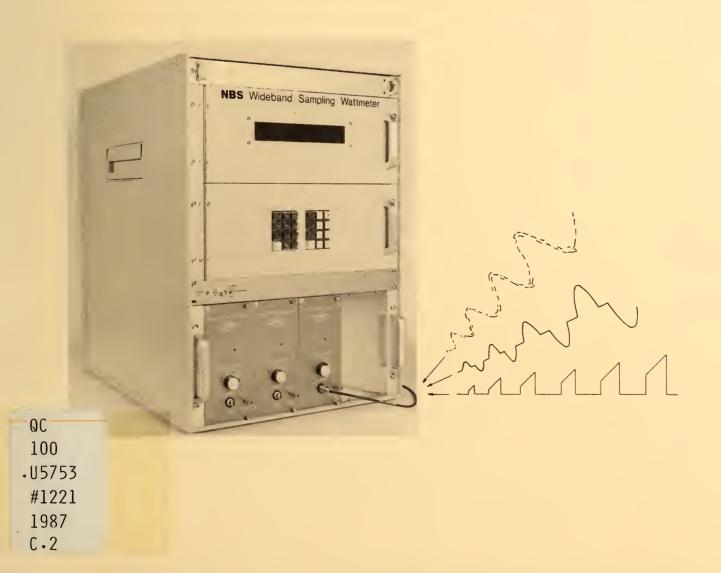

The design and operation of a wideband sampling wattmeter capable of measuring distorted power signals with fundamental frequencies from 1 Hz to 10 kHz and harmonics up to 100 kHz is described. The microcomputer controlled wattmeter uses asynchronous sampling of the voltage and current signals. The errors associated with this type of operation are described, as are various methods of correcting some of these errors. A hardware multiplier-accumulator allows a large number of power signal samples to be integrated for each measurement. Sampling rates are variable up to a maximum of 300 kHz. A direct-memory-access unit is used to capture 4096 samples of both the voltage and current signals. These data are used to calculate the average and rms values of these signals.

A special feature of the sampling wattmeter is the use of programmable time delay circuits to compensate for differential time delays between the two input channels. Performance tests of the wattmeter show that it has a measurement uncertainty of less than  $\pm$  0.1 percent of full-scale amplitude over the above described frequency range.

This technical note gives schematic diagrams of the circuits used in this wattmeter and describes their operation. The software is also described, and flow charts and selected program listings are provided for the programs written in Pascal. The results of calibration of the instrument over the past year are also presented.

Key words: calibration; power measurement; sampling voltmeter; sampling wattmeter; signal analyzer; truncation error; wideband sampling wattmeter.

## 1. INTRODUCTION

The design, operation and performance of a new wideband sampling wattmeter are described in this report. The wattmeter was developed to meet the growing need for accurate methods of measuring highly distorted power signals in the 1 kHz to 100 kHz frequency range. The development of this instrument was carried out at the National Bureau of Standards (NBS) and received substantial financial support from the Department of Energy (DOE). DOE's interest in this project is related to their efforts to accurately characterize the efficiency of dc/ac converter systems used in powering electric vehicles. Such systems operate by chopping the dc power source at frequencies ranging from 1 to 10 kHz [1]. These systems produce signals with significant harmonics above 50 kHz on both the ac output as well as on the chopped dc input power. Many other DOE technology programs also require the accurate measurement of distorted power signals. These efforts include more widespread use of dc/ac conversion as a result of expanded use of HVDC transmission, use of large battery storage technology by power utilities, and solar cell power generation systems.

Based on these needs, NBS began the development of a wideband wattmeter which could accurately measure distorted power in systems with fundamental signal frequencies up to 10 kHz and harmonics up to 100 kHz with an uncertainty of less than  $\pm$  0.1 percent of full scale amplitude. Several techniques were considered as candidates for this new wattmeter. Time-division-multipliers and thermal-converter-based techniques have very good accuracies at power line frequencies, but their accuracy drops rapidly at frequencies above 1 kHz. Analog multipliers, on the other hand, have the necessary frequency response but not the desired accuracy. The approach selected was a dual-channel sampling wattmeter using custom designed input amplifiers, commercial track-and-hold (T/H) amplifiers, and analog-to-digital (A/D) converters. An earlier sampling wattmeter that measured signals up to 5 kHz had already been successfully developed at NBS [2]. This new wideband NBS sampling wattmeter operates at sampling rates up to 300 kHz using 12-bit A/D converters. To accommodate future upgrading of the wattmeter, the input sections of the wattmeter have been designed as plug-in modules. The digital portions of the wattmeter can accommodate 16-bit data at sampling rates of up to 1 MHz.

The design of the NBS wideband sampling wattmeter makes accurate operation possible over a wide frequency range. Power measurements can be made on dc signals and ac signals from 1 Hz to over 100 kHz. A high speed digital multiplier-accumulator is used to calculate the power in real time from a large number of input signal samples. Real time computations, together with the fixed sampling approach, accounts for the wide frequency range of the wattmeter. The use of trigger and counter circuits provides an automatic summation interval control which accounts for the high accuracy, independent of the frequency, from 1 Hz to 10 kHz. Response from 10 kHz to over 100 kHz is limited by the input amplifiers. A feature unique to the NBS sampling wattmeter is the use of programmable time delay circuits to compensate for differential time delays between the two input channels. Without this correction the accuracy of the wattmeter would be seriously affected at higher frequencies.

A microcomputer is used to control the operation of the wattmeter. Direct-memory-access (DMA) channels are used to store data from the two channels which allows measurements to be made on the input voltage and current waveforms. New algorithms were developed which improve the accuracy with which the average and rms values of these two signals are determined.

Chapter 2 describes the basic operating principles of the NBS wideband sampling wattmeter. A brief description is given of the circuits and software used in the wattmeter. The operator interface with the sampling wattmeter is covered in chapter 3. Each of the settable parameters and their range of possible values is described. Chapter 4 provides a detailed description of the hardware and circuits used in the wattmeter. Simplified circuit diagrams are given and the operation of the circuits is explained. Chapter 5 presents flow charts for the major software and explains the operation of the software. The results of the many calibration tests performed on the sampling wattmeter are presented in chapter 6. Appendix A shows the complete circuit diagrams of the sampling wattmeter and appendix B provides the major software programs.

## 2. SYSTEM DESCRIPTION

This section describes the basic principles of operation of sampling wattmeters with emphasis on the approach taken for the NBS wideband sampling wattmeter. Details on the theory of sampling wattmeters can be found in references [3], [4] and [5]. A brief overview of the hardware and software used in the NBS wideband sampling wattmeter is also given in this chapter.

## 2.1. Basic Sampling Principles

For periodic power signals having a period of T seconds, voltage v(t), and current i(t), the true power P is given by

$$P = \frac{1}{T} \int_{0}^{T} v(t) i(t) dt .$$

(1)

Sampling wattmeters measure power by averaging many samples of instantaneous power. These instantaneous power values are obtained by sampling the voltage and current waveforms simultaneously, converting these samples to digital values, and calculating their products. If the voltage at time  $t_k$  is denoted as  $V(t_k)$  and the current as  $I(t_k)$ , then the average power W is given by

$$W = \frac{1}{n} \sum_{k=0}^{n-1} V(t_k) I(t_k) , \qquad (2)$$

where n is the number of samples used in the average. The major error in determining W comes from two sources: first, the limitations inherent in the sampling process, and second, the imperfections of the hardware used to make the measurements. The errors from the sampling process are described next, with reference to the sampling approach used in the NBS sampling wattmeter. The errors due to hardware imperfections are described in chapter 6.

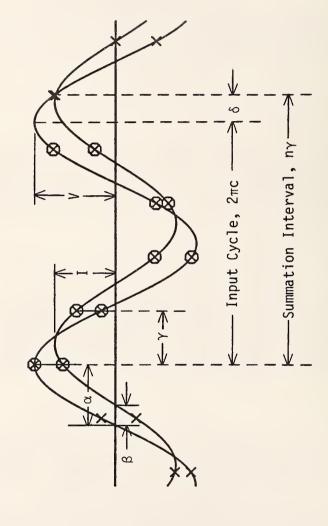

#### 2.1.1. Sampling Errors

The easiest way to look at the errors associated with sampling wattmeters is to consider measuring simple sinusoidal power. Figure 2.1.1 shows the relationship between the sample times and the associated voltage and current signals. To calculate the power in such signals, the sample values from a finite interval of the waveforms are used. This interval is called the summation interval and is represented in figure 2.1.1 by the circled sample values. The sample interval can be normalized by expressing it in terms of the phase angle change which either signal makes during this interval. Thus, for a signal of period T seconds and a sampling rate of r samples per second, the sample interval  $\gamma$  in radians per sample is given by

$$\gamma = \frac{2\pi}{rT} \quad . \tag{3}$$

- X Sample Values

- 🔇 Values used in Summation

The voltage and current sample values are given by

$$V(t_k) = V_k = V \sin(k\gamma + \alpha) \tag{4a}$$

and

$$I(t_k) = I_k = I \sin(k\gamma + \alpha + \beta) , \qquad k = 0 \text{ to } n-1$$

(4b)

where k is the sample number,  $\alpha$  is the phase angle of the first voltage sample relative to the zero crossing,  $\beta$  is the relative phase angle between the current and voltage, and V and I are the peak values. Thus, if the power W is calculated as above, this gives,

$$W = \frac{VI}{2} \left[ \cos \beta - \frac{1}{n} \sum_{k=0}^{n-1} \cos(2k\gamma + 2\alpha + \beta) \right] .$$

(5)

For sine waves the true power P is equal to the first term: thus, the summation terms can be interpreted as the error E. This can be expressed in terms of the truncation angle  $\delta$  which is the difference between the summation interval n $\gamma$  and the nearest number of whole cycles c of the signal, that is  $\delta = 2\pi c - n\gamma$ . Using these factors the error is given by [6]

$$E = \frac{VI}{2n} \frac{\sin \delta}{\sin \gamma} \cos(2\alpha + \beta - \delta - \gamma) , \qquad (6)$$

or as

$$E = \frac{VI\gamma}{4\pi c}, \frac{\sin \delta}{\sin \gamma} \cos(2\alpha + \beta - \delta - \gamma) , \qquad (7)$$

where c' is the number of cycles and partial cycles of the signal in the summation interval, and is given by

$$c' = \frac{n\gamma}{2\pi} . \tag{8}$$

The error given in (6) and (7) is called the truncation error and arises because the summation interval does not exactly match an integral number of cycles of the signal. Equation 7 shows that if the truncation angle  $\delta$  is zero this error is zero. This is the reason many sampling wattmeters use synchronous sampling for which  $\delta$  is zero.

For the NBS sampling wattmeter to achieve its desired accuracy, the truncation error must be much less than  $\pm$  0.1 percent of the full scale amplitude (FSA). Equation (6) shows that this error can be reduced by keeping  $\delta$  small and n large. Consider the problem caused by not controlling  $\delta$ . In this case, (7) shows that the truncation error is inversely proportional to c' the number of signal cycles in the summation interval. Thus, at low signal frequencies the summation interval must be very long. For example, to keep this error to less than  $\pm$  0.1 percent FSA requires a summation interval of at

least 160 cycles. For a 10 Hz signal this means a measurement time of 16 seconds, which is unacceptable.

Although the NBS sampling wattmeter has asynchronous sampling, it uses a trigger and cycle counting hardware to control the summation interval. By starting and stopping the summation interval with a trigger pulse synchronized with the signal being measured, the truncation angle  $\delta$  is kept to less than the sample interval  $\gamma$ . Equation (6) shows that in this case the maximum error occurs when sin  $\delta = \sin \gamma$  and the cosine term is  $\pm 1$ . Then, the maximum error is given by

$$E_{\max} = \pm \frac{VI}{2n} , \qquad (9)$$

which is independent of the input frequency. Thus, the truncation error can be made small by taking a large number of samples n independent of the input frequency. With the NBS sampling wattmeter, power measurements are typically made with an n of greater than 150,000 samples so that the truncation error is negligible. With a sampling rate of 300 kHz, this number of samples requires a summation interval of about one half second.

## 2.2. Theory of Operation

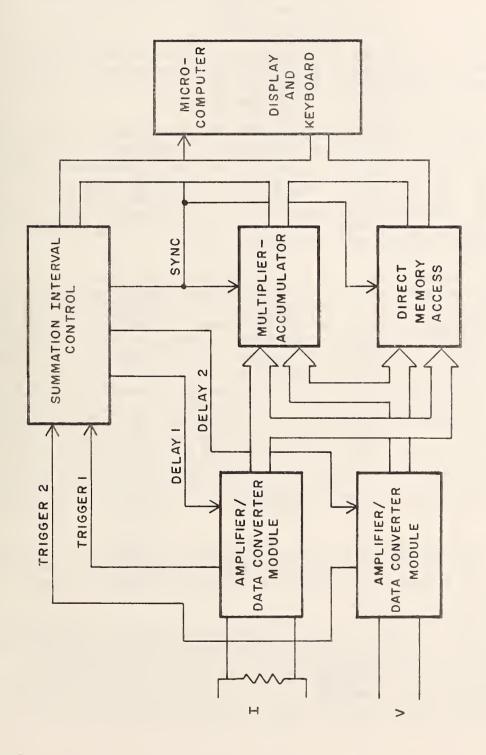

This section briefly describes how the wideband sampling wattmeter performs the operations described in the previous section (2.1). Figure 2.2.1 is a simplified block diagram of the wattmeter. The current and voltage signals are sampled and converted to digital quantities in the two Amplifier/Data Converter modules. This circuitry scales the input signal to a ± 5 V ac amplitude and then digitizes this signal. Scaled copies of the input signals called Trigger 1 and 2 are sent to the Summation Interval Control circuitry. In turn, the Summation Control circuitry provides the Delay 1 and Delay 2 signals to the Amplifier/Data Converter Modules, which control the sample time for the data conversion circuitry.

The trigger signals are used by the Summation Interval Control circuitry to synchronize the wattmeter data processing with the period of the input signals. As mentioned in section 2.1, this synchronization is required to get accurate measurement results. The Summation Interval Control circuitry performs the synchronization by counting a number of the periods of the input signals using one of the trigger signals. When the proper number of periods has been counted, a synchronization signal Sync is sent to the data processing circuits to indicate the termination of one summation interval and the start of the next one. The Summation Interval Control circuitry also counts the number of samples taken during each such interval and passes this number on to the microcomputer.

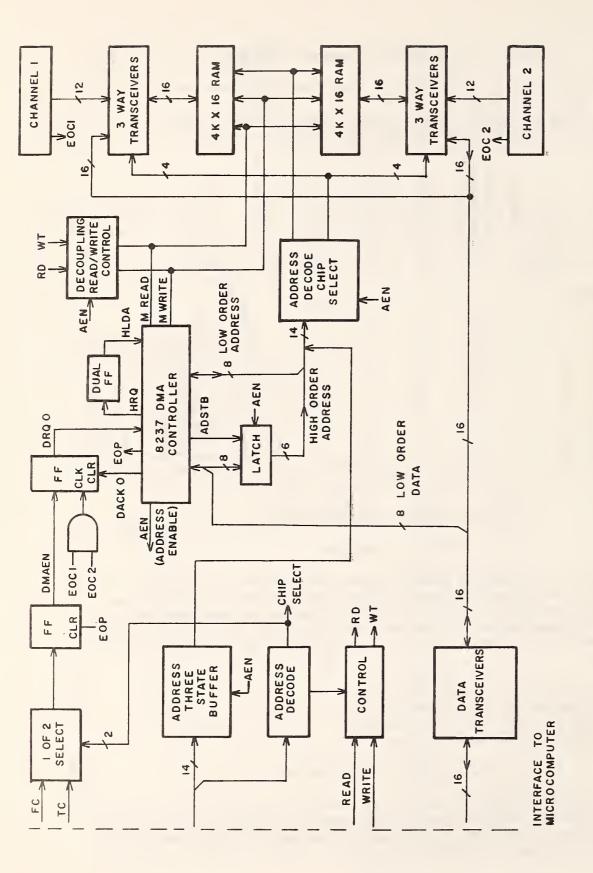

The two 12-bit binary numbers from the converter modules are sent to the Multiplier-Accumulator circuitry and to the Direct-Memory-Access (DMA) memory circuitry. The Multiplier-Accumulator multiplies the two numbers and sums the resulting products over the intervals controlled by the Sync signal from the Summation Interval Control circuitry. At the end of each interval the accumulated product results are sent to the microcomputer. The DMA circuitry

Figure 2.2.1 Simplified Block Diagram of Wideband Sampling Wattmeter

7

stores up to 4096 consecutive pairs of numbers from the two input channels.

The microcomputer calculates the average power for each of the summation intervals from the accumulated products and number of samples. It also uses the data stored in the DMA memory to calculate the average and root-mean-square (rms) values for the current and voltage input signals.

## 2.3. Hardware Overview<sup>1</sup>

This section describes the hardware used in the NBS wideband sampling wattmeter and the associated circuits to the block diagram level. A more detailed discussion of the various circuits is given in chapter 5, and a complete set of schematics is provided in appendix A.

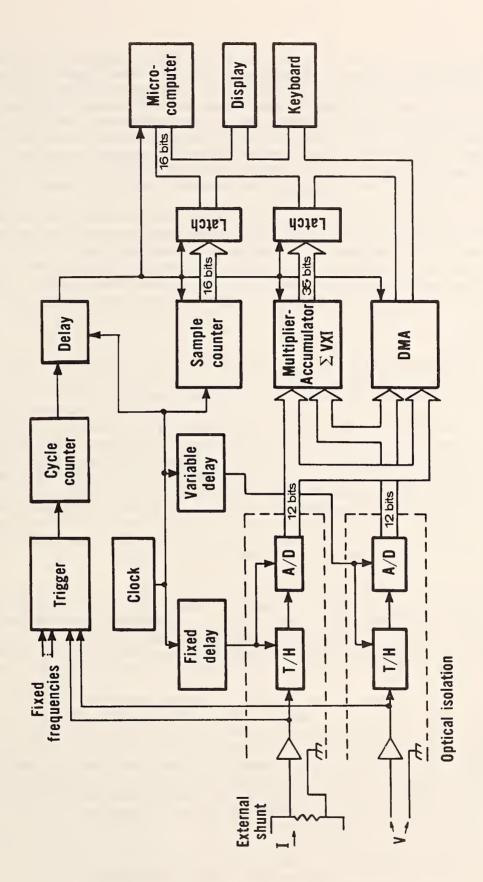

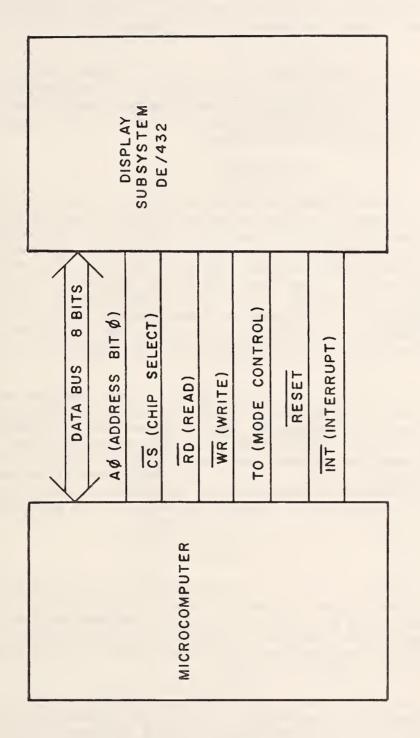

A more detailed block diagram of the NBS sampling wattmeter is shown in figure 2.3.1. The input signal conditioning units consist of a variable gain amplifier, track-and-hold (T/H) unit, and a 12-bit analog-to-digital (A/D) converter. These units have six ranges which accept input signals with a peak amplitude of from  $\pm$  125 mV to  $\pm$  5 V. This input circuitry is optically isolated from the remainder of the system as indicated by the dashed lines in figure 2.3.1. This optical isolation ensures that the sampling wattmeter will not introduce ground loops into the measuring circuit.

The convert command signals, which initiate the data conversion process for the two input modules, are derived from a crystal controlled clock. The convert command signal can be set to rates of from 2.344 kHz to 300 kHz. The convert command signal passes though two programmable delay units which allows for a differential delay between the two signal channels of from -60 ns to +195 ns in one ns steps. The delay is used to compensate for the differential time delay between the two input amplifiers and can be used also, to compensate for any external differential time delays. The significance of this compensation can be illustrated by considering the potential errors from differential time delays. If the system is measuring a 10 kHz power signal at half-power-factor, i.e., a phase angle of 60°, then a differential time delay of only 18 ns will cause an error of  $\pm$  0.2 percent of the true power value. The differential time delay of the input amplifiers can be as large as 44 ns when set on different gains. Thus, without the ability to set differential time delays, the resulting error could be almost 0.5 percent for a half-powerfactor signal.

The summation interval control is accomplished by the four blocks labeled trigger, cycle counter, delay, and sample counter in figure 2.3.1. An analog multiplexer in the trigger circuit allows selection of one of four fixed

<sup>&</sup>lt;sup>1</sup> This technical note reports on equipment developed at the National Bureau of Standards. Certain commercial components are identified in this paper in order to adequately describe the design and operation of the equipment. Such identification does not imply recommendation or endorsement by the National Bureau of Standards, nor does it imply that the components are necessarily the best available for the purpose.

frequencies or a signal from either of the input channels. The choice of fixed frequencies allows the wattmeter to measure dc inputs. This ability is useful in calibrating the gain and offsets of the input modules. A filter option on the signals from the input modules (not shown in figure 2.3.1) also allows for clean triggering on a variety of input waveforms. The trigger level is programmable so that reliable triggering can be obtained on complex waveforms. The delay circuit synchronizes the trigger event with sample times and allows for a programmable delay in units of sample periods. This delay allows control of the phase angle at the start of the summation interval  $\alpha$ which was discussed in section 2.1.1 above. The cycle counter determines the summation interval in units of input signal cycles while the sample counter determines the number of samples taken during each summation interval. The start and stop time for each summation interval is determined by the signal out of the cycle counter and delay circuits which indicates that the programmed number of cycles has been registered. This signal is used to strobe the data out of the sample counter, to strobe the data out of the multiplier-accumulator, to trigger the DMA, and to interrupt the microcomputer.

The digitized voltage and current values are multiplied and summed by the high speed multiplier-accumulator circuit. Although this circuit is presently multiplying two 12-bit numbers at up to 300 thousand products per second, the circuit is capable of multiplying two 16-bit numbers at a rate of one million products per second. This added capability is provided to accommodate improved amplifier/data converter modules in the future. The accumulator has a capacity of 35-bits which limits the number of products that can be summed without overflow. For full scale dc signals the limit is 4096 samples, whereas for a full scale sine wave the limit is 8192 samples. This summation limit can be software extended to allow for a total accumulation of over a million samples. The sample count and product accumulation data are strobed into latches, and the multiplier-accumulator circuits are cleared in time to respond to the next data sample. Thus, the software-extended summation interval is provided without any loss of data.

The digitized voltage and current values are also directed to the direct-memory-access (DMA) unit. This unit stores up to 4096 samples of both channels. Since the DMA unit is started with the same signal that strobes the sample counter and multiplier-accumulator, the data that is stored is synchronized with the same starting phase angle as the product data.

The microcomputer is a commercial (Intel SDK-86) single-board, 16-bit computer with 4k bytes of random-access-memory (RAM). The SDK-86 board utilizes the Intel 8086 microprocessor central processing unit (CPU) chip. A priority interrupt controller and a Multibus<sup>2</sup> interface have been added to this basic microcomputer. The software operating system is stored on a commercial programmable read only memory (PROM) board plugged into the Multibus. Presently only 24k of the available 64k bytes of memory space is being used to hold the system software (i.e., firmware).

2

Multibus is a trademark of Intel Corporation.

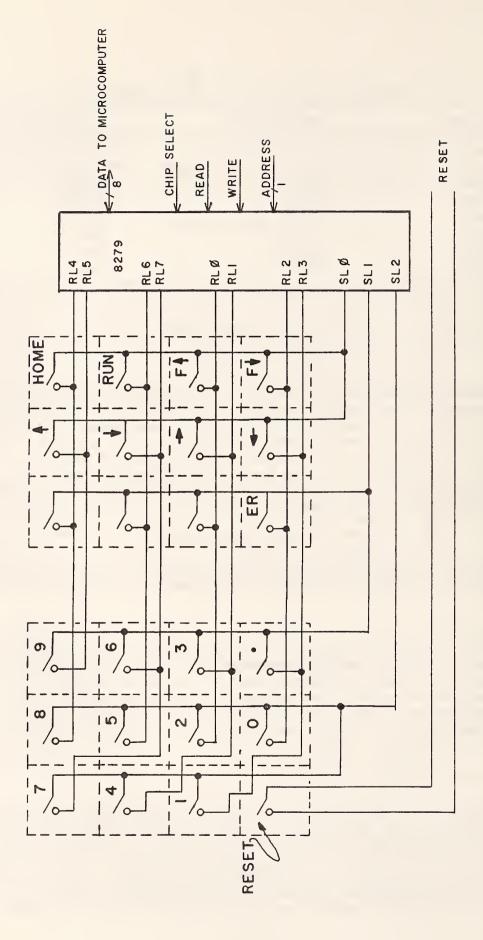

The operator interface is via a 32-character alphanumeric display and two 12-key keyboards located on the front of the sampling wattmeter enclosure. The display is interfaced directly with the Multibus as two read-and-write addresses in the I/O space of the microcomputer. The keyboards are connected to the Multibus via a keyboard interface chip which performs the keyboard scanning function and buffers up to eight keystrokes. This chip provides an interrupt to the microcomputer when a key action is sensed. Twenty-three of the keys are connected to this interface chip while the last key (Reset) is directly wired to the reset line on the microcomputer.

The sampling wattmeter is entirely housed in a rack 27 inches high by 19.5 inches wide by 25 inches deep. The major parts of the system electronics are built on four circuit cards which conform to the Multibus I interconnection specification. These cards are mounted in a commercial Multibus cage. One of the cards is the commercial PROM board and the other three are cards made at NBS using wire wrap connections.

The SDK-86 microcomputer board is mounted above the card cage. It is connected to the other boards via a specially designed SDK-86 to Multibus I interface. The reason for using this approach instead of a commercial microcomputer card mounted in the Multibus cage is because the SDK-86 board provided for convenient prototype development. A current design would make use of an integrated Multibus microcomputer card.

The input signal conditioning is accomplished by two identical amplifier/data converter modules mounted below the card cage. These units plug into the system via a 44-pin connector. The display and keyboards are mounted on panels in the front of the enclosure and are connected via cables to one of the NBS-developed Multibus cards. The power supplies are mounted behind the card cage.

## 2.4. Software Overview

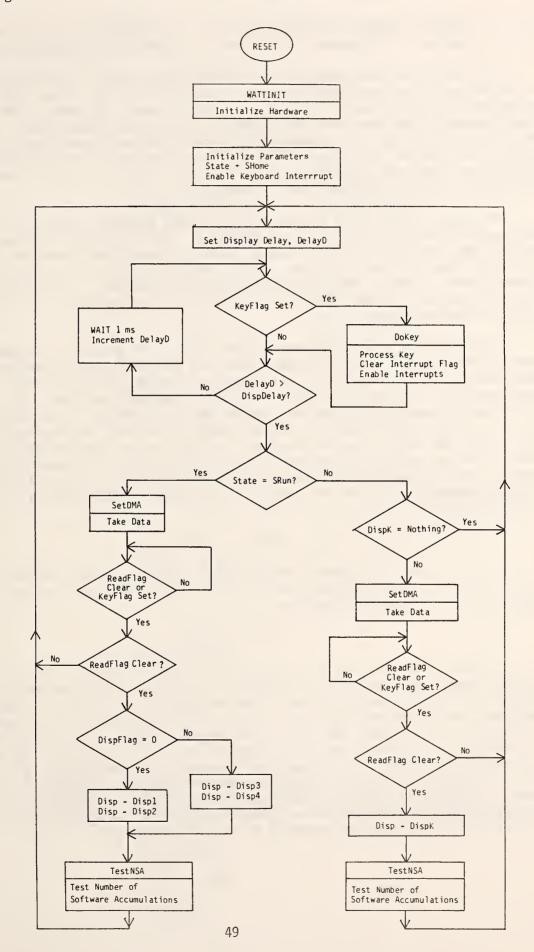

The operating system software for the sampling wattmeter is contained in the PROMs within the instrument. Most of this software is compiled from Pascal into native microprocessor code. These routines are interfaced with the hardware of the wattmeter via assembly language driver routines. Hardware interrupts synchronize the hardware functions with the software operation. The Pascal and assembly language routines are summarized below and described in more detail in section 6.

## 2.4.1. Pascal Routines

The main control program first initializes the hardware and software to the startup default values, enables the keyboard interrupt, then goes into an infinite loop. Program execution in the loop first waits for the specified display delay, starts the measurements sequence, and then calls the appropriate subroutine which calculates and displays the measured values. At the end of each loop the number of sample products accumulated in hardware is checked and adjusted, if necessary. Since this number is controlled by a counter which counts input signal cycles, the number of samples accumulated gives a way to determine the frequency of the input signal. The number of hardware accumulations must be kept within certain limits. If the number is too small, then the hardware results will come faster than the microcomputer can handle, resulting in lost data. Also, if the number of hardware accumulations is too high, then the hardware accumulator will overflow, again causing a loss of data. This automatic updating at the end of each pass through the loop allows the wattmeter to track changes in signal frequency.

The keyboard monitor routine uses the operator key entries to change the state of the wattmeter; then, depending on the current state, sends the key entries to the appropriate subroutines to change the wattmeter operating parameters. The remaining Pascal routines include the display and parameter changing subroutines mentioned above and a display routine to output Pascal floating point numbers in engineering notation.

2.5. Specifications

The following specifications describe the input characteristics of the two channels of the wideband sampling wattmeter and the accuracy of the power measurements.

Input ranges in peak voltage: ± 0.125, ± 0.25, ± 0.5, ± 1.25, ± 2.5, ± 5.

Input impedance: 100 k $\Omega$  and 47 pF.

Common mode isolation: 300 pF to ground.

Accuracy of ranges 0.5 to 5,

dc, 10 Hz to 10 kHz: ± 0.1 %, 10 kHz to 100 kHz: ± 0.5 %.

Accuracy of ranges 0.1 and 0.2,

dc, 10 Hz to 10 kHz: ± 0.2 %, 10 kHz to 100 kHz: ± 1 %.

3. OPERATING THE SAMPLING WATTMETER

3.1. Keypad Control and Display

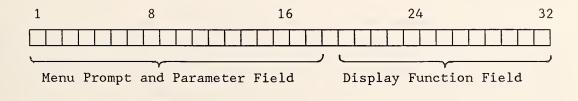

The operator interface of the NBS wideband sampling wattmeter consists of a 32-character display and two 12 button keypads each arranged as a three by four matrix. Figures 3.1.1 and 3.1.2 show the keypads and display, respectively.

| 7     | 8 | 9 | (blank) | t |

|-------|---|---|---------|---|

| 4     | 5 | 6 | (blank) | ţ |

| 1     | 2 | 3 | (blank) | ← |

| Reset | 0 | • | ER      | ÷ |

Figure 3.1.1 Control Keypads

Home

Run

Ft

F↓

Rather than having an individual key select each function that the operator wants to examine or change, the sampling wattmeter uses a menu approach with direction or arrow keys to step through the menu. The operator interface software controls the sequence of menu items displayed, based on the operator inputs. This software has two modes of operation called "Home" and "Run". The Home mode is used to enter operating parameters and to view a single function. The Run mode is used to display up to four measured functions.

When the system is first powered on, the Reset key (located on the left keypad) must be activated to start the microcomputer. This causes the system to initialize all the various interfaces using the default parameters and to set the operator interface to the Home mode. These default parameters will be described below as each parameter is described. While in the Home mode, the first 18 characters of the display are used to display the menu prompt and the parameter value. Simultaneously, the display field of characters 20 through 32 is used to display one of the measured functions. The first field is called the parameter setting field and the second is called the display function field.

Table 3.1.1 shows the sequence of prompts that appear on the display in response to the arrow keys. The up and down arrow keys  $(\uparrow, \downarrow)$  move vertically through the prompts and the left and right arrow keys ( $\leftarrow$ ,  $\rightarrow$ ) move horizontally between the three columns. The arrow keys are located in the center column of the right hand keypad. Within the software is a menu pointer called "State" that moves through the menu in response to key inputs. The value of this variable "State" determines what is shown on the display and the response to the next key entry. When the Home mode is first entered, either by pressing the Reset key or the Home key, the menu pointer is set to the "Top of List" location, so that the parameter-setting field will display "Top of List". From here successive activations of the down arrow will move the menu pointer to Sample Pulse; Synchronization, Integration Period, Scale Factors, Display, and finally DMA Parameters, with the corresponding message displayed in the function display field. Another activation of the down arrow brings the pointer back up to Sample Pulse; thus, the list is actually a circular list. The up arrow can be used to move along the loop in the reverse direction. From location Sample Pulse, pressing the right arrow moves the pointer to Sample Freq, and the display shows "Smp Frq = 300 kHz", where 300 kHz is the default value for the sample rate. Activation of the down arrow gives displays of "Pls Wdt = 1000 ns", "Conv Dly = 1 ns", and back to "Smp Frq = 300 kHz", so this is also a circular list. To move to the Multiplexer, which selects the signal which controls the summation intervals requires pressing a left arrow, down arrow, and right arrow with successive displays being "Sample Pulse", "Synchronization", and finally, "Mplx = 4.688 kHz". Movement around the rest of the menu is accomplished in a similar manner. From each of the subloops a right arrow moves the pointer into the data field which enables changing of the parameters. However, before these operations are described, it will be useful to examine the operation of the display function field, since observing the values of functions in this field provides useful feedback while setting many of the system parameters.

Table 3.1.1 Parameter Selection Menu and Default Values

Top of List

| Sample Pulse    | Sample Freq.<br>Pulse Width<br>Conv Cmd Delay                     | 300 kHz<br>1.00 µs<br>0 ns                                   |

|-----------------|-------------------------------------------------------------------|--------------------------------------------------------------|

| Synchronization | Multiplexer<br>Trigger Level<br>Trigger Delay                     | 4.68 kHz<br>2.0 V<br>1 sample                                |

| Integration     | Lock Mode<br>Integration Per.                                     | 16 cycle                                                     |

| Scale Factor    | Shunt Res.<br>Ch 1 Gain<br>Ch 2 Gain<br>Approx Freq.              | 1.0<br>1.0<br>1.0<br>1000                                    |

| Display         | Display Delay<br>Display 1<br>Display 2<br>Display 3<br>Display 4 | 1000 ms<br>Power<br>Number of Samples<br>Frequency<br>Period |

| DMA Parameter   | DMA Trigger<br>DMA Trancation<br>DMA Ave                          | TC<br>None<br>(Blank)                                        |

The two keys labeled Ft and F4 are used to control the display function field. This field displays one of the 12 measurement values, or a blank display, see table 3.1.2. Using the Ft and F4 keys moves the function pointer in software much the same as the menu pointer described above. Table 3.1.2 represents the sequence of functions that will be calculated and the code letters which will appear on the display to identify the numeric data. Table 3.1.3 shows the codes as they appear on the display and the default values assigned at reset.

An appropriate measurement function can be displayed while the parameter values are changed. For example, while setting the summation interval of the sampling wattmeter, which is done in terms of cycles of the incoming signal, the number of samples that are taken in this period can be displayed. To reduce the effects of quantization and other types of noise, the number of samples should be high without introducing excessive measurement delay. Also, to take full advantage of the DMA memory for measuring the average and rms value of each channel, the number of samples should be set to greater than 4096 samples.

Now back to how the parameter values are changed. The parameter values are set using one of three methods. Some parameters have a small fixed set of parameter values and they are set by stepping through the fixed sequence of values. For example, the synchronization source can be set to one of four fixed frequencies or to either input channel. With each input channel signal a filter can be included or not. Thus, this parameter is set by stepping through the eight possible settings. Secondly, some parameters which require a numeric entry, are set by incrementing or decrementing digits of these numbers. The summation interval is set using this method. The number can be incremented or decremented in the units, tens, hundreds, thousands, or ten thousands place. The final method used to set parameters is to enter the various scale factors. In this case, each entry requires the number to be entered using the left numeric keypad. The exponent of the entered number can be changed using the up and down arrow keys. Thus, for example, to enter a value of one milliohm for the shunt resistance, the operator selects the shunt scale factor display location using the arrow keys. Pressing the right arrow key blanks the numeric field and allows numeric entry. Enter 1.0 on the numeric keys, then press the down arrow once. This last step reduces the exponent by a factor of 1000 so the display shows 1.0 m, which is the desired value of one milliohm.

## 3.2. Parameter Ranges

The setting and significance of each of the sampling wattmeter operating parameters is described in this section:

<u>Sample Rate</u> - A frequency which is adjustable by powers of 2 from 2.34375 kHz to 300.0 kHz. The value of this parameter determines the sampling rate for the wattmeter. Note that when measuring input signals below 80 Hz the sampling rate must be less than 300 kHz to prevent overflow of the hardware accumulator.

Pulse Width - A time interval which is adjustable from 0.333 µs to 2.666 µs by

## Table 3.1.2 Function Displays

| Function                    | <u>Display Code</u> |

|-----------------------------|---------------------|

| Nothing                     | (Blank Display)     |

| Power                       | P=                  |

| Frequency                   | F=                  |

| Number of Samples           | SN=                 |

| Period                      | Pe=                 |

| Average of Channel 1        | Avl=                |

| RMS of Channel 1            | Rm1=                |

| Average of Channel 2        | Av2=                |

| RMS of Channel 2            | Rm2=                |

| Decimal Count               | Dec2=               |

| Trigger Count               | TrC=                |

| Channel 1 Correlation Count | C1C=                |

| Channel 2 Correlation Count | C2C=                |

## Table 3.1.3 Display Codes

Top of List SAMPLE PULSE Smp Frq = 300.0 kHzPls Wdt = 1000.0 ns Conv Dly = 0 nsMplx = 4.688 kHzSYNCHRONIZATION Trg L = 0.0 mVTrg Dly = 1 smINTEGRATION PERIOD LOCK MODE - NIY (Not Implemented Yet) Int Per = 32 cyShuntR = 1.000000SCALE FACTORS Ch1 SF = 2.441406 mCh2 SF = 2.441406 mApprox F = 1.00000kDISPLAY Disp D = 1000 msDisp1 = Power Disp2 = Smp Num Disp3 = Freq Disp4 = Period DMA PARAMETERS DMA Trg S = TCDMA Trunc = none DMA Ave

steps of 0.333  $\mu$ s. This parameter sets the hold time for the track-and-hold unit. Note that for the present input amplifier/data converter modules this value must be set at 1.0  $\mu$ s or greater.

<u>Converter Delay</u> - A time interval which is adjustable from -60 to 195 ns by steps of 1 ns. This parameter adjusts the differential time delay between the two input channels and is used to compensate for both internal and external differential time delays. Table 6.1.1 gives the recommended settings for the present input amplifier/data converter modules.

<u>Multiplex Source</u> - This parameter selects one of eight synchronization signals. Four are internally generated fixed frequencies of 2.344 kHz, 4.688 kHz, 18.75 kHz, or 75.00 kHz. The other four are one of the input channel signals with a low pass filter of either 1.5 kHz or 15 kHz.

<u>Trigger Level</u> - A voltage level which is adjustable from -5.000 to 4.961 V by steps of either 625 mV or 39.06 mV. This parameter sets the reference level which the comparator uses to trigger on the selected synchronization signal. For internal fixed frequencies this level is automatically set to about 2.0 V to be compatible with the internal TTL levels.

<u>Trigger Delay</u> - An adjustable delay from 1 to 65,535 samples in steps of 1 sample. This parameter sets a delay between the trigger event and the start of the summation interval. This feature allows the trigger event to be placed at a reliable, rapidly-rising part of the input signal and, yet, to start and stop the summation interval at another phase of the input signal.

Lock Mode - A planned feature that has not been implemented. The hardware was developed but the software was not. The presently implemented approach for locking to the input signal using the trigger circuit has worked so well with all signals that no need exists for implementing an alternate approach.

<u>Intergration Period</u> - An adjustable interval from 2 to about 99,000 cycles of the incoming signal. This parameter sets the summation interval for calculating the power in terms of the number of cycles of the incoming signal. The values are selected by incrementing or decrementing the units, tens, hundreds, thousands, or ten thousands place. The actual increment will depend on the resolution allowed by the hardware. Since the number of samples which can be accumulated in hardware is limited, as described in section 2.2, long sumation intervals require accumulations in software of hardware results. Thus, the summation interval will be incremented in multiples of the number of cycles over which the hardware accumulator is integrating.

<u>Shunt Resistance</u> - A seven-digit floating-point constant for the shunt resistance, which is used to convert the accumulated product value to true power.

<u>Channel 1 Scale Factor</u> - A seven-digit floating-point constant for the gain of channel one, which is used to change the results from the A/D converter to physical units such as volts or amperes. The default value represents an input range of  $\pm$  5 V full scale.

Channel 2 Scale Factor - Same as above for channel two.

Approximate Frequency - Unused parameter.

<u>Display Delay</u> - An adjustable delay from 1 to 32,767 ms in steps of 1 ms, which is used to specify a delay in the update rate for the display. This allows easy reading of the function values while using short summation intervals.

<u>Display 1 to 4</u> - These four parameters specify the four functions that will be displayed in the Run mode. The display will show two quantities at a time, either the functions specified by Display 1 and 2 or those specified by Display 3 and 4. The F<sup> $\dagger$ </sup> or F<sup> $\ddagger$ </sup> keys will toggle between these two choices.

<u>DMA Trigger Source</u> - The selection of this parameter value determines which of two signals is used to start and stop the summation interval and the DMA module. TC coincides with the sample following the trigger event and FC is delayed from TC by the number of samples specified by the trigger delay parameter.

<u>DMA Truncation Correction Source</u> - The selection of a value for this parameter determines the method used to measure the fraction of a sample needed to make the truncation correction calculation. The choices for this parameter are "no correction", calculate correction from the trigger count, or do a correlation-like fit to data in the DMA memory using either channel one data or channel two data.

DMA Ave - Unused parameter.

#### 4. HARDWARE

## 4.1. Amplifier/Data Converter Module

The amplifier/data converter unit provides the necessary voltage gain and impedance transformation of input signals for conversion within the unit into a 12-bit, parallel binary code. A front-panel range switch permits selection of full-scale input range levels from 125 mV to 5 V. The input impedance is 100 k $\Omega$  in parallel with 47 pF. The two channels of the wattmeter employ identical amplifier/data converter units which are each housed in a plug-in module assembly, thereby permitting easy replacement with updated versions. Generally in power measurement applications, the signal levels in each channel may differ significantly in amplitude. In other words, the "potential" channel may be several hundred volts and the "current" channel may be in the millivolt range from the voltage drop across a resistive current shunt. These wide differences in amplitude for each channel generally require attenuation for the "potential" channel and amplification for the "current" channel. However, the decision was made to design the instrument as a general purpose, dual channel signal analyzer with two identical signal conditioning channels that can be used for other applications as well as power measurement. A further advantage of employing identical signal conditioning units for each channel is the inherent minimization of any differential phase or time delay

between channels. For small differential delays, the instrument contains a programmable differential delay compensation system. This compensation system is discussed in section 4.3. For voltage levels above 5 V, the range can be extended up to 500 V for either channel by means of an external attenuator specially designed for use with the amplifier/data converter module.

The amplifier/data converter unit features a floating input common which permits measurement of signals riding on common mode signals referenced to ground as high as 500 V. The floating input circuit is achieved by optical isolators and dc to dc power converters. This floating feature reduces ground loop errors and permits measurement of small voltages from a resistive 4-terminal shunt not referenced to a common ground potential. Outputs are an isolated analog signal used to trigger the summation interval control circuitry and a 12-bit binary number used to compute the power and other measured quantities.

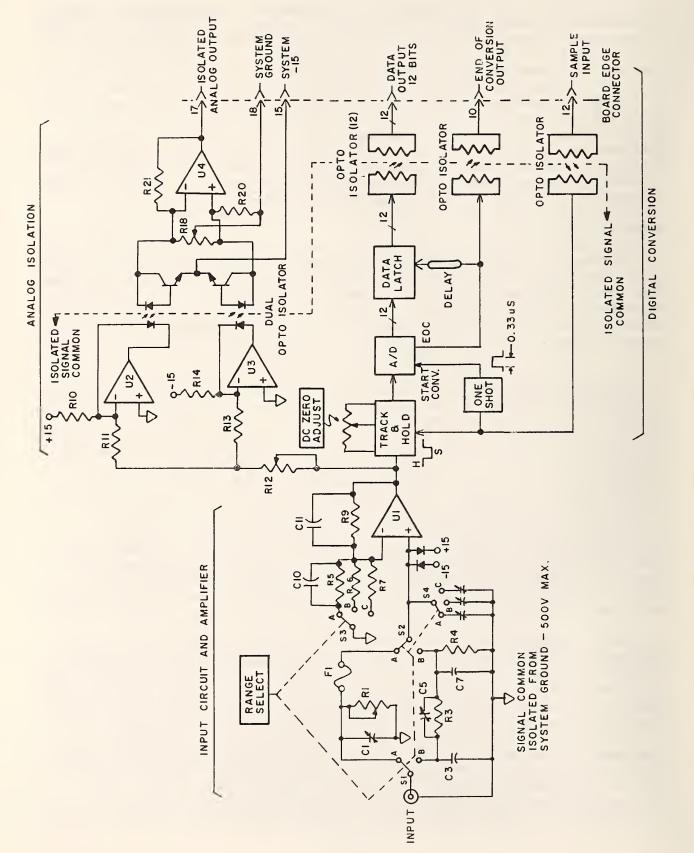

Figure 4.1.1 shows a simplified schematic of the amplifier/data converter unit. For discussion purposes, the unit can be broken into three major parts: the input circuit and amplifier, the analog isolation circuit, and the digital conversion and output isolators. Following the description of these three parts is a section describing common mode voltage considerations.

## 4.1.1. Input Circuit and Amplifier

The input signal is coupled to the unit through a BNC connector that has its outer shell insulated from the system ground but connected to the floating common of the circuitry. Range selection is executed by switches S1, S2, and S3 each of which is one deck of a ganged wafer switch. When switches S1 and S2 are in the A position the signal is connected directly to the noninverting input of amplifier U1. The amplifier provides three selectable voltage gain levels of 40, 20, or 10 by respective connections of R5, R6, or R7 to the signal common by switch S3. When switches S1 and S2 are in the B position the input signal is attenuated by a factor of 10 by means of a compensated attenuator formed by R3, C5 and R4, C7. With the attenuator switched in, three additional selectable voltage gains of 4, 2, or 1 are available, thus providing a total of six gains ranging from 1 to 40 in a 1, 2, 4 sequence. Since the track-and-hold amplifier has a gain of one, and the analog-todigital converter requires a 5-V level, the full scale input voltage for each range is as follows: 0.125, 0.25, 0.5, 1.25, 2.5, 5 V.

The attenuator is compensated by capacitors C5 and C7 and the frequency response is adjusted by trimmer capacitor C5. However, the practicality of obtaining a frequency response for the attenuator that is flat to better than 0.025 percent out to 100 kHz with a resistance of 1 MΩ requires high quality resistors and capacitors with dissipation factors in the order of  $10^{-4}$ . The greatest errors or aberrations in the frequency response for this type of attenuator occur around the "crossover" frequency (i.e., the frequency where the capacitative reactance equals the parallel resistance of each arm of the attenuator). To obtain the desired flatness in frequency response around 10 kHz, the "crossover" frequency was designed slightly above 100 kHz. A "crossover" frequency in this region dictates an attenuator resistance of about 100 kΩ (i.e., R3 = 90 kΩ and R4 = 10 kΩ) because of restrictions imposed

by practical values of capacitance for C5. Because the input impedance of amplifier U1 contributes primarily a capacitive load, which changes slightly for different gain settings of the attenuator, additional compensation is provided by three trimmer capacitors which are switched in synchronism with S3 by S4. Three capacitors are adjusted to obtain the best overall flat frequency response for all gain settings of the amplifier. When the range switch is set so that the input is connected directly to the amplifier, a fuse in conjunction with two clamping diodes protect the amplifier against an inadvertent overload voltage. Capacitor C1 and R1 are adjusted to obtain the same input impedance when switches S1 and S2 are in either the A or B position.

## 4.1.2. Analog Isolation

The purpose of the analog isolation circuit is to provide a trigger signal from the floating output of U1 that is referenced to the system ground. Since very high linearity are not required for the trigger signal, optically coupled isolators provide a satisfactory means of direct coupling the floating analog input signal to an output port referenced to the system ground. The analog isolation amplifier uses a matched pair of optically coupled isolators in a differential connection. This system operates on the principle that at a given operating point a gain increment in one optically coupled isolator is approximately balanced by a gain decrement in the second opto-isolator. This technique tends to reduce the total linearity error to a few percent. Amplifiers U2 and U3 are used in a voltage-to-current configuration to forward bias each light-emitting diode at an operating point of 3 mA by means of the 15-V supply and resistors R10 and R14. The signal current into each diode is controlled by resistors R11 and R13, and since the diodes are connected in opposition, the signal causes current to increase in one diode and decrease in the other. The photodetectors of each isolator are connected to U4 which combines the difference in detected currents to produce a ground referenced output signal that is a replica of the input signal (from the output of U1). Resistor R12 is used to trim the overall voltage gain to one. Resistor R18 is adjusted to produce a zero output when the output of U1 is zero.

There are two uses for this analog signal: first, a system-groundreferenced trigger signal is required at the frequency counter board to control the summation interval. A second use is for monitoring signals into the track-and-hold amplifier. Monitoring signals at this point provide the convenience of using a single-ended ground-referenced instrument to observe a signal riding on a common mode voltage and enables a quick means of checking whether a particular signal is within the dynamic range of the A/D converter.

## 4.1.3. Digital Converter and Output Isolators

The digital conversion circuitry converts the analog signal at the output of U1 into a 12-bit, two's complement, binary code. The A/D converter is preceded by a track-and-hold module which upon command makes a fast "acquisition" of the varying analog signal and "holds" this signal level for the duration of the conversion process. The conversion process is started by a sample input pulse which is coupled through an opto-isolator from the frequency counter board. The sample input pulse has a minimum duration of 1  $\mu$ s which is the maximum acquisition time of the track-and-hold module. At the end of the sample input pulse the track-and-hold module "holds" the analog signal. The conversion process in the A/D converter is delayed by approximately 0.3  $\mu$ s to ensure that switching transients from the track-and-hold have settled. The A/D converter requires 2  $\mu$ s to convert the "held" analog signal to a 12-bit word. When the conversion is completed, the A/D converter sends an End of Conversion (EOC) signal which after a short delay causes the data from the A/D converter to be fed to the data latch. The EOC signal is also coupled through an opto-isolator to the multiplier-accumulator to indicate that the data is ready. The total delay required for the 1  $\mu$ s acquisition time, the 0.3  $\mu$ s settling time, and the 2  $\mu$ s conversion time limit the sampling frequency to 300 kHz.

## 4.1.4. Common Mode Voltage Considerations

Significant measurement errors can arise from undesired conversion of common mode signals to normal mode signals. Common mode voltages often appear in noisy environments as potentials between two reference ground terminals because of ground loops. Also, common mode voltages will be present at the potential terminals of a 4-terminal resistance shunt that is used in a power measurement setup.

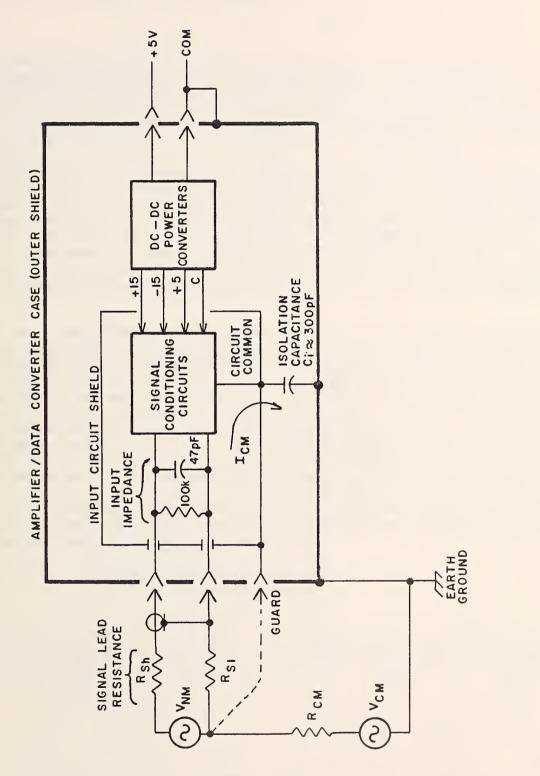

An ideal, floating input, signal conditioning circuit that is perfectly isolated from earth ground (i.e., infinite resistance and zero capacitance) is devoid of any measurement errors from common mode signals. However, a truly infinite isolation impedance is impossible to achieve, and therefore, depending on the applications, the finite isolation impedance, which results from a practical system, must be accommodated. Figure 4.1.2 shows the floating measurement system of the Amplifier/Data Converter Unit. The circuit shows an isolation capacitance  $(C_i)$  from the signal common to ground of about 300 pF. Although not infinite, the isolation resistance in this system can be neglected, and, as will be shown, it is the isolation capacitance which causes the greatest error from high frequency common mode voltages. The bulk of the isolation capacitance is contributed by the dc-to-dc power converters and less than 20 pF by the 16 opto-isolators. As shown in figure 4.1.2 the presence of a common mode voltage  $V_{cm}$  causes a common mode current  $I_{cm}$  to flow through the low-side or signal common lead to ground through the isolation capacitance  $C_i$ . This current will produce a voltage drop across the impedance of the signal lead R<sub>s1</sub> which causes an error in the measurement of the normal mode voltage  $V_{nm}$ . Although there is a component of common mode current that flows through the high-side of the signal lead, it can be neglected because the normal mode input impedance is high compared to R<sub>s1</sub>. Decreasing the normal mode input impedance tends to improve the common mode rejection by equalizing the currents in both signal leads, but the penalty is an increased normal mode loading error. The error voltage developed across  $R_{s1}$  from figure 4.1.2 is

$$E_{sl} = \frac{(V_{cm}) (R_{sl})}{R_{cm} + R_{sl} + \frac{1}{jwC_{i}}}$$

(10)

and for the case where  $(R_{cm} + R_{sl}) \ll \frac{1}{jwC_i}$ , equation 10 becomes

$$E_{sl} = V_{cm} R_{sl} j w C_i .$$

<sup>(11)</sup>

To gain an appreciation of the error that can be caused by the frequency dependent common mode voltage, consider the worst case where the amplifier is set for maximum gain (125 mV range) which will result in an input quantization resolution of 60  $\mu$ V. This means that when a common mode error voltage of at least 60  $\mu$ V is developed across R<sub>sl</sub> a common mode error of one least significant bit (1 LSB) will result.

For example, a 500-V peak, 60-Hz common mode voltage with a signal lead resistance of 0.1  $\Omega$  (including connector contact resistance) will result in an error voltage of about 5  $\mu$ V which is well below the quantization resolution of 60  $\mu$ V; hence, the error can be completely neglected. On the other hand, it is the high frequency common mode signals and noise which become the most troublesome. At higher frequencies the signal lead impedance becomes complex and no longer can be considered all resistive. Thus, for example a 1-V, 1-MHz common mode signal with a 0.1- $\Omega$  signal lead resistance will produce an error voltage of 188  $\mu$ V which is a common mode voltage error equivalent to 3 LSB's.

The errors caused by high frequency common mode voltages can be considerably reduced by connecting a low impedance conductor (i.e., a flat braided wire) from the low-side of the signal source to the guard terminal as shown in figure 4.1.2. If the impedance of this additional circuit is sufficiently low, the common mode current will favor this path, thus, reducing the common mode error voltage drop across  $R_{\rm S1}$ . Measurements on the effectiveness of this technique have shown that the error from a 400-V, 200-kHz common mode signal applied at the low-side of the far end of a 1-m 50- $\Omega$  coax cable terminated in 50  $\Omega$  can be reduced by a factor of 50 with the use of a bypass 2-cm wide braided cable connected from the end of the signal cable to the guard terminal. It is recommended that, when measurements are being made in the presence of high frequency common mode signals, a low impedance conductor be connected to the common mode source and the guard terminal provided on the front of the amplifier/data converter modules.

4.2. Summation Interval Control

#### 4.2.1. Overview

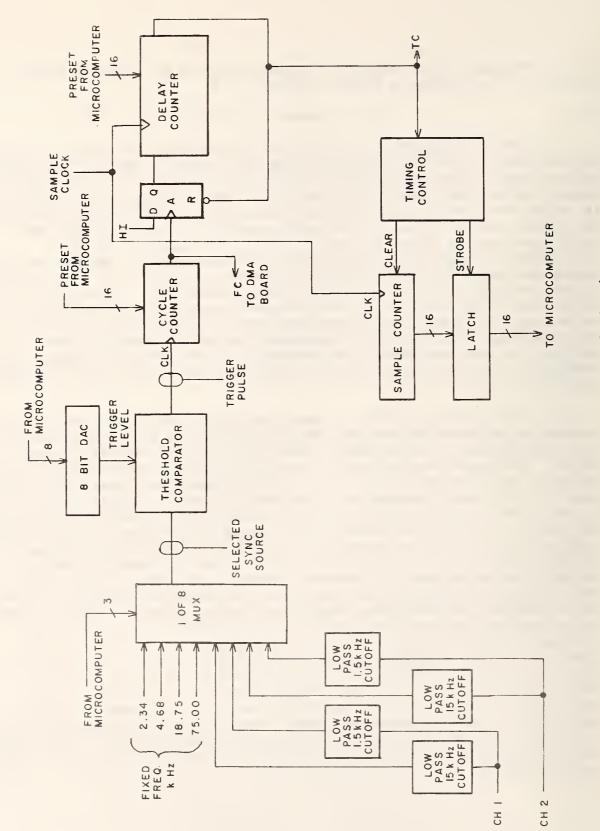

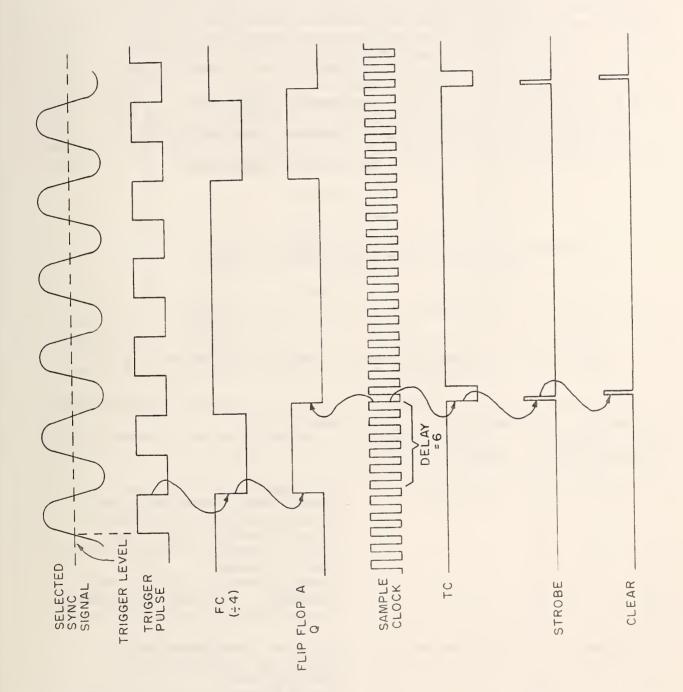

In order to accurately measure the power of an ac signal, the time interval over which the sample data is accumulated must be matched with the period of the input signal. This matching or synchronization function is performed by the summation control circuitry described in this section. The circuitry allows selecting one of eight signals to be used as the synchronizing signal. Through the setting of programmable counters, this circuitry also allows for summation over a variable number of periods, and allows the summation interval to start at a variable phase of the input signal. The time resolution of this matching or synchronization process is the sample interval (reciprocal of the sampling rate). This circuit also counts the number of samples which are taken during each summation interval. A block diagram of this circuitry is shown on figure 4.2.1, and a timing diagram for the signals is given in figure 4.2.2.

## 4.2.2. Circuit Description

The synchronization source can be set to one of the internal (crystal-based) fixed frequencies (75 kHz, 18.8 kHz, 4.7 kHz, 2.3 kHz) when pure dc signals are being measured (and for self-test), or set to either channel for ac input signals. In the latter case, the synchronization signal is derived from the optically isolated signal from either channel one or two. The signals from each channel are conditioned with a low-pass filter with a cutoff frequency of either 1.5 kHz or 15 kHz. The selection of the synchronization signal is accomplished by the microcomputer setting the binary output levels for signals F, C1, and T as shown in table 4.2.1. These control signals are applied to a one-of-eight analog multiplexer. The analog output of this device is then converted to a digital signal via a threshold comparator. The other input to this comparator is connected to an 8-bit D/A converter (DAC) which provides programmable reference levels for the triggering of the comparator. The microcomputer programs the output of the 8-bit DAC to set the trigger level to anywhere in the - 5 V to + 5 V range in 39 mV steps.

The output of the threshold comparator goes to the cycle counter. This counter is programmed to function as a rate generator, providing an output pulse (designated FC for frequency count) after a preset number of input pulses. This preset number is set by the microcomputer and determines the number of cycles of the input signal over which summation takes place. The counter is sixteen bits wide and counts from 2 to 65,535 cycles. This counter is one of three in a programmable counter/timer chip. Table 4.2.2 describes the function of the three counters. The output of the cycle counter, normally high, goes low for one period of the input once the preset count has been reached. The high to low transition of this output latches flip-flop A. The output of the flip-flop then serves as a gate to the delay counter. This counter also has a preset count, set by the microcomputer, which signifies the delay in sample command pulses. The delay counter is also sixteen bits wide and counts from one to 65,535 sample pulse commands. This counter works as a retriggerable one-shot down counter. The output of the delay counter TC (Terminal Count), normally high, goes low for one incoming clock period once the preset count is reached. The Terminal Count pulse resets flip-flop A and starts the timing control circuitry which generates two control signals. The first signal (strobe) latches the parallel output of the sample counter into latches accessible to the microcomputer. The second signal (clear) resets the contents of the sample counter for the next summation interval. This latching and clearing operation takes place within one sample interval, so no sample counts are missed.

Figure 4.2.1 Summation Interval Control Circuitry

Figure 4.2.2 Timing Diagram for Summation Interval Control

Table 4.2.1 Control Signals of Interval Control Source

T = Test Frequency C1 = Channel Control F = Filter Control

| Т | C1 | F | Selected Signal       |

|---|----|---|-----------------------|

| 0 | 0  | 0 | Channel 2 Low Cutoff  |

| 0 | 0  | 1 | Channel 2 High Cutoff |

| 0 | 1  | 0 | Channel 1 Low Cutoff  |

| 0 | 1  | 1 | Channel 1 High Cutoff |

| 1 | 0  | 0 | 2.3 kHz               |

| 1 | 0  | 1 | 4.7 kHz               |

| 1 | 1  | 0 | 18.8 kHz              |

| 1 | 1  | 1 | 75 kHz                |

Table 4.2.2 Programmable Counter Timer Function/Description

| Counter   | Function      | Description                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Counter O | Unused        |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Counter 1 | Delay Counter | <ul> <li>Retriggerable one shot down count</li> <li>Counter starts counting on pos-<br/>itive going edge of data input</li> <li>Output (Terminal Count) goes low<br/>for one incoming clock period when<br/>count is reached</li> <li>Counts between 1 to 65,535 sample<br/>intervals. Sets start of summation<br/>interval relative to trigger event</li> </ul> |  |  |  |

| Counter 2 | Cycle Counter | <ul> <li>Continuous rate generator</li> <li>Output low for one period of<br/>incoming clock</li> <li>Counts between 2 to 65,535 cycles<br/>of the selection interval control<br/>signal.</li> </ul>                                                                                                                                                              |  |  |  |

# 4.3. Differential Time Delay

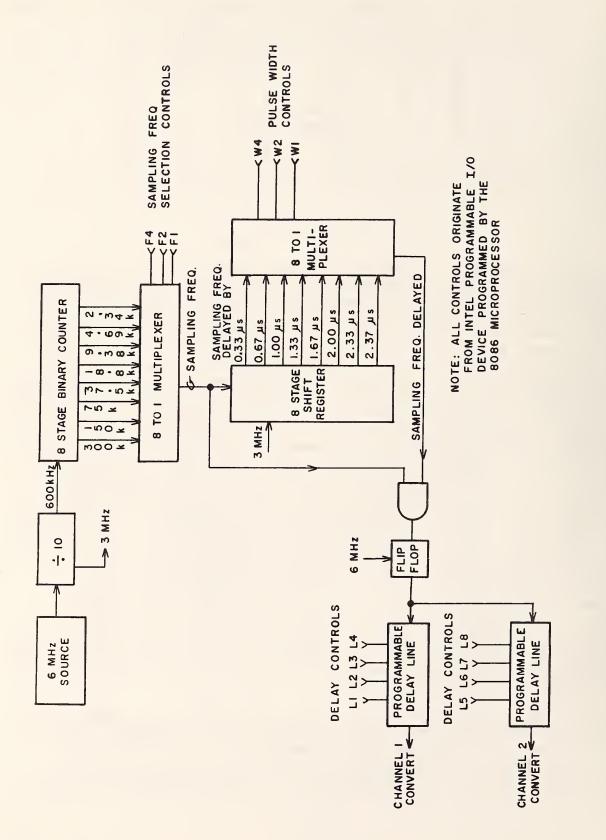

# 4.3.1. Overview