## NBS SPECIAL PUBLICATION 401

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

Computer Performance Evaluation

## NATIONAL BUREAU OF STANDARDS

The National Bureau of Standards was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of a Center for Radiation Research, an Office of Measurement Services and the following divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Nuclear Sciences <sup>2</sup> — Applied Radiation <sup>2</sup> — Quantum Electronics <sup>3</sup> — Electromagnetics <sup>3</sup> — Time and Frequency <sup>3</sup> — Laboratory Astrophysics <sup>2</sup> — Cryogenics <sup>3</sup>.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry.

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services to promote the use of available technology and to facilitate technological innovation in industry and Government; cooperates with public and private organizations leading to the development of technological standards (including mandatory safety standards), codes and methods of test; and provides technical advice and services to Government agencies upon request. The Institute consists of a Center for Building Technology and the following divisions and offices:

Engineering and Product Standards — Weights and Measures — Invention and Innovation — Product Evaluation Technology — Electronic Technology — Technical Analysis — Measurement Engineering — Structures, Materials, and Life Safety — Building Environment — Technical Evaluation and Application — Fire Technology.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical services designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the selection, acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the executive branch for the development of Federal standards for automatic data processing equipment, techniques, and computer languages. The Institute consists of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific information generated within NBS and other agencies of the Federal Government; promotes the development of the National Standard Reference Data System and a system of information analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate services to ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of the following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Library — Office of International Relations.

<sup>&</sup>lt;sup>1</sup> Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

<sup>&</sup>lt;sup>2</sup> Part of the Center for Radiation Research.

<sup>3</sup> Located at Boulder, Colorado 80302.

<sup>4</sup> Part of the Center for Building Technology.

# **Computer Performance Evaluation**

Proceedings of the Eighth Meeting of Computer Performance Evaluation Users Group [CPEUG]

Sponsored by United States Army Computer Systems Command

and

Institute for Computer Sciences and Technology National Bureau of Standards Washington, D.C. 20234

Edited by

Dr. Harold Joseph Highland

State University Agricultural and Technical College at Farmingdale New York 11735

U.S. DEPARTMENT OF COMMERCE, Frederick B. Dent, Secretary NATIONAL BUREAU OF STANDARDS, Richard W. Roberts, Director

## Library of Congress Cataloging in Publication Data

Computer Performance Evaluation Users Group. Computer performance evaluation.

(NBS Special Publication 401)

"CODEN: XNBSAV."

Sponsored by the U. S. Army Computer Systems Command and the Institute for Computer Sciences and Technology, National Bureau of Standards.

Supt. of Docs. No.: C 13.10:401

1. Electronic digital computers—Evaluation—Congresses. I. Highland, Harold Joseph, ed. II. United States. Army. Computer Systems Command. III. United States. Institute for Computer Sciences and Technology. IV. Title. V. Series: United States. National Bureau of Standards. Special Publication 401.

QC100.U57 No. 401 [QA76.5] 389'.08s

[001.6'4]74-13113

## National Bureau of Standards Special Publication 401

Nat. Bur. Stand. (U.S.), Spec. Publ. 401, 155 pages (Sept. 1974) CODEN: XNBSAV

> U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1974

#### FOREWORD

As part of the Federal Information Processing Standards Program, the Institute for Computer Sciences and Technology of the National Bureau of Standards sponsors the Federal Information Processing Standards Coordinating and Advisory Committee (FIPSCAC) and a series of Federal Information Processing Standards (FIPS) Task Groups. The Task Groups are composed of representatives of Federal departments and agencies, and in some cases of representatives from the private sector as well. Their purpose is to advise NBS on specific subjects relating to Information Processing Standards.

One of the Task Groups is FIPS Task Group 10 - Computer Component and Systems Performance Evaluation. Among FIPS Task Group 10's other responsibilities is to sponsor a self-governing Computer Performance Evaluation User's Group (CPEUG) whose purpose is to disseminate improved techniques in performance evaluation through liaison among vendors and Federal ADPE users, to provide a forum for performance evaluation experiences and proposed applications, and to encourage improvements and standardization in the tools and techniques of computer performance evaluation.

With this volume, the proceedings of the CPEUG are for the first time being made available in a form that is readily accessible not only to Federal agencies but to the general public as well. This is in recognition of the fact that computer performance evaluation is important not only for Federal ADP installations but also for those of the private sector.

It is expected, therefore, that this volume will be useful in improving ADP management through the use of performance evaluation in both the private and public sectors.

Acknowledgement is made of the assistance of Dr. Joseph 0. Harrison, Jr., Chairman of the FIPSCAC, and Captain Michael F. Morris, USAF, Chairman of FIPS Task Group 10, in promoting and producing this volume.

Ruth M. Davis, Ph.D., Director Institute for Computer Sciences and Technology National Bureau of Standards U. S. Department of Commerce

#### ABSTRACT

The Eighth Meeting of the Computer Performance Evaluation Users Group (CPEUG), sponsored by the United States Army Computer Systems Command and the National Bureau of Standards, was held December 4-7, 1973, at NBS, Gaithersburg. The program chairman for this meeting was Merton J. Batchelder of the U.S. Army Computer Systems Command at Fort Belvoir, Virginia 22060 (CSCS-ATA Stop H-14).

About 150 attendees at this meeting heard the 17 papers presented on computer performance, evaluation and measurement. Among the papers presented were those dealing with hardware and software monitors, workload definition and benchmarking, a report of FIPS Task Force 13, computer scheduling and evaluation in time-sharing as well as MVT environment, human factors in performance analysis, dollar effectiveness in evaluation, simulation techniques in hardware allocation, a FEDSIM status report as well as other related topics.

These proceedings represent a major source in the limited literature on computer performance, evaluation and measurement.

Key words: Computer evaluation; computer performance; computer scheduling; hardware monitors; simulation of computer systems; software monitors; systems design and evaluation; time-sharing systems evaluation

## PREFACE

The evolution and rapid growth of computer performance, evaluation and measurement has been the result of an amalgam of developments in the computer field, namely:

- the growing complexity of modern digital computer systems;

- the refinement of both multiprogramming and multiprocessing capabilities of an increasing number of computer systems;

- the concomitant expansion and complexity of systems programming;

- the accelerated trend toward the establishment of computer networks;

- the myriad of applications programs in business, technical, scientific, industrial and military fields; and

- the emphasis on massive data bases for information retrieval, data analysis, and administrative management.

Prior to proceeding, it is essential to define several basic terms so that the examination is not made in a vacuous environment.

Performance, according to the dictionary, is defined as "an adherence to fulfill, to give a rendition of, to carry out an action or a pattern of behavior."

**Evaluation** is defined as a "determination or the fixing of a value, to estimate or appraise, to state an approximate cost."

Measurement is defined as a "process of measuring, the fixing of suitable bounds, the regulation by a standard."

Computer performance, evaluation and measurement is now vital to the designer, the user and the management-owner of a modern computer system. To some, computer performance, evaluation and measurement is a tool, a marriage of abstract thought and logic combined with the techniques of statistical and quantitative methods. To others, it is a technique with very heavy reliance on modeling and simulation and simultaneously involves features of both classical experimentation and formal analysis. The prob-

lem of exact specification is made the more difficult by the recent birth and development of computer performance, evaluation and measurement as a discipline within computer science.

Among the early practitioners of this discipline were the members of CPEUG [Computer Performance Evaluation Users Group], individuals from many United States Governmental agencies involved in various phases of this field. At about the same time, there were a number of academicians as well as analysts from business and industry working in this area, and this gave rise to the formation within the Association for Computing Machinery of SIGME [Special Interest Group in Measurement and Evaluation] which is currently known as SIGMETRICS.

In its formative period of growth, computer performance, evaluation and measurement has relied heavily upon modeling and simulation. It has been concerned with the design of computer systems as well as the analysis of the behavior of these systems. The analyst, on the one hand, has used simulation to secure detailed information about a system that he has created, or about which his knowledge is On the other hand, the analyst has used simulation to test various hypotheses about the system in an effort to improve its performance. It is a quixotic hope that as this discipline grows it will become more interdisciplinary and involve the work not only of modelers, simulators and statisticians, but also behavioral scientists, economic analysts and management scientists.

Computer performance, evaluation and measurement is replete with benefits for the computer community — the manufacturer of modern electronic processing equipment, the user of that equipment, especially the manager responsible for the complete operations, as well as the purchasers of this equipment. It is capable of providing many urgently needed answers

to problems faced today, such as:

- <u>procurement</u> the evaluation of various <u>proposals</u> for different systems configurations:

- <u>planning</u> determination of the effects of projected future workloads upon an existing or planned system;

- costing detailed information of cost data to users of an existing or planned computer system or network;

- scheduling the allocation of systems resources to the various demands on the system;

- designing how best to design a new or modify an existing system, and how to improve the operation of that system;

- optimization determination of a systems mode to enhance the performance of a portion or of the entire system.

Within this volume are the technical papers presented at the Eighth Meeting of the Computer Performance Evaluation Users Group. The Meeting was sponsored by both the United States Army Computer Systems Command and The Institute for Computer Sciences and Technology of the National Bureau of Standards, and was held December 4th - 7th, 1973 at Gaithersburg, Maryland. Added to these technical papers are other papers which were presented at an earlier meeting of CPEUG but never published.

## Dr. Harold Joseph Highland, Editor

- Chairman, ACM\SIGSIM [Special Interest Group in Modeling and Simulation of the Association for Computing Machinery]

- Chairman, Data Processing Department of the State University Agricultural and Technical College at Farmingdale (New York)

June 1974

## TABLE OF CONTENTS

| * | PREFACE Dr. Harold Joseph Highland, Editor New York State University College at Farmingdale                                                             | , ,  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| * | COMMENTS OF CHAIRMAN, CPEUG John A. Blue Department of Navy, ADPESO                                                                                     | Х    |

| * | COMMENTS OF PROGRAM CHAIRMAN  Merton J. Batchelder  U. S. Army Computer Systems Command                                                                 | ×′i¦ |

| * | KEYNOTE ADDRESS  Brigadier General R. L. Harris  Management Information Systems, U. S. Army                                                             | 1    |

| * | INITIATING COMPUTER PERFORMANCE EVALUATION                                                                                                              |      |

|   | GETTING STARTED IN COMPUTER PERFORMANCE EVALUATION Philip J. Kiviat and Michael F. Morris Federal Computer Performance Evaluation and Simulation Center | 5    |

|   | A METHODOLOGY FOR PERFORMANCE MEASUREMENT Daniel M. Venese The MITRE Corporation                                                                        | 15   |

| * | ACCOUNTING PACKAGES                                                                                                                                     |      |

|   | USE OF SMF DATA FOR PERFORMANCE ANALYSIS AND RESOURCE ACCOUNTING ON IBM LARGE-SCALE COMPUTERS                                                           |      |

|   | Robert E. Betz Boeing Computer Services, Inc                                                                                                            | 23   |

|   | USING SMF AND TFLOW FOR PERFORMANCE ENHANCEMENT James M. Graves                                                                                         |      |

|   | U. S. Army Management Systems Support Agency                                                                                                            | 33   |

| * | SOFTWARE MONITORS                                                                                                                                       |      |

|   | USACSC SOFTWARE COMPUTER SYSTEM PERFORMANCE MONITOR: SHERLOC                                                                                            |      |

|   | Philip Balcom and Gary Cranson                                                                                                                          | 917  |

|   | U. S. Army Computer Systems Command                                                                                                                     | 37   |

## \* BENCHMARKS

|   | BENCHMARK EVALUATION OF OPERATING SYSTEM SOFTWARE: EXPERIMENTS ON IBM'S VS/2 SYSTEM Bruce A. Ketchledge Bell Telephone Laboratories | 45  |

|---|-------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | REPORT ON FIPS TASK GROUP 13 WORKLOAD DEFINITION AND BENCHMARKING David W. Lambert The MITRE Corporation                            | 49  |

| * | HARDWARE MONITORS                                                                                                                   |     |

|   | PERFORMANCE MEASUREMENT AT USACSC Richard Castle U. S. Army Computer Systems Command                                                | 55  |

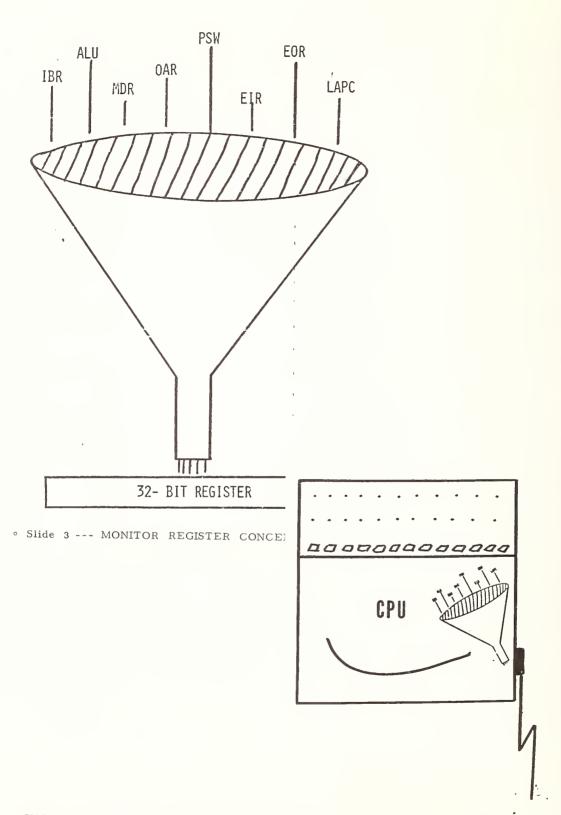

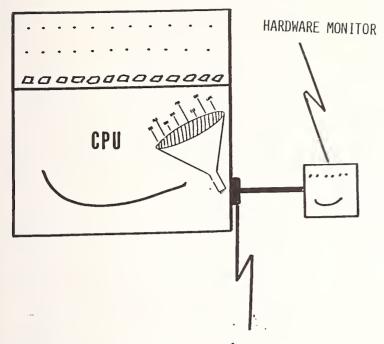

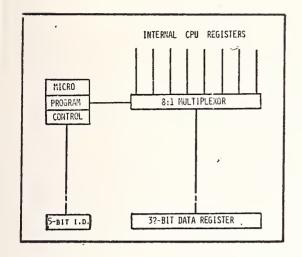

|   | A COMPUTER DESIGN FOR MEASUREMENT THE MONITOR REGISTER CONCEPT                                                                      |     |

|   | Donald R. Deese Federal Computer Performance Evaluation & Simulation Center                                                         | 63  |

| * | SIMULATION                                                                                                                          |     |

|   | THE USE OF SIMULATION IN THE SOLUTION OF HARDWARE ALLOCATION PROBLEMS W. Andrew Hesser USMC Headquarters, U. S. Marine Corps        | 73  |

| * | RELEVANT CONSIDERATIONS                                                                                                             |     |

|   | HUMAN FACTORS IN COMPUTER PERFORMANCE ANALYSES A. C. (Toni) Shetler The Rand Corporation                                            | 81  |

|   | DOLLAR EFFECTIVENESS EVALUATION OF COMPUTING SYSTEMS Leo J. Cohen                                                                   |     |

|   |                                                                                                                                     | 85  |

| k | SPECIFIC EXPERIENCE                                                                                                                 |     |

|   | COMPUTER SCHEDULING IN AN MVT ENVIRONMENT Daniel A. Verbois U. S. Army Materiel Command                                             | 99  |

|   | PERFORMANCE EVALUATION OF TIME SHARING SYSTEMS T. W. Potter Bell Telephone Laboratories                                             | 107 |

|   | A CASE STUDY IN MONITORING THE CDC 6700 - A MULTI - PROGRAMMING, MULTI-PROCESSING, MULTI-MODE SYSTEM                                | ·   |

|   | Dennis M. Conti<br>Naval Weapons Laboratory                                                                                         | 115 |

| * | FEDERAL COMPUTER PERFORMANCE EVALUATION AND SIMULATION CENTER                                                           |     |

|---|-------------------------------------------------------------------------------------------------------------------------|-----|

|   | FEDSIM STATUS REPORT Michael F. Morris and Philip J. Kiviat Federal Computer Performance Evaluation & Simulation Center | 119 |

| * | PREVIOUS MEETING: SPECIAL PAPERS                                                                                        |     |

|   | DATA ANALYSIS TECHNIQUES APPLIED TO PERFORMANCE MEASUREMENT DATA G. P. Learmonth Naval Postgraduate School              | 123 |

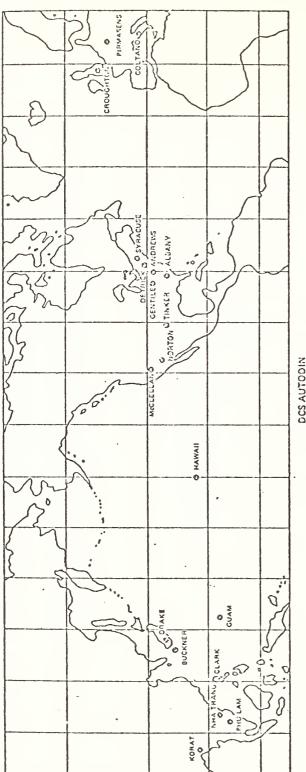

|   | A SIMULATION MODEL OF AN AUTODIN AUTOMATIC SWITCHING CENTER COMMUNICATIONS DATA PROCESSOR LCDR Robert B. McManus        |     |

|   | Naval Postgraduate School                                                                                               | 127 |

| * | ATTENDEES: EIGHTH MEETING OF COMPUTER PERFORMANCE EVALUATION USERS GROUP                                                | 137 |

#### COMMENTS OF CHAIRMAN

#### COMPUTER PERFORMANCE EVALUATION USERS GROUP

This publication provides papers presented at the eighth meeting of the Computer Performance Evaluation Group held at the National Bureau of Standards, sponsored by the United States Army Computer Systems Command and the Institute for Computer Sciences and Technology of the National Bureau of Standards; and some papers presented at the meeting held in March 1973 at Monterey, California, and sponsored by the Naval Postgraduate School.

As the now past chairman of CPEUG, I am very pleased at the qualities of these papers. They provide valuable information on a wide spectrum of computer performance evaluation techniques and tools. The authors deserve a great deal of credit

for the time and effort they have expended on the preparation and presentation of their papers. I thank them very much for making the meetings that I have chaired so successful. I know that with that kind of support, future meetings will be even more interesting and informative. I look forward to having continued contact with all members of CPEUG, and I wish the new officers all the best.

John A. Blue

## COMMENTS OF PROGRAM CHAIRMAN

## EIGHTH MEETING OF

## COMPUTER PERFORMANCE EVALUATION USERS GROUP

I wish to express my appreciation to the members of government, industry and the academic community who contributed their time and resources to make this a highly successful conference.

Brigadier General Richard L. Harris, Director of Management Information Systems for the Army, set the tone of the conference with his keynote address. Authors of the 16 technical papers shared the benefits and problems of their endeavors with Computer Performance Evaluation tools and techniques.

The conference technical program began with an overview of items for consideration when initializing a computer performance evaluation program. This was followed by applications of the CPE tools in order of increasing complexity. Philip Kiviat, Technical Director of the Federal Computer Performance Evaluation and Simulation Center, concluded with a summary of contributions by FEDSIM.

The conference scheduling of a presentation each hour allowed time for questions and participation from the audience. Ample coffee breaks also permitted time to pursue specific CPE problems and discussions and stimulate new ideas.

This exchange of performance evaluation experiences should have widespread effect on our ADP community. Each agency is striving to improve its application of ADP systems. Interchange of experience should continue through contacts with others met at the conference.

Good luck, and let us hear from you.

Mert Batchelder

## COMPUTER PERFORMANCE EVALUATION USERS GROUP

## EIGHTH MEETING HELD 4-7 DECEMBER 1973

## AT NATIONAL BUREAU OF STANDARDS

## GAITHERSBURG, MARYLAND

## Program Committee

Mr. Merton J. Batchelder, Chairman

Mr. John A. Blue

MAJ Richard B. Ensign

Mr. William J. Letendre

Mr. William C. Slater

## CPEUG Officials 1971 - 1973

Mr. John A. Blue, Chairman

Mr. William J. Letendre, Vice Chairman

MAJ Richard B. Ensign, Secretary

## CPEUG Officials 1974 - 1975

Mr. William J. Letendre, Chairman MAJ Richard B. Ensign, Vice Chairman

WAJ KICHARU B. ERSIGII, VICE CHARIMA

Mr. Jules B. DuPeza, Secretary

## KEYNOTE ADDRESS

## Brigadier General R. L. Harris

Director, Management Information Systems, US Army

Good Morning Ladies and Gentlemen:

I am pleased to have a chance to welcome you to this meeting of the Computer Performance Evaluation Users Group. I believe such meetings are most bene-ficial to all users of ADP through the sharing of information on mutual problems and because they provide us the chance to leave our desks and, for a little while, to look at the bigger problems on the horizon. Since becoming the Army's Director of Management Information Systems in July, I have had an opportunity to review some of the history and current philosophy which underlies the Army's approach to the management of ADP. have also discussed with my staff the future trends and areas for exploration over the next five to ten years. I would like to share some of these thoughts with you this morning.

The Army has had a long association with the development and use of digital computers. Initially we used these machines to assist us in processing complex scientific computations and, more recently, our attention has been focused on automating the bread and butter functions---logistics, personnel admin-istration, and financial management. The Army's first interest in digital computers dates back to 1942 when we commissioned the University of Pennsylvania's Moore School of Electrical Engineering to design and produce the electronic numerical integrator and computer (the ENIAC). The installation of the ENIAC in 1947 in the Ballistic Research Labs at Aberdeen, Maryland marked the beginning of the widespread use of electronic computing machines within the Federal Government and the civilian economy as well. ENIAC was closely followed by the installation of our second computer, the EDVAC, or Electronic Discrete Variable Automatic Computer, operational at BRL since 1949. These initial computers were used primarily for solution of ballistic equations, fire control problems, data reduction, and related scientific problems. From these beginnings, the Army expanded its use of both unique and off-the-shelf computers to other scientific and administrative areas, so that by the begin-ning of the sixties, the Army had over 100 computers in its inventory.

During the sixties, the Army expanded its use of ADP at a rate of almost fifteen percent annually. This expansion

was caused by two major factors—the conflict in Southeast Asia and the increas—ing complexity of our weaponry and the personnel skills and logistic base neces—sary to support them. This complexity was the price we had to pay for the greater move, shoot, and communicate equipment of the Army in the field. More importantly, the attendant requirement for faster, more responsive ways of supporting this combat power became quick—ly apparent.

We have, however, been conscious of the need to economize and have made significant gains in our efforts to stem this spiral of ever-increasing ADP costs. Like most of you, we have been helped along by Congress, of course. However, in spite of these efforts, our resource commitment is still significant. We are currently expending more than three hundred and eighty million dollars and nineteen thousand manyears on this effort, while operating almost 950 computers of all shapes and sizes. This commitment to automation has been so pervasive that there is probably no manager at any level within the Army whose decisions are not influenced by the products of our automated systems.

To continue to provide the qualitative support required by today's managers in an era of decreasing resource availability and increasing constraints on flexibility, we all must become better at managing the resources we do have. Our increased management efforts in the Army will fall in three major areas: better planning, better management of systems development, and, lastly, increased productivity in software.

From an organization viewpoint, we shall continue our commitment to the centralization of software development through increased emphasis on the development of standard systems in more functional areas. The benefits which the Army has gained since the establishment of its central design agencies have permitted us to reduce the total number of personnel in ADP by almost one-third while at the same time increasing the qualitative support to managers at our major operating activities. Combined with our centralization efforts is our continuing search for better methods of defining functional requirements. Part of this effort has been to place squarely

in the hands of the functional user the responsibility for determining these requirements and for preparation of the supporting economic justification for undertaking the software development effort.

Better software development is predicated upon better planning methods which can help us to allocate our planned resources to meet new user requirements. Along these lines, we believe that we can no longer sell automation by using subjective arguments. We all recognize that the day of automation for automation's sake has passed. We must now support our requirements with quantitative economic and benefit analyses, as well as workload projections. Use of both of these tools is predicated upon an adequate means of data gathering for predictive purposes. In line with this, one of the current major efforts of my office is to improve our dollar and utilization reporting systems to provide the data we now feel is necessary to help us make these critical resource allocation decisions. One such effort which we have just completed is a hardware requirements projection model called <u>SCORE</u>. This model enables us to project needed upgrades in computer capability dependent upon increasing workload over time.

Turning now to the question of software productivity, it is this area in which we can most benefit from the discussions which will take place over the next four days. Increased productivity will not come from increased or better management alone. Technology will assist us and we in the Army intend to lean on the technologists. In order to do this, however, we will have to increase our management of R&D expenditures in information science. One of the investments we are making is in the area of performance monitors. We are excited about the possibilities inherent in performance monitors, and have been since we first started using them in 1970. We are currently decreasing our operating costs through the use of performance monitors at our central design agencies. Details of these efforts are included in two presentations by the Computer Systems Command. We also have two monitors at our Computer Systems Support and Evaluation Command (our ADPE evaluation and selection command). CSSEC is using these monitors in an ombudsman role to help determine the right hardware configuration to match user processing requirements. We are using the monitors in a number of ways -- no different, I'm sure, than how they are being used by others. We have found the use of these monitors most effective as aids in ADPE configuration balancing and the optimization of data base design.

We are particularly interested in their potential in software optimization. The trend in software development, including systems software, is toward potential use of a higher order language. (UNIVAC, for example, for their new, but unannounced, 1100 system are building most of their compilers and operating system in PL-1). In this environment, monitors are a prerequisite in achieving throughput effectiveness; that is, finding the critical code and optimizing it. We are attempting to build our software in a similar manner. We are still subjected to the argument that software effectiveness can only be achieved through use of an assembly language. I believe that management, ever sensitive to total life cycle costs, will find that the higher level language approach, in conjunction with an effective monitor, will prove the more economic solution for most systems.

I certainly cannot be classified as a computer expert, but it is clear to me that the automation field in this next decade will undergo considerable change. There will certainly be greater emphasis on the computer-communications interrelationship and continued moves toward distributive processing with hierarchies of processing power. Revolutionary changes are on the horizon in software. We all recognize the accelerating cost imbalance between hardware and software. Steps must be taken to redress this imbalance. Software development must move from its present cottage industry stage if it is to continue to exist. The engineers, armed with microprogramming techniques and a well established manufacturing discipline, are a force to be reckoned with. The general purpose offthe-shelf computer as we know it may very well give way in the eighties to microprogrammed special purpose devices capable of solving well defined problems at minimal cost.

What does the software industry need to meet this challenge? From my perspective, it appears to me that the list includes:

- a. A simple management-oriented language for describing automation requirements—a tool which can be placed in the hands of the computer neophyte to enable him to bridge the functional analyst-computer analyst communication gap.

- b. Means of increasing the productivity of our programmers. Many attempts have been undertaken to achieve this goal. Monitors used in conjunction with a procedure-oriented language will help. The team programmer concept, structured programming, the machine tool

approach to software development and automatic programming are all attempts which have been undertaken to increase programming productivity.

- c. Programming is estimated to represent only fifteen percent of the system life cycle time. Approximately fifty percent of a programmer's time is spent trying to find logical (and illogical) errors. Very little attention is now being focused on the validation problem, and yet, it is precisely here where our major resources are expended. This subject area demands our professional attention.

- d. Improved control systems for management use are required. A pre-requisite to management control is adequate planning. Planning, in turn,

requires refined estimating techniques. The computer industry has been embarrassingly deficient in its failure to develop a system to help management estimate system costs. The DOD community has made minimal attempts in this area with little success to show for our money. This area, too, demands much more of our managerial attention.

The challenges I have outlined are substantial, but the potential return is great. We have no alternative but to approach them -- if necessary -- one at a time.

This symposium is certainly a step in that direction, and I urge all of you to keep these objectives in mind as you participate in these discussions.

Thank you.

Philip J. Kiviat and Michael F. Morris

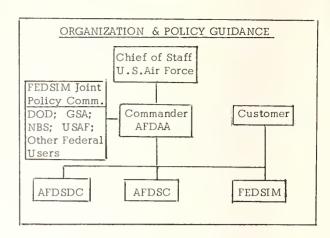

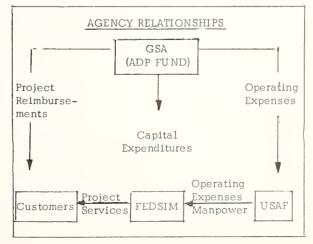

#### FEDSIM

## 1. WHEN TO START A PROGRAM

## A. EXPENDITURE LEVEL DECISION

When the cost of a computer installation reaches some threshold value, a CPE program may be examined as an investment problem. The installation costs include all computer and peripheral equipment; supplies such as cards, tapes and paper; all computer operations personnel; and any systems programmers that are used solely to keep the computer system operating. The value of the system's products must be established. Where no price is already associated with existing products, a break-even price per customer-ordered piece of output must be calculated and assumed as the start-up value. Once a system's cost exceeds its value, or value could be higher if the system could produce more salable products, CPE is needed. When value exceeds cost, but cost is high, CPE aimed at cost reduction is in order. As long as no value is associated with the system's products, there will be no real cost-reduction motivation to attempt to improve a system's performance (except, perhaps, as an academic exercise).

## B. PROBLEM DRIVEN DECISION

More typical of the reason most CPE efforts are begun: another set of applications are to be added to an alreadybusy computer system; projected workload growth was an underestimate; the director of operations says he needs another or a larger computer; etc. Someone must look deeply and carefully into the way that existing resources are being applied to meet existing demands. Then the demands and resources must be aligned so that room for growth is available. A simple example may be seen that really made a substantial difference in work performed at no real change in products produced: A system of 14 batch programs that had been operational on various equipment for nearly 16 years was modelled using a simulation package. This system ran an average of 4 hours and 30 minutes and interfaced with several other systems so that neither inputs nor outputs could be changed. Several proposed changes were tested on the simulator. Two very simple changes were found that made substantial differences in the system's performance: first, the programs were allowed to run simultaneously (multiprogram) wherever possible; and, second, records stored on disk were blocked to the average track size. The average system run time went down to 2 hours 5 minutes giving better than a 50% reduction each time the system is run. Total CPE project time was about six manweeks; five in the simulation phase and one to alter and test the programs. No magic or profound intellect was involved in this effort, just a thorough examination of the demands and resources.

## C. PRELIMINARY ANALYSES: SETTING GOALS, DEFINING APPLICATIONS

One of the worst ways to start a CPE effort is to purchase a hardware monitor and assign a person to use it to "do good things". Many starts have been made just like this and few, if any, have succeeded. The monitors are stored away, collecting only dust. It is much more reasonable if specific systems are identified for analysis with modest goals set such as -- decrease the time that is used by one old program by 5%; or, document the flow of jobs form the input desk to the output window and reduce the total turnaround time for one large job by 5%. No sophisticated tools are needed and any standard time study text will provide quidelines for the test. What these types of projects allow a manager to accomplish are, first, operations personnel become aware of a systematic improvement effort; and, second, recommendations will be made regarding information that is needed, but very difficult to obtain. Setting only one or two simple improvement goals causes unknowns to become visible. These unknowns may then be categorized into application areas for solution by specific CPE tools or techniques. The usual result of these initial efforts is establishment of a systematic analysis of the accounting package information and some physical rearrangement of computer support room layout. Once the analysis effort is underway, specific needs for additional CPE capability will become apparent. This approach is really quite conservative, and it may take six months or more before the effort begins to produce useful results. But, once underway, very valuable results will be produced.

## 2. SELECTING TEAM MEMBERS

The work "team" is used continuously to stress the point that a lone individual seldom succeeds for very long in a CPE effort. This is not to imply that more than one full-time person is always necessary, but rather that at least three different types of individuals need to be involved and the background that leads to CPE successes is seldom found in any one person.

## A. NECESSARY BACKGROUND

Implementing improvements is often more difficult than identifying improvements. Nearly all significant improvements require either programming skill or a background in systems engineering. Since systems programmers usually evolve from applications programmers, system men are ideal CPE specialists. A systems programmer with a field engineering history is even better. Education in a scientific discipline usually helps a person to examine situations systematically. A scientific education nearly always exposes an individual to fundamentals of mathematics and statistics. These traits--systematic thinking and knowledge of math and statistics -- are also necessary for a CPE team. An additional feature that adds immeasurably to a CPE team's effectiveness is an academically diversified background. Reasoning here is like in any other developing field -- the broader the investigator's background, the more likely that parallels will be seen in other fields where similar problems have already been solved.

## B. TYPES OF PEOPLE

Considerable amounts of nearly original or, at least, innovative thought is a major part of any disciplined investigation. (And the CPE team will indeed appear to be investigators if they are properly placed in the organizational structure.) Picking a person and making him think as a routine part of a task is a nearly impossible approach. It is far better to pick a reaearch type who takes every assignment as a challenge to his thought process. (If no researchers are available, pick a lazy person with the experience and education mentioned earlier.)

Next, and at times most important, is a person who can explain and convince. Perhaps an "evangelist" would come closer to describing this person than "salesman" but "evangelist" would be a misleading outline heading. (That is, no divine guidance is necessary for CPE success -- it does help. though.) This person is particularly important at the beginning and end of each CPE project. The idea of performing each project usually needs to be "sold" all the way down to the lowest involved working level. In fact, to be of lasting worth, it is more important that these working level people be convinced that CPE is worthwhile than that higher management be so convinced. Further, a sales type is essential when a project is completed (to make certain that those responsible for authorizing implementation of team recommendations are thoroughly convinced to do so). Unless changes are made, the CPE effort will be wasted.

As a CPE team must produce useful work in a timely manner, a worker is a must. This is the one individual who should be full time in the CPE field. He need not be particularly well educated or intelligent but he must not be lazy. He will probably be both the easiest one to find and the least expensive to pay. This is the team member who should have the strong system programming background as he will be the one that will sift through reams of output and determine feasible changes in programs.

It should by now be clear that good CPE teams aren't easy to find. This is true. In two cases of large CPE activities, about 100 detailed resumes of people who think they are qualified are examined to find each CPE specialist who turns out to be good. Most often, it's faster to offer the duty to someone in your shop that has the background and is of the type described earlier (or maybe to steal someone who is already a success - but this expensive).

## C. IMPORTANCE OF ATTITUDE

It is often true that very good systems programmers are extremely reluctant to change anything that they didn't think of first (or, at least to change it the way someone else has). This is a very poor attitude to bring into a CPE team. The best team members are openminded and eager to examne suggested changes from whatever source. Be careful that an individual who is too conservative in his work doesn't defeat the purpose of your CPE team. It is an imaginative and innovative field.

## D. IN-HOUSE OR CONSULTANTS

If time is available to decide to

go into CPE based on return on investment (as opposed to an immediate operational problem) it is certainly more beneficial to develop the CPE capability in-house. If the CPE need is immediate and if you have no capability in-house and can't hire a proven performer as a regular employee, then the only alternative is to use a consultant. There are certainly cases where a return-on-investment decision requires that the CPE investment be less than the cost of an established in-house effort. Such cases could be handled by consultants (although these aren't the jobs consultants try very hard to get...). As a general rule, solve immediate onetime problems with consultants. Solve immediate, but general problems with a consulting contract that requires the consultant to train your in-house CPE team. Solve continuing, non-urgent problems totally in-house. The suggestion here is no different for a CPE team than it would be for any other effort -- the best way is in-house.

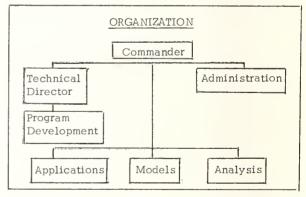

## 3. ORGANIZATIONAL PLACEMENT OF THE CPE $\overline{\text{TEAM}}$

Let's assume here that computer system expenditures are large enough to justify a continuing 1 1/2 - 2 manyear CPE investment per year on an in-house basis. (In the consultant case, the following could be put in terms of "Who should the consultant report to?").

## A. LINE VERSUS STAFF

A CPE team performs a staff function: it investigates existing methods, finds and recommends alternative methods, and outlines ways of implementing methods. Although the team must be able to implement any recommendation, it is usually a misallocation of scarce talent for the team to do this. Usually, and particularly in very large data processing environments, the CPE team will periodically be challenged (generally by a middle-manager in applications programming surroundings) to do the implementation job themselves. About every 8 to 12 months, this should be done. In the process of implementing its own recommendations, the team not only gains operational credibility, it also has the opportunity to sharpen and update the team's own programming (or systems design) skills. This keeps the CPE team from becoming a group of former experts. And this is important.

## B. REPORTING AUTHORITY

Organizations are so very different that the only way of describing placement, in general, is in relative terms. The team should, at the very lowest, report to the same person that the data processing or computer center manager reports to. Ideally, the CPE team should

report to the corporate-level controller. This placement insures that recommendations that are accepted will be implemented. Also, it will encourage the team to view their activity in a cost-benefit light. The more cost conscious the CPE team, the more likely that sound recommendations will be made. Unless the data processing center is extremely large, the CPE team should not report to the manager of data processing. (Extremely large: more than three separate and different computer systems and monthly least cost--or equivalent--of more than \$100,000.) If there is a good argument for using consultants continuously rather than in-house personnel, it is in this reporting authority region: A CPE team is really a working level activity. It is not customary to have this type activity reporting at such a high level. However, it is customary for consultants and outside auditors to circulate at the working level and report at very high management levels. Except in cases of very small companies (the president acting as data processing manager), company size has little to do with the CPE team's organizational placement. It is more a matter of scaling the CPE effort to match the computer effort, which is generally dependent on company size.

## C. CHARTER

This is the CPE team's license to operate. When duties to identify improvements in computer system operations are assigned to a group outside the direct control of the computer center manager (as recommended earlier), it is mandatory that clear notice of the team's operational arena be given. This notice should be formal (written) and signed by the highest possible corporate officer. Such a notice will be a charter or license to become involved in even the most routine aspects of providing computer support. The charter need not be long or particularly specific. General direction is usually better because it's never known ahead of time exactly which areas will produce the most plentiful savings. The ideas regarding system bottlenecks and workload characteristics that grow in the computer center without benefit of CPE tools, are almost always wrong. (Explain: scientific vs. business mix, printer-bound, etc.) A charter should include, as a minimum, the following statements:

"No new programs or systems of programs and no substantial changes to existing programs are to be implemented without first having the design or change reviewed by the CPE team. If in the CPE team's opinion it is necessary, the design or change must be simulated to predict its impact on the existing workload and to test any reasonable design alternatives before committing resources to programming and implementing the system or change.

"Before ordering new equipment to replace, to add to, or to enhance existing equipment's speed or capacity, the CPE team must be called upon to measure the levels of activity and contentions of the system or portions of the system that would be affected by the new equipment."

This type of charter will allow the team to examine both existing systems and proposed changes before new workloads or equipment acquisitions are committed. Determining the impact of such changes requires a thorough knowledge of existing workloads and systems. The benefit from this initial learning phase for the CPE team will be significant: it is almost always the first time that a review of all facets of the computer center's activity will have been attempted by knowledgeable and impartial persons. This phase is, in itself, sound justification for establishing a CPE team.

## D. CONTROLS

Since a good CPE team that is properly placed in the organization will represent a high level of technical competence and have the endorsement of upper management, there will be a tendency to react quickly to the team's suggestions. It is, therefore, important that rather strict controls be established to insure that the team follows a total project plan (more about this later) to its conclusion before discussing possible recommendations with those who will be implementing the changes. Otherwise, there may be changes well underway before all aspects of the changes are examined. And these may turn out to be unacceptable changes when everything is considered. It is quite easy to avoid this situation by adding a statement to the "charter" that establishes a need for written directive by some specified manager (above the CPE team) before any recommendation is to be implemented. Whenever possible, management should insist that the CPE team provide at least two recommended approaches to the solution of any problem. And the approach should be selected by a manager above the CPE team or within the area that will be most affected by the recommended change.

## 4. PROJECT ADMINISTRATION

## A. JOB DESCRIPTIONS

The formal writeups that cover CPE team members must mention the need to (1) work with documentation describing the logical and physical flow of signals through the system and its components; (2) perform measurement analyses and coding changes of applications and control programs; (3) install or connect such CPE

devices or tools as are available; (4) develop and use simulation and modeling techniques; and (5) document activities and recommendations for use by management. These may be elaborated as required to fit each personnel department's peculiar needs. But these five basic areas are necessary to insure that the CPE team has the minimal capability to perform useful projects.

## B. RESPONSIBILITIES

A CPE team just as any other group of employees, must be expected to produce results that are worth more than they cost. A detailed listing of responsibilities and procedures will be given in a moment, in classical management terms. At this point, it is enough to say that the team is responsible for "paying its own way." In the early start-up phase, it isn't reasonable to demand this of the team. But, by the end of its first year of existence, a CPE team that hasn't documented savings equal to or greater than its costs should be dissolved. By itself, this is a heavy responsibility to meet.

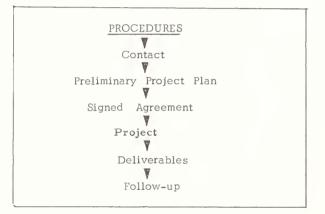

## C. PROCEDURES

The day-to-day operating procedures of the CPE team are essentially the same as for an audit group or, in times past, for a time-study effort: define a problem, examine existing methods, postulate changes, test change, recommend best changes, and oversee implementation of accepted recommendations. Written procedures are important especially for groups that visit detached sites.

## D. RECOMMENDING CHANGES

As pointed out earlier, changes should be recommended to management, not at the working level. The recommendations should only reach the working level in clear-cut, directive form.

## E. FORMAL REPORTS

These will be the only real (tangible) product of a properly run CPE team. The changes (except in the rare cases mentioned already) will be made by other programmers and engineers. Only by carefully and completely documenting each project can the CPE team progress in an orderly manner. A format for project reports that has proven useful in several environments is that of the classical "staff study": Purpose, Scope, Procedure, Findings, Conclusions, and Recommendations -- preceded by a short summary of major findings and recommendations. Hopefully, the entire report, but at least the summary and recommendations, should be completely "jargon" free. (The best report is worthless if only the authors can understand it.)

#### F. PROJECT MANAGEMENT

It has been implied several times that the CPE team is most effective if it operates on a project basis. CPE projects tend to be ad hoc in nature: each one has a single purpose. The following remarks are therefore framed in this project orientation. In classical management terms the CPE project manager's job is to:

--PLAN: Determine requirements of the project in terms of people, facilities, equipment, etc.; estimate the project's duration and relationships between workload of the CPE team and the project's deliverables.

--ORGANIZE: Request and insure availability of the necessary facilities, equipment, personnel, material, and (most important) authority.

--DIRECT: Set time and cost milestones and bounds for what must be done; make all operating, project-specific decisions.

--CONTROL: Measure performance against plan and take any necessary actions to correct malperformance.

--COORDINATE: Insure that all involved activities are aware of, and receptive to the project's efforts, goals, and recommendations.

To make certain that the full impact of this project administration section has been made clear, a few minutes will be spent on an exhaustive listing of the responsibilities of a CPE project manager. First, it is pointed out that if the CPE team is large, or if team members have specific skills that not all team members have, each project or study may have a different project manager. Each project manager is responsible for the technical content and conduct of the study. His ultimate responsibility is twofold: to the managers that receive the team's recommendations and to the individual or group who will implement the team's recommendations. For lack of a better term, these two groups are referred to as the "customer". The individual CPE project manager is responsible for:

- 1. Insuring that he can detect malperformance.

- 2. Establishing measures to prevent malperformance.

- 3. Assuring that he can correct malperformance.

- 4. Insuring that all ideas will be explored and exploited.

- 5. Exercising positive cost control.

- 6. Insuring that schedules will be met.

- 7. Establishing quality control procedures.

- 8. Thoroughly understanding the kinds of management abilities that will be required in a project.

- 9. Determining the quantity of management required in a project.

- 10. Determining what must be provided by all parties involved, e.g., sutomer, other suppliers.

- ll. Knowing what is needed to "solve" the problem.

- 12. Understanding the customer's problem and translating it into a solvable CPE problem.

- 13. Insuring that a clear, consistent, and appropriate plan for each study is produced.

- 14. Knowing how the results of the study will fill the customer's needs.

- 15. Insuring that the planned approach to the project is logical and realizable.

- \$16.\$ Understanding the details of the approach.

- 17. Insuring that all essential tasks are included.

- 18. Insuring that no unnecessary tasks are included.

- 19. Knowing the output from each task.

- $20\,.\,$  Judging whether or not each task is the best way to achieve the output.

- 21. Knowing what resources are required for each task.

- 22. Periodically reviewing the adequacy of the skills, quantity of personnel, facilities, equipment, and information.

- 23. Insuring that commitments of all resources made to the project are honored.

This is a rather long list for each CPE project but the team's tasks are complex and detailed enumeration of the individual project manager's responsibilities is important. What, then, is left for the leader of the CPE team to do if he is not always the project leader? -- Even a longer list of non-technical, management tasks.

The CPE team leader acts to:

- 1. Manage objectives of each CPE study.

- -Does the customer know what he wants?

- -Does the customer have the authority to perform its tasks?

- -Are all the results the customer requests needed?

- -Is the customer adequately motivated to support CPE efforts over the long haul?

- 2. Schedule the project tasks.

- -Use a documented, quantitative (graphic) method to schedule people, equipment, facilities, tasks.

- -Act to acquire resources when needed.

- -Establish procedures to monitor and control progress.

- 3. Select and organize personnel.

- -Determine when outside support is required.

- -When necessary, establish a project management structure.

- -Motivate personnel to the goals of the project.

- -Distribute workload to make the best use of present talents and promote cross training by on-the-job experience.

- 4. Manage the scope of each study.

- -Determine whether a study should be specific to a project or made more general.

- -Determine essential components and boundaries of the study.

- -Insure all boundary effect assumptions are considered and stated explicitly in project reports.

- 5. Control the level of detail for each study.

- -Derive an evolutionary development plan that permits continual assessment and redirection.

- -Strive for a minimal, consistent, level of detail, adding detail only on evidence that it is required.

- 6. Control costs.

- -Establish control procedures.

- -Guard against inefficient use of people and equipment.

- -Obtain CPE resources best suited to a project at a cost that is consistent with project size and importance.

- 7. Manage validation phase.

- -Expose all assumptions.

- -Determine the "level of noise" inherent in different methods.

- -Establish procedures for debugging and testing.

- -Specify nominal outputs in advance of experimentation.

- -Insure sensitivity analyses are performed.

- -Specify levels of confidence required to demonstrate success of a method.

- -Insist a validation plan be developed in advance of its need.

- 8. Manage documentation effort.

- -Insure that all assumptions and limitations are specified.

- -State the purpose and use of each recommendation.

- -Describe each recommendation clearly in narrative form.

- -Establish a project notebook that is a chronological log of all project decisions, actions, trip reports, etc.

- -Insure that a good channel of communication exists between CPE team members and their customers.

- 9. Manage experimentation effort.

- -Develop an experiment plan that is consistent with project objectives before starting a new type of project.

- -Establish validity of statistical analysis procedures when they are applied.

- -Insure analyses are consistent and correct.

- -Insure summaries and presentations are clear, illuminating and concise.

- -Insure experiments produce required results.

## 5. ACQUIRING TOOLS AND TECHNIQUES

(Most of the rest of the outlined topics will be covered in detail by other presentations. They are mentioned here, briefly, simply to introduce them as important topics that require concern if a viable CPE effort is to be established at any installation).

## A. FREE TOOLS - ACCOUNTING PACKAGES

Before any special CPE tools are purchased or techniques are learned, the output of the system accounting package should be studied in detail and thoroughly understood. A tremendous amount of information that can lead to improved computer performance is contained in accounting data. In almost every case, it is a "free" good. That is, it is collected as a routine task. If nothing is now done to your facility's capacity: eliminate the accounting package. But if you are seriously considering the establishment of a CPE activity, you'll have to reinstall this package at least periodically. Nevertheless, if you don't use its output now, stop generating it.

#### B. COMMERCIALLY AVAILABLE TOOLS

A list of all CPE suppliers is given in the following table. There are three general product categories:

- -Accounting package reduction programs, referred to in the table as "Other".

- -Monitors, broken into hardware and software monitors.

- -Simulation, which is in the form of general purpose CPE packages, specialized simulation languages, and simulation studies.

#### C. SURVEYING THE FIELD

Several individuals have compared and contrasted the various CPE tools that are now available. Such surveys should be examined before commitments are made to any one CPE supplier. User's groups are the best sources of this survey information. Figure 8-10 lists several

CPE product suppliers as an indication of the broad availability of such products.

#### D. LEARNING TECHNIQUES

All CPE techniques require some training before they can be used. In order of least to most training, these are:

- -Accounting system analysis

- -Software monitors

- -Hardware monitors

- -Simulation languages

- -Simulation packages

While CPE techniques can be learned by self-study, classroom training is advised. On-the-job training is imperative, as class-room courses can teach only technique, and not guidelines or standards for its application in the field.

#### E. PROCURING TOOLS

As mentioned earlier, it is not wise to begin a CPE effort by purchasing CPE equipment. First, use the available accounting data, then acquire a software monitor or accounting data reduction package (lease one, don't buy, as it will soon be unused in most shops), then develop a simulation capability, and finally -- when the CPE team justifies it for a specific project -- acquire a hardware monitor. This procurement of tools should span at least one year and probably two or three.

## 6. A FLOW CHART FOR CPE DECISIONS

The chart shown in Figure 8-17 describes many situations where CPE may be useful. It's certainly not exhaustive, but it covers enough situations to give a new CPE team an ambitious start. Its use can help an organization to decide where the application of CPE may produce worthwhile results.

## CONTINUING THE EVALUATION ACTIVITY

Once established, the CPE team loops through a series of continuing activities:

- A. Examine and select new CPE tools

- 1. To keep up with developments.

- To interchange information with CPE teams

- - 1. The characteristics of each installation

- a. Capital investment

- b. Workload stability

- c. Personnel

- 2. The aging of systems

- - a. New systems

- b. New users

- c. New user mix, e.g., RJE, interactive, batch

- C. Maintain a close watch over the distribution of computer activity by device and by program to:

- 1. Relate equipment costs to level of use

- Determine trade-offs possible between cost and performance

- "Tune" the total system as a routine task

- a. Data set allocation

- b. Selection of programs for multi-programming

- c. Operating system and applications program optimization

- D. Develop a CPE data base

- 1. CPE information collected by one tool will usually be used in conjunction with that collected by another tool.

- 2. Historical data can be used to predict trends in workload, usage, etc.

- As new analysis tools and techniques are developed, data from well-understood situations is needed to test their discriminant and predictive power.

- 4. A common data format and structure is needed to compare similar installations for normative and management purposes.

- 5. Customized interfaces can be built between the data base and the CPE tools used to standardize and simplify tool Center (FEDSIM). usage and add additional features, e.g., editing.

- "Trigger" reports can be incorporated into data base processing or interface programs to indicate that something is happening in the system that should be studied in detail.

- 3. Planned workload changes E. Integrate ment activities E. Integrate operations and measure-

- 1. Educate operations personnel to be aware of visual cues to system malperformance

- 2. Use existing and new operations reports

- a. Console logs

- b. System Incidence Reports

- c. "Suggestion Box"

- 3. Educate operators in use of tools to improve selection of jobs for multiprogramming, mounting of tapes and disk packs upon request, etc.

## Operator performance is an overriding factor in the operation of an efficient thirdgeneration computer installation.

- F. Establish good relations with the computer system vendor

- 1. May require assistance for probe point development

- 2. May require permission to attach a hardware monitor

- 3. First instinct of maintenance personnel is to resist measurement activities

- 4. Acquire a knowledge of his activities and the acquaintance of his research staff

- G. Kiviat Graphs for Diagnosing Computer Performance (Refer to reprint of "Computerworld" article)

## SPECIAL CONSIDERATIONS AND FINANCIAL ASPECTS

- A. A minimum investment in CPE tools and technicians will be one manyear per year and an equivalent in tool and training expenditures, computer costs, travel expenses, etc. Assume this is \$40,000 based on proration of the following costs experienced at the Federal Computer Performance Evaluation and Simulation

- Typical FEDSIM staff salary: \$19,700

- 2. Software monitor: \$1-15,000

- 3. Hardware monitor: \$4-100,000

- 4. Accounting system analysis \$3-15,000 program:

- 5. Simulation packages: \$12-40,000

- B. CPE savings must be at least 5%, probably no more than 20\$ on an annualized basis, although many individual projects will show larger returns. For example:

- \$40,000/.05 = \$800,000 per year to justify on low expected CPE value;

- \$40,000/.20 = \$200,000 per year to justify on high expected CPE value.

- C. CPE savings are difficult to quantify in many instances, e.g., system design analysis via simulators, configurations studies for system enhancement, measurement of workload to prepare benchmarks for new RFP, etc.

CPE savings are easy to quantify in other instances, e.g., equipment returned after a reconfiguration prompted by a measurement analysis, computer time saved by system and program tuning, etc.

But what is extra computer capacity, improved turnaround or better response worth to the company?

D. Manufacturers will not assist most smaller installations in their CPE efforts, as their goal is to increase these to larger systems. CPE is counter to this goal.

E. There are many small systems using general purpose computers for highly specialized applications. CPE effort in these installations should be spent in stripping all unused or unnecessary parts out of the control program to match it to the special application. In the case of serial, batch systems (or serial, batch equipment) there is little that CPE can do for performance. In these cases, the best available programming techniques are called for.

## F. CPE should include:

- 1. Software package evaluation

- Software validation and verification

- 3. Equipment reliability studies

- 4. Studies of programming techniques

- 5. Management and organizational effects

But it rarely does. CPE should be viewed from a total systems perspective.

#### Daniel M. Venese

## The MITRE Corporation

#### T. INTRODUCTION

This paper presents a methodology for performance evaluation. A general framework is developed to orient and direct a performance evaluation task. Within this framework, operating systems can be classified and compared, hypotheses formulated, experiments performed, and cost/benefit criteria applied. This methodology has the following underlying assumptions:

- (a) Most systems can be modified or tuned to achieve improved performance.

- (b) Although some optimizations will not degrade other areas of system performance (removing a system-wide bottleneck), most performance gains will be the result of compromise and cause degradation in another area of system performance.

- (c) Relatively small changes can often lead to dramatic changes in system performance.

- (d) Modifications indicated by a performance evaluation study should be cost effective.

- (e) In many cases when a performance bottleneck is removed, another will immediately become the limiting factor on performance.

The aim of this methodology is to account for the significant factors that affect a performance evaluation effort. Inadequate performance evaluations result from limited outlooks. Purely technical evaluations concentrate on hardware and software monitors, but ignore the human factors. Other efforts have obtained huge quantities of data without a framework for analysis. In general, two of the most common inadequacies are to take a narrow approach to performance evaluation and to gather data without having a means to analyze it.

## II. OUTLINE OF METHODOLOGY

The following outline describes the steps in the performance evaluation methodology:

- (a) Understand the system. Classify the subject operating system according to the framework provided in paragraph III.

- (b) Survey the environment. Examine and analyze the environment surrounding the computer installation including management attitudes and goals, mode of operation, workload characteristics, and personnel experience.

- (c) Evaluate system performance:

- (1) examine problem types,

- (2) formulate performance evaluation hypothesis,

- (3) conduct benefits analysis, and

- (4) test performance evaluation hypothe-

#### III. OPERATING SYSTEMS FRAMEWORK

In order to conduct an effective performance evaluation, it is necessary to understand the operating system. Although the precise implementation of each operating system differs in many respects, they have many facets in common. The identification and classification of these common functions into a framework for understanding operating systems is an important step in computer performance evaluation (CPE).

This framework for operating systems is not intended to be all inclusive since operating systems can be examined and classified from other meaningful points of view. Examining and classifying from the user point of view, is an example of another framework. The framework presented here isolates those portions that are important in CPE and allows various systems to be compared by means of this common classification.

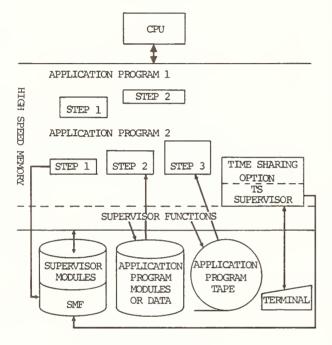

Large-scale third-generation computers typically have more resources than any single program is likely to need. The rationale for an operating system is to manage the utilization of these resources allowing many programs to be executing at one time. The resource manager concept of operating system is the product of J. Donovan and S. Madnick of MIT.

In a computing system with finite resources and a demand for resources that periodically exceeds capacity, the resource manager (operating system) makes many policy decisions. Policy decisions are strategies for selecting a course of action from a number of alternatives. There is general agreement that as many relevant factors as possible should be included in policy decisions. For example, the core allocator algorithm might consider such factors as the amount requested, the amount available, the job priority, the estimated run time, other outstanding requests, and the availability of other requested peripherals. Disagreement arises as to how factors should be weighted and the strategies that are most appropriate for the installation workload.

The component of the operating system that decides which jobs will be allowed to compete for the CPU is the job scheduler. The scheduling policy might be first-in, first-out (FIFO) or estimated run time with the smallest jobs scheduled first. The FIFO strategy is one of the simplest to design and implement, but it has many disadvantages. The order of arrival is not necessarily the order in which jobs should be selected for execution nor can it be assured that a FIFO scheduling policy will provide a balanced job mix and adequate turnaround for priority jobs. Although general prupose algorithms can provide

an acceptable level of service for a wide spectrum of situations, tuning to the needs of the particular DPI can realize significant gains in efficiency and ease of use.

Once a job has been allocated and is eligible for execution, the process scheduler (system dispatcher) decides when jobs gain control of the CPU and how long they maintain control. The process scheduler queue may be maintained in order by priority, by the ratio of I/O to CPU time or in a number of different ways. The job scheduler decides which jobs will be eligible to compete for CPU time while the process scheduler decides which jobs will receive CPU time. A number of other decision points and important queues are found in operating systems. These include I/O supervisors, output queues, interrupt processing supervisors, and data management supervisors.

Another important facet of operating systems is the non-functional software which carries out the policy decisions and comprises the bulk of the operating system software. The gains to be effected in the areas of policy making are primarily the result of tuning to the particular Data Processing Installation (DPI) while the gains from the non-functional software are primarily the result of improvements in efficiency. For example, the routine that physically allocates core has a number of minor housekeeping decisions to make and any improvements to be realized in this area will be from an improved chaining procedure or a faster way of searching tables or a similar type of gain in efficiency.

Once this framework for computer systems has been adopted, systems are no longer viewed as a collection of disparate components, but as a collection of resources. The operating system is the manager of these resources and attempts to allocate them in an efficient manner through policy decisions and non-functional software to carry out these decisions. System bottlenecks are not mysterious problems, but are the result of excess demand for a limited resource. By stating performance problems in terms of the relevant resources instead of in terms of the effects of the problem, the areas in need of investigation are clearly delineated.

## IV. SURVEY THE ENVIRONMENT

Understanding and classifying the subject operating system is one facet of understanding the total system. Computers do not operate in a vacuum. Their performance is influenced by the attitudes and abilities of the operations personnel, programmers and managers. Although improving the performance of a system by streamlining the administrative procedures is not as dramatic as discovering a previously unknown inefficiency in the operating system, the net gain can be just as worthwhile.

## Computer Operations

Parts of the following survey are based on the Rand document, "Computer Performance Analysis: Framework and Initial Phases for a Performance Improvement Effort," by T. E. Bell.

- (a) Determine the prime operational goal of the computer center.

- (b) Determine which job or group of jobs constitutes a significant part of the installation's workload.

- (c) Describe the explicit actions taken by the computer operations to help schedule the computer, e.g., using job priorities to promote a good job mix.

- (d) Determine the most frequent causes for computer reruns, e.g., mounting the wrong tape for a production run.

- (e) Determine from interviewing computer operations personnel the extent to which the following are done:

- (1) scheduling of jobs,

- (2) premounting of tapes and disks,

- (3) interfacing with users,

- (4) card handling,

- (5) responding to console commands, and

- (6) documenting operational difficulties.

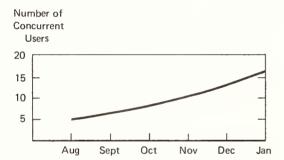

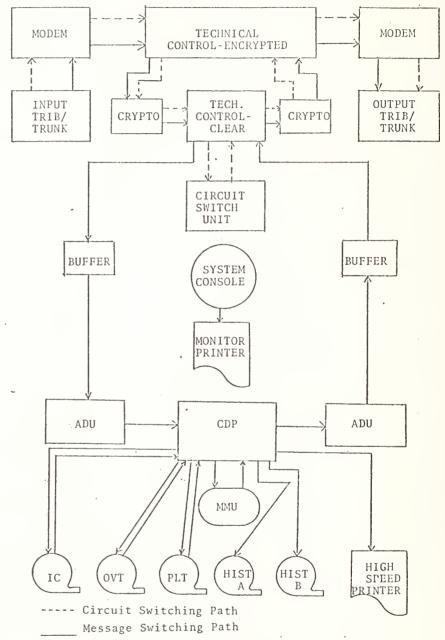

- (f) Determine the extent and impact of on-line applications on the computer system.