IC 20 .57

100-4

.2

# NBS SPECIAL PUBLICATION 400-4

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

# Semiconductor Measurement Technology

Combined Quarterly Report October 1, 1973 to March 31, 1974 The National Bureau of Standards<sup>1</sup> was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of a Center for Radiation Research, an Office of Measurement Services and the following divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Nuclear Sciences<sup>2</sup> — Applied Radiation<sup>2</sup> — Quantum Electronics<sup>3</sup> — Electromagnetics<sup>3</sup> — Time and Frequency<sup>3</sup> — Laboratory Astrophysics<sup>3</sup> — Cryogenics<sup>3</sup>.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry.

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services to promote the use of available technology and to facilitate technological innovation in industry and Government; cooperates with public and private organizations leading to the development of technological standards (including mandatory safety standards), codes and methods of test; and provides technical advice and services to Government agencies upon request. The Institute consists of a Center for Building Technology and the following divisions and offices:

Engineering and Product Standards — Weights and Measures — Invention and Innovation — Product Evaluation Technology — Electronic Technology — Technical Analysis — Measurement Engineering — Structures, Materials, and Life Safety <sup>4</sup> — Building Environment <sup>4</sup> — Technical Evaluation and Application <sup>4</sup> — Fire Technology.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical services designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the selection, acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the executive branch for the development of Federal standards for automatic data processing equipment, techniques, and computer languages. The Institute consists of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific information generated within NBS and other agencies of the Federal Government; promotes the development of the National Standard Reference Data System and a system of information analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate services to ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of the following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Library — Office of International Relations.

<sup>&</sup>lt;sup>1</sup>Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

<sup>&</sup>lt;sup>2</sup> Part of the Center for Radiation Research. <sup>3</sup> Located at Boulder, Colorado 80302.

<sup>&</sup>lt;sup>4</sup> Part of the Center for Building Technology.

Bureau of Standards

0-4

# <sup>1974</sup> Semiconductor Measurement Technology Combined Quarterly Report, October 1, 1973 to March 31, 1974

W. Murray Bullis, Editor

Electronic Technology Division Institute for Applied Technology V.S. National Bureau of Standards Washington, D.C. 20234

> Jointly Supported by: The National Bureau of Standards, The Defense Nuclear Agency, and The Defense Advanced Research Projects Agency

t. Special publication no. 400-4

U.S. DEPARTMENT OF COMMERCE, Frederick B. Dent, Secretary NATIONAL BUREAU OF STANDARDS, Richard W. Roberts, Director

+2

Issued November 1974

National Bureau of Standards Special Publication 400-4 Nat. Bur. Stand. (U.S.), Spec. Publ. 400-4,101 pages (Nov. 1974) CODEN: XNBSAV

> U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1974

For sale by the Superintendent of Documents, U.S. Government Printing Office, Washington, D.C. 20402 (Order by SD Catalog No. C13.10:400-4). Price \$1.70

# TABLE OF CONTENTS

# SEMICONDUCTOR MEASUREMENT TECHNOLOGY

| PAG                                                                | ۲Ľ, |

|--------------------------------------------------------------------|-----|

| Preface                                                            | ç   |

| 1. Introduction                                                    | L   |

| 2. Highlights                                                      | 3   |

| 3. Resistivity; Dopant Profiles                                    | 5   |

| 3.1. Spreading Resistance Methods                                  | 5   |

| 3.2. Junction Capacitance-Voltage Method                           | 3   |

| 3.3. Mathematical Models of Dopant Profiles                        | )   |

| 3.4. Diffused Layer Sheet Resistance                               | L   |

| 3.5. Reevaluation of Irvin's Curves                                | 3   |

| 3.6. Computer Program to Calculate Dopant Density from Resistivity | 3   |

| 3.7. Effective Masses and Band Gap of Silicon                      | 5   |

| 3.8. Hall Effect Measurements                                      | L   |

| 3.9. Probe Force Measurements                                      | ÷   |

| 3.10. Standard Reference Materials                                 | 5   |

| 3.11. Other Standards Activities                                   | ;   |

| 4. Crystal Defects and Contaminants                                | ,   |

| 4.1. Thermally Stimulated Current and Capacitance Measurements     | ,   |

| 5. Oxide Film Characterization                                     | Ļ   |

| 5.1. MOS Capacitance-Voltage Method                                | ł   |

| 5.2. MOS Bias-Temperature Stress Test                              | ,   |

| 5.3. Hot/Cold Stage Development                                    | )   |

| 5.4. Ion Microprobe Mass Analysis                                  | ,   |

| 5.5. X-Ray Photoelectron and Auger Electron Spectroscopy           |     |

| 6. Test Patterns                                                   | 3   |

| 6.1. Process Development                                           | 3   |

| 6.2. Test Structure: Collector Resistor                            | 3   |

| 6.3. Test Pattern: Charged-Coupled Device                          | ;   |

| 6.4. Test Structures: Sheet Resistors                              |     |

| 7. Photolithography                                                | ,   |

| 7.1. Photomask Metrology                                           |     |

| 7.2. Automated Photomask Inspection                                |     |

| 7.3. Photoresist Illumination                                      |     |

| 7.4. Photoresist Spinner Dynamics                                  |     |

| 8. Epitaxial Layer Thickness                                       |     |

| 8.1. MOS Capacitance Methods                                       |     |

|                                                                    | ~   |

# TABLE OF CONTENTS

| 9. Wa   | afer Inspection and Test                                          | 54 |

|---------|-------------------------------------------------------------------|----|

| 9.1.    | Flying-Spot Scanner Development                                   | 54 |

| 9.2.    | Scanning Electron Microscope Damage Study                         | 54 |

| 9.3.    | Scanning Electron Microscopy Voltage Contrast Mode                | 54 |

| 9.4.    | Scanning Electron Microscopy — Electron Beam Induced Current Mode | 56 |

| 10. In  | nterconnection Bonding                                            | 57 |

| 10.1.   | Ultrasonic Bonding to Thick Film Copper with Aluminum Ribbon Wire |    |

| 10.2.   | Ultrasonic Bonding of Small Diameter Platinum Wire                | 57 |

| 10.3.   | Automatic Puller for Beam Lead Bonds                              | 60 |

| 10.4.   | Non-Destructive Wire Bond Pull Test                               | 60 |

| 10.5.   | Bonds in Power Devices                                            | 63 |

| 10.6.   | Direct Observation of Ultrasonic Aluminum Wire Bonds              | 63 |

| 10.7.   | In-Process Bond Monitor                                           | 65 |

| 11. He  | ermeticity                                                        | 67 |

|         | Helium Mass Spectrometer Method for Leak Detection                |    |

| 11.2.   | ARPA/NBS Workshop II                                              | 67 |

|         | Mass Spectrometer Application                                     |    |

| 11.4.   | Gas Flow Mechanisms                                               | 68 |

|         | Dry, Quantitative Gross Leak Test                                 | 70 |

| 12. Th  | nermal Properties of Devices                                      | 71 |

| 12.1.   | Transient Thermal Response                                        | 71 |

| 12.2.   | Standardization Activities                                        | 74 |

|         | crowave Diodes                                                    | 75 |

|         | Radiation Response of Schottky-Barrier X-Band Mixer Diodes        |    |

|         |                                                                   |    |

| 14. Ke  | eferences                                                         | 78 |

| Appendi | x A. Semiconductor Technology Program Staff                       | 82 |

| Appendi | x B. Semiconductor Technology Program Publications                | 83 |

| Appendi | x C. Workshop and Symposium Schedule                              | 85 |

| Appendi | x D. Standards Committee Activities                               | 86 |

| Appendi | x E. Solid-State Technology & Fabrication Services                | 88 |

| Index   |                                                                   | 89 |

| 1.  | Scanning electron micrograph of tip of an unconditioned tungsten carbide                                                                    |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | spreading resistance probe with a nominal radius of 125 $\mu m$                                                                             | 7  |

| 2.  | Scanning electron micrograph of a lightly abraded tungsten carbide spreading resistance probe with a nominal radius of 125 $\mu m$          | 7  |

| 3.  | Imprints of two spreading resistance probes with about the same contact                                                                     |    |

|     | resistance                                                                                                                                  | 8  |

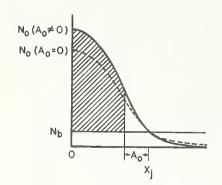

| 4.  | Dopant density profile of a diffused layer showing true $[N_0(A_0\neq 0)]$ and apparent $[N_0(A_0=0)]$ surface dopant density               | 12 |

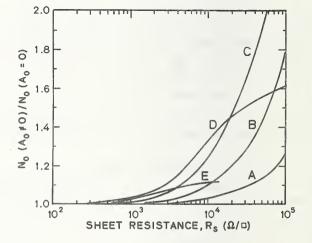

| 5.  | Ratio of true to apparent surface dopant density of a $p$ -type Gaussian                                                                    |    |

|     | diffused junction, 0.1 $\mu m$ deep, as a function of sheet resistance, for                                                                 |    |

|     | various values of background dopant density, $N_b$                                                                                          | 12 |

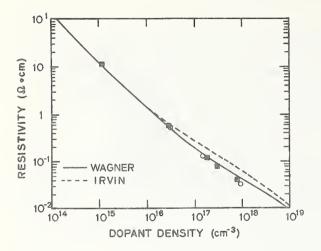

| б.  | Resistivity as a function of dopant impurity density for $p$ -type silicon                                                                  | 14 |

| 7.  | Plots to show region of convergence for solution to the carrier density                                                                     |    |

|     | equation                                                                                                                                    | 15 |

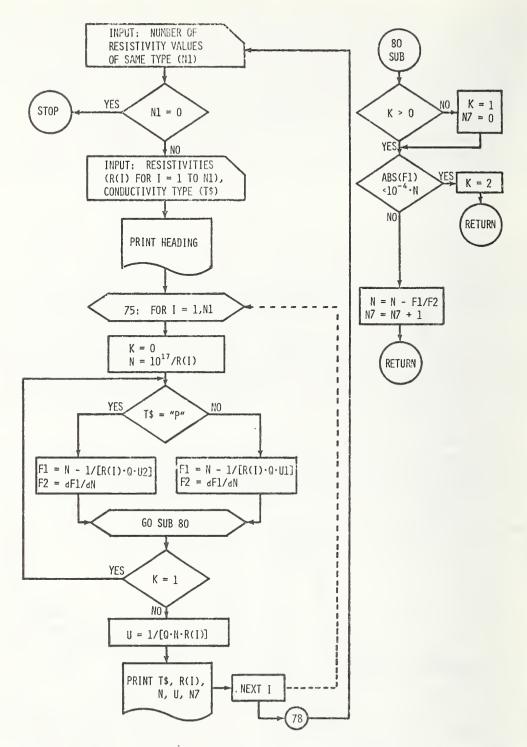

| 8.  | Flow chart for extended BASIC DOPDEN program                                                                                                | 16 |

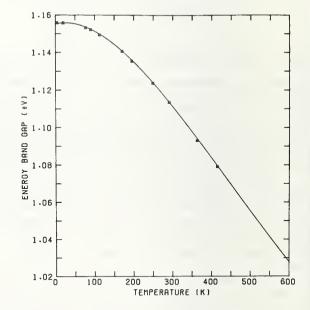

| 9.  | Energy band gap of silicon as a function of temperature                                                                                     | 20 |

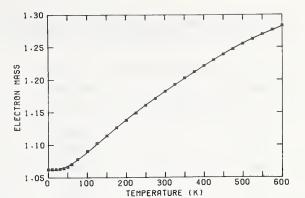

| 10. | Electron density-of-states effective mass in silicon with donor density                                                                     |    |

|     | less than 5 × $10^{17}$ cm <sup>-3</sup> as a function of temperature                                                                       | 21 |

| 11. | Hole density-of-states effective mass in silicon with acceptor density                                                                      |    |

|     | less than $10^{18}$ cm <sup>-3</sup> as a function of temperature                                                                           | 22 |

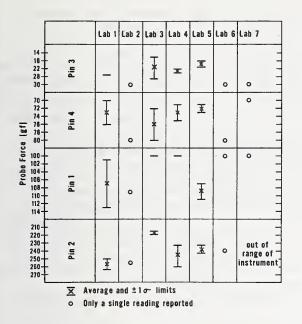

| 12. | Restoring force of the pins of a four-probe array for measuring resistivity                                                                 |    |

|     | as measured by seven laboratories                                                                                                           | 25 |

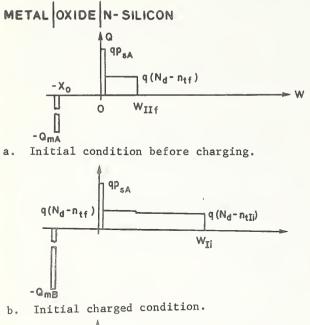

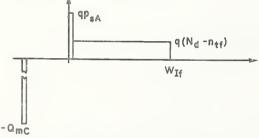

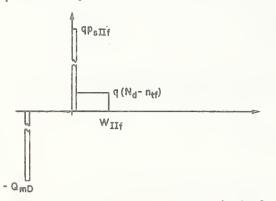

| 13. | Charge density distribution in an ideal, gold-doped <i>n</i> -MOS capacitor during                                                          |    |

|     | dynathermal response measurement                                                                                                            | 28 |

| 14. | Capacitance-voltage characteristic and dynathermal current and capacitance                                                                  |    |

|     | response of an ideal, gold-doped <i>n</i> -MOS capacitor                                                                                    | 28 |

| 15. |                                                                                                                                             |    |

|     | at various heating rates                                                                                                                    | 32 |

| 16. | Emission temperature of the phase II response of the gold acceptor in a silicon <i>n</i> -MOS capacitor at various normalized heating rates | 33 |

| 17. | MOS capacitor and its equivalent circuit representations                                                                                    | 35 |

| 18. | MOS capacitor with backside oxide film and its equivalent circuit                                                                           |    |

|     | representations                                                                                                                             | 35 |

| 19. | Worst case error plot for capacitance measurements on an MOS capacitor<br>with zero backside contact resistance, steam grown silicon dioxide of |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | three thicknesses, $X_0$ , and a measurement frequency of 1 MHz                                                                                 | 36 |

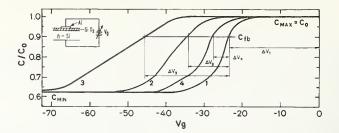

| 20. | Capacitance-voltage characteristics of an MOS capacitor with poor                                                                               |    |

|     | oxide quality after various bias-temperature stresses                                                                                           | 38 |

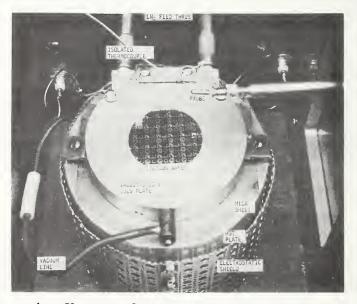

| 21. | Hot-cold stage for wafer characterization                                                                                                       | 40 |

| 22. | Photomicrograph of collector resistor, test structure 18 of test pattern                                                                        |    |

|     | NBS-2                                                                                                                                           | 45 |

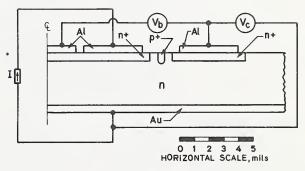

| 23. | Cross sectional diagram of collector resistor structure with a schematic of                                                                     |    |

|     | the measuring circuit                                                                                                                           | 45 |

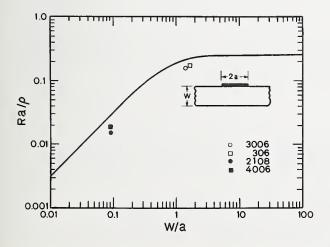

| 24. | Normalized resistance-resistivity ratio as a function of normalized sheet                                                                       |    |

|     | thickness                                                                                                                                       | 45 |

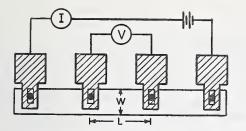

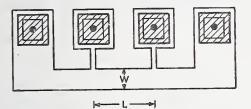

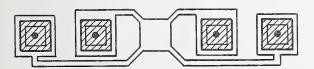

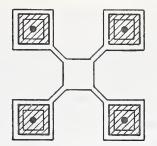

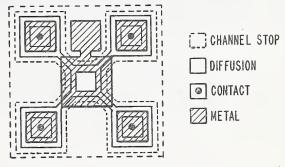

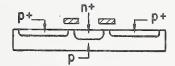

| 25. | Diffused layer sheet resistors with Kelvin contact schemes                                                                                      | 47 |

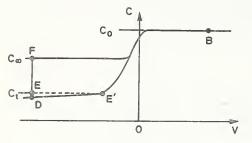

| 26. | High-frequency capacitance-voltage characteristic of an <i>n</i> -MOS capacitor                                                                 | 52 |

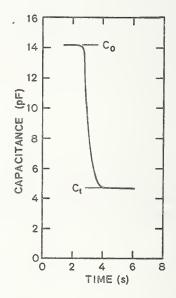

| 27. | Relaxation characteristic of an MOS capacitor formed on a thin                                                                                  |    |

|     | epitaxial layer illustrating the step-relaxation method for measuring                                                                           |    |

|     | epitaxial layer thickness                                                                                                                       | 52 |

| 28. | Deep depletion characteristic of an MOS capacitor formed on a thin                                                                              |    |

|     | epitaxial layer illustrating the ramp-voltage method for measuring                                                                              |    |

|     | epitaxial layer thickness                                                                                                                       | 52 |

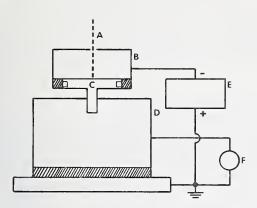

| 29. | Configuration of the beam current measuring equipment                                                                                           | 55 |

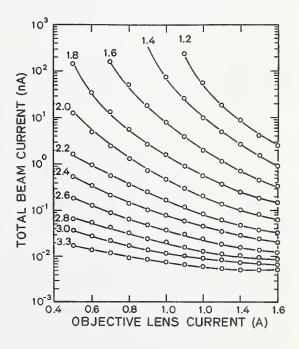

| 30. | Beam current as a function of objective lens current for an accelerating                                                                        |    |

|     | voltage of 20 kV and various values of condenser lens current                                                                                   | 55 |

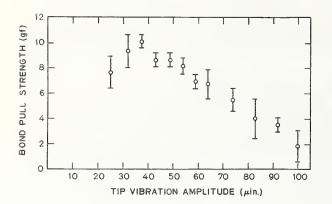

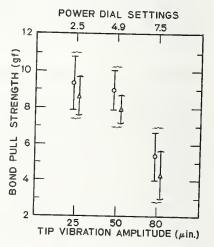

| 31. | Pull strength of aluminum ribbon wire bonded to thick film copper                                                                               | 58 |

| 32. | Pull strength of aluminum ribbon wire bonded to etched thick film copper                                                                        |    |

|     | before and after heating in air at 155°C for 168 h                                                                                              | 58 |

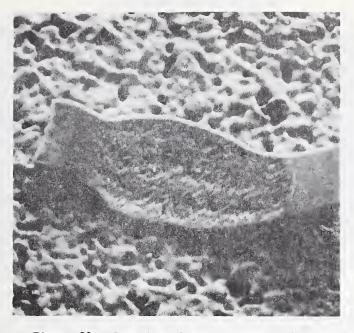

| 33. | Scanning electron micrograph of first bond of aluminum ribbon wire                                                                              |    |

|     | made to etched thick film copper with high power after heating in                                                                               |    |

|     | air at 155°C for 168 h                                                                                                                          | 59 |

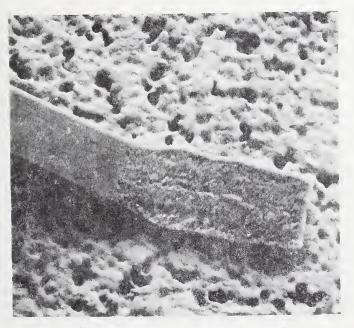

| 34. | Scanning electron micrograph of second bond of aluminum ribbon wire                                                                             |    |

|     | made to etched thick film copper with intermediate power after heating                                                                          | 50 |

|     | in air at 155°C for 168 h                                                                                                                       | 59 |

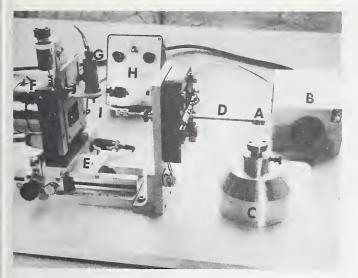

| 35. | Automatic puller for beam lead bonds                                                                                                            | 61 |

| 36. | Two-axis, variable-angle substrate holder                                                                                                       | 61 |

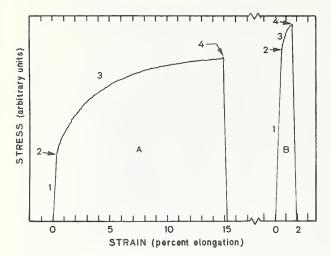

| 37. | Stress-strain curves for annealed and hard-drawn or stress-relieved aluminum wire |

|-----|-----------------------------------------------------------------------------------|

|     |                                                                                   |

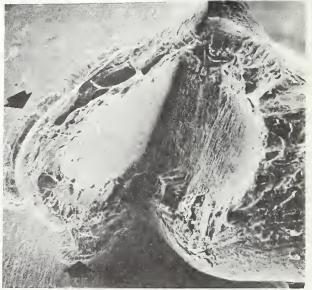

| 38. | Scanning electron micrograph showing the typical failure mode of well-made,       |

|     | 200-µm diameter, aluminum wire bonds subjected to a destructive double-bond       |

|     | pull test                                                                         |

| 39. | Scanning electron micrograph of the emitter post of a power transistor            |

|     | showing the imprint of a weak electrical discharge weld that lifted off           |

|     | at low pull force and a partially peeled back $300-\mu m$ diameter aluminum       |

|     | wire bond                                                                         |

| 40. | Scanning electron micrograph of a partially lifted, very strong electrical        |

|     | discharge weld to a gold-plated post showing the absence of welding in the        |

|     | center of the bond                                                                |

| 41. | Scanning electron micrograph of the lower emitter post bond of figure 39 at       |

|     | greater magnification to show absence of deformation or welding in the center     |

|     | region of the bond and purple plague regions around the outer perimeter of        |

|     | the weld                                                                          |

| 42. | Photomicrographs of patterns of ultrasonic aluminum wire bonds made with          |

|     | various power settings to a thin aluminum film on a 96-percent silica glass       |

|     | slide viewed through the glass slide                                              |

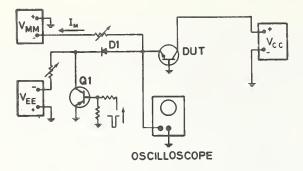

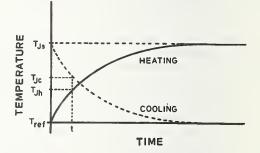

| 43. | Emitter-only switching circuit for measuring thermal response of transistors      |

|     | using the emitter-base voltage as the temperature sensitive parameter             |

| 44. | Illustrative heating and cooling curves of a semiconductor device                 |

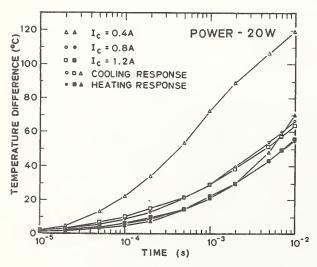

| 45. | Electrically measured heating and cooling curves for constant power at            |

|     | three different current-voltage operating conditions                              |

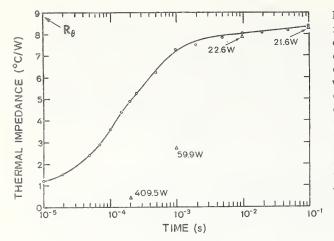

| 46. | Thermal impedance derived from the electrically measured cooling curve of         |

|     | a device which has a severe current constriction at the steady-state              |

|     | operating conditions for which the cooling curve was generated compared           |

|     | with thermal impedance determined for pulsed power in excess of the               |

|     | dissipation limited d-c power where the peak temperature for the pulse            |

|     | was the same as the steady-state temperature                                      |

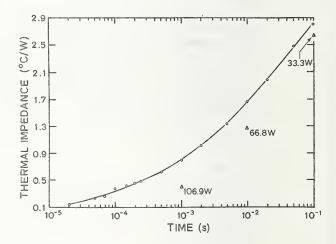

| 47. | Thermal impedance derived from the electrically measured cooling curve            |

|     | of a device which has a relatively uniform current distribution at the            |

|     | steady-state operating conditions for which the cooling curve was generated       |

|     | compared with thermal impedance determined for pulsed power in excess of the      |

|     | dissipation limited d-c power where the peak temperature for the pulse was        |

|     | the same as the steady-state temperature                                          |

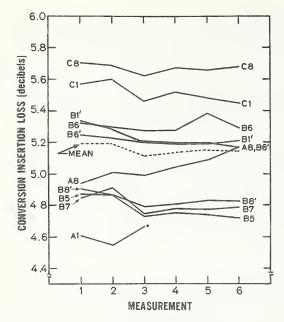

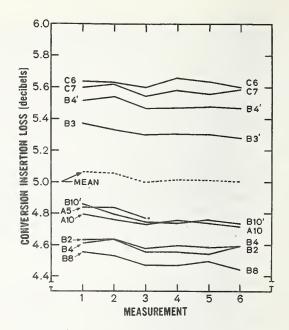

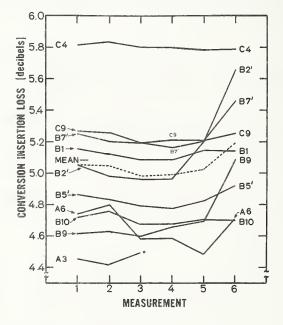

| 48. | Conversion | insertion | loss | for | first-lot | gamma-group  | diodes   | • | • • | • | • | • | • | • | • |  | 76 |

|-----|------------|-----------|------|-----|-----------|--------------|----------|---|-----|---|---|---|---|---|---|--|----|

| 49. | Conversion | insertion | loss | for | first-lot | control-grou | up diode | s |     | • | • | • | • | • | • |  | 76 |

| 50. | Conversion | insertion | loss | for | first-lot | neutron-grou | ip diode | 5 |     |   |   |   |   | • | • |  | 76 |

# LIST OF TABLES

|     |                                                                                                                                              |   | PAGE |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|---|------|

| 1.  | Summary of <i>p</i> -Type Dopant Density Profiles, Run No. 2.5                                                                               | • | 10   |

| 2.  | Listing of Extended BASIC DOPDEN Program                                                                                                     | • | 17   |

| 3.  | Variables for Extended BASIC DOPDEN Program                                                                                                  | • | 18   |

| 4.  | Typical Output of Extended BASIC DOPDEN Program                                                                                              |   | 19   |

| 5.  | Coefficients of the Polynomial Fits to the Energy Band Gap, Electron Mass,<br>and Hole Mass of Silicon                                       |   | 20   |

| 6.  | Data used for the Polynomial Fit of the Energy Band Gap of Silicon                                                                           | • | 20   |

| 7.  | Data used for the Polynomial Fit of the Electron Density-of-States<br>Effective Mass in Silicon                                              |   | 21   |

| 8.  | Data used for the Polynomial Fit of the Hole Density-of-States Effective<br>Mass in Silicon                                                  | • | 22   |

| 9.  | Band Gap, Electron Mass, Hole Mass, and Intrinsic Carrier Density of<br>Silicon at Selected Temperatures Calculated from the Polynomial Fits | • | 23   |

| 10. | Constants for Emission Rates for Gold Acceptor in Silicon                                                                                    | • | 30   |

| 11. | Measurements from Two <i>p</i> -Type Wafers Fabricated with <i>pnp</i> Process and<br>Test Pattern NBS-2; Run No. 2.5                        |   | 43   |

| 12. | Epitaxial Layer Thickness in Micrometres Measured on MOS Capacitors<br>Along Slice Diameters by the Step-Relaxation Method                   |   | 53   |

| 13. | Summary of NDP Force Recommendations                                                                                                         | • | 62   |

| 14. | Flow and Flow Rate Characteristics for Channel Leaks of 1-mm Length<br>for Air at 25°C                                                       | • | 69   |

| 15. | Channel Leak Flow Rate Limits and Leak Rates Relative to Air for Gases other than Air                                                        |   | 69   |

| 16. | Cumulative Radiation Levels for Lot 1 Diodes                                                                                                 |   | 75   |

The Semiconductor Technology Program serves to focus NBS efforts to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in specifying materials and devices in national and international commerce and for use by industry in controlling device fabrication processes. Its major thrusts are the development of carefully evaluated and well documented test procedures and associated technology and the dissemination of such information to the electronics community. Application of the output by industry will contribute to higher yields, lower cost, and higher reliability of semiconductor devices. The output provides a common basis for the purchase specifications of government agencies which will lead to greater economy in government procurement. In addition, improved measurement technology will provide a basis for controlled improvements in fabrication processes and in essential device characteristics.

The Program receives direct financial support principally from three major sponsors:

the Defense Advanced Research Projects Agency (ARPA), the Defense Nuclear Agency (DNA), the Defense Nuclear Agency (DNA),

and the National Bureau of Standards (NBS).<sup>×</sup> The ARPA-supported portion of the Program, Advancement of Reliability, Processing, and Automation for Integrated Circuits with the National Bureau of Standards (ARPA/IC/NBS), addresses critical Defense Department problems in the yield, reliability, and availability of integrated circuits. The DNA-supported portion of the Program emphasizes aspects of the work which relate to radiation response of electron devices for use in military systems. There is considerable overlap between the interests of DNA and ARPA. Measurement oriented activity appropriate to the mission of NBS is a critical element in the achievement of the objectives of both other agencies.

Essential assistance to the Program is also received from the semiconductor industry through cooperative experiments and technical exchanges. NBS interacts with industrial users and suppliers of semiconductor devices through participation in standardizing organizations; through direct consultations with device and material suppliers, government agencies, and other users; and through periodically scheduled symposia and workshops. In addition, progress reports, such as this one, are regularly prepared for issuance in the NBS Special Publication 400 sub-series. More detailed reports such as state-of-the-art reviews, literature compilations, and summaries of technical efforts conducted within the Program are issued as these activities are completed. Reports of this type which are published by NBS also appear in the Special Publication 400 sub-series. Announcements of availability of all publications in this sub-series are sent by the Government Printing Office to those who have requested this service. A request form for this purpose may be found at the end of this report.

\*

Through ARPA Order 2397, Program Code 4D10 (NBS Cost Center 4259555).

<sup>\*</sup> Through Inter-Agency Cost Reimbursement Order 74-811 (NBS Cost Center 4259522).

<sup>\*</sup> Through Scientific and Technical Research Services Cost Centers 4251126, 4252128, and 4254115.

# SEMICONDUCTOR MEASUREMENT TECHNOLOGY

COMBINED QUARTERLY REPORT October 1, 1973 to March 31, 1974

Abstract: This combined quarterly progress report describes NBS activities directed toward the development of methods of measurement for semiconductor materials, process control, and devices. The emphasis is on silicon device technologies. Principal accomplishments during this reporting period include (1) identification of major problem areas in connection with measuring and inspecting photomasks, (2) development of a mathematical model suitable for interpreting thermally stimulated current and capacitance measurements on junction diodes and metal-oxide-semiconductor (MOS) capacitors, (3) completion of a preliminary evaluation of a method, based on the transient capacitancevoltage characteristic of an MOS capacitor, for measuring thickness of epitaxial layers up to 2 µm thick, and (4) development of criteria for use in nondestructive wire bond pull tests. Results are also reported on spreading resistance, capacitance-voltage, and carrier mobility measurements; polynomial fits for energy band gap and hole and electron effective masses in silicon; methods for characterizing oxide films; evaluation of sheet resistance and collector resistor test structures; evaluation of a photoresist spinner test; scanning electron microscopy; bonding of aluminum ribbon wire to thick film copper; bonding of platinum wire to thin film aluminum; leak rate calculations in the transition flow regime; transistor thermal response measurements; and radiation response of microwave mixer diodes. Supplementary data concerning staff, publications, workshops and symposia, standards committee activities, and technical services are also included as appendices.

Key Words: Boron redistribution; collector resistor; dopant profiles; effective mass; electrical properties; electron beam induced current mode; electronics; epitaxial layer thickness; flying spot scanner; gold-doped silicon; hermeticity; ion microprobe mass analysis; methods of measurement; microelectronics; microwave diodes; mobility; MOS devices; oxide films; photomasks; photoresist; platinum wire; resistivity; resistivity standards; ribbon wire; scanning electron microscopy; semiconductor devices; semiconductor materials; semiconductor process control; sheet resistance; silicon; spreading resistance; test patterns; thermal response; thermally stimulated capacitance; thermally stimulated current; thick film copper; voltage contrast mode; wire bonds; X-ray photoelectron spectroscopy.

# 1. INTRODUCTION

This is a report to the sponsors of the Semiconductor Technology Program on work during the twenty-second and twenty-third quarters of the Program. It summarizes work on a wide variety of measurement methods for semiconductor materials, process control, and devices that are being studied at the National Bureau of Standards. The Program, which emphasizes silicon-based device technologies, is a continuing one, and the results and conclusions reported here are subject to modification and refinement.

The work of the Program is divided into a number of tasks, each directed toward the study of a particular material or device property or measurement technique. This report is subdivided according to these tasks. Highlights of activity during the quarter are given in section 2. Subsequent sections deal with each specific task area. References cited are listed in the final section of the report.

#### INTRODUCTION

The report of each task includes a narrative description of progress made during this reporting period. Additional information concerning the material reported may be obtained directly from individual staff members identified with the task in the report. The organization of the Program staff and telephone numbers are listed in Appendix A.

Background material on the Program and individual tasks may be found in earlier quarterly reports as listed in Appendix B. From time to time, publications are prepared that describe some aspect of the program in greater detail. Current publications of this type are also listed in Appendix B. Reprints or copies of such publications are usually available on request to the author.

Communication with the electronics community is a critical aspect both as input for guidance in planning future program activities and in disseminating the results of the work to potential users. Formal channels for such communication occur in the form of workshops and symposia sponsored or co-sponsored by NBS. Currently scheduled seminars and workshops are listed in Appendix C. In addition, the availability of proceedings from past workshops and seminars is indicated in the appendix.

An important part of the work that frequently goes beyond the task structure is participation in the activities of various technical standardizing committees. The list of personnel involved with this work given in Appendix D suggests the extent of this participation. In most cases, details of standardization efforts are reported in connection with the work of a particular task.

Technical services in areas of competence are provided to other NBS activities and other government agencies as they are requested. Usually these are short-term, specialized services that cannot be obtained through normal commercial channels. To indicate the kinds of technology available to the Program, such services provided during the period covered by this report are listed in Appendix E. Particularly significant accomplishments during this reporting period include (1) identification of major problem areas in connection with measuring and inspecting photomasks, (2) development of a mathematical model suitable for interpreting thermally stimulated current and capacitance measurements on junction diodes and metal-oxide-semiconductor (MOS) capacitors, (3) completion of a preliminary evaluation of a method, based on the transient capacitance-voltage characteristic of an MOS capacitor, for measuring thickness of epitaxial layers up to 2 µm thick, and (4) development of criteria for use in nondestructive wire bond pull tests.

In addition, the second ARPA/NBS Workshop, on hermeticity, was held at NBS Gaithersburg. This workshop focussed on problems with correlation between various methods for testing semiconductor device packages for fine leaks, the lack of correlation between device failure and leaks in the fine leak range, and the need for an objective, quantitative test procedure for measuring leaks in the gross leak range. A separate report is being prepared on the discussions and conclusions of the workshop.

The following are highlights of these and other activities during this reporting period.

Resistivity; Dopant Profiles — An investigation was initiated to determine the relationships, if any, which exist between the surface morphology of the probe tips used for spreading resistance measurements and their electrical behavior. The junction capacitance-voltage

technique was successfully applied to gated diodes formed by diffusing an  $n^{+}$  layer into a uniformly doped p-type silicon wafer or epitaxial film. Mathematical analysis of the boron redistribution problem continued with the development of procedures for solving the appropriate equations by the method of heat potentials. Curves were calculated to relate the surface dopant density of a diffused layer to the sheet resistance-junction depth product, taking into account the penetration of the zero-bias space charge region into the diffused layer; this correction is important for films with sheet resistance in excess of 0.8 k $\Omega/\sigma$ . In cooperation with ASTM Committee F-1 on Electronics, experimental work was undertaken to redetermine the relationships between resistivity, carrier density, and carrier mobility in silicon. In response to a request from the industry, a computer program was written to calculate dopant density as a function of silicon resistivity using empirical expressions for the relationship between carrier mobility and dopant density found in the literature. Polynomials were developed which describe the temperature dependence of the hole and electron masses and the energy band gap of silicon. An analysis was completed of procedures which can be used to eliminate misalignment or magnetoresistance voltages when calculating the Hall coefficient from measured values of the Hall voltage when the forward and reverse magnetic flux densities are not equal. A small-scale experiment, designed to test the ability of various laboratories to measure the probe force of pins mounted in a four-probe head, showed that for probe forces near 0.30 N the variability was in excess of that permitted by the requirements of the ASTM method for measuring sheet resistance on epitaxial silicon wafers.

Crystal Defects and Contaminants — A physical model has been developed and applied to the experimental results obtained for the dynathermal current and capacitance response of the gold acceptor center in silicon. This model satisfactorily predicts the shift in the thermally stimulated current characteristics with heating rate for the single peak in the case of a p-n junction and both peaks in the case of an n-MOS capacitor.

Oxide Film Characterization — An analysis was made of the errors which could arise in the capacitance measurement as a result of excessive loss due to high contact resistance on the backside, high series body resistance, or capacitance and conductance of a backside oxide in an MOS capacitor when measuring the capacitance-voltage characteristics. Studies of the bias-temperature stress test were begun; a prototype apparatus has been constructed and preliminary measurements made on an oxide layer fabricated in-house. Several techniques were examined for creating a shallow, uniformly sloped region through the oxidized surface of a silicon wafer; such a slope is necessary to make depth profile measurements with the ion microprobe mass analyzer. Preliminary study of the silicon-oxygen system by means of x-ray photoelectron spectroscopy (also known as electron spectroscopy for chemical analysis) revealed the presence of carbon near the surface. The origin of this carbon is being investigated in some detail in order to establish whether it is an artifact of the measurement or whether it comes from the specimen itself; should it be found to come from the surface or bulk of the specimen, it would be of considerable interest in connection with the operation of MOS devices.

#### HIGHLIGHTS

Test Patterns — The process previously used to fabricate gated  $p^{+}n$  junctions and *n*-MOS capacitors was modified by interchanging the emitter and base diffusions in order to fabricate gated  $n^{+}p$  junctions and *p*-MOS capacitors. A detailed analysis of the collector resistor test structure on test pattern NBS-2 revealed several possible limitations; five new structures have been designed and incorporated into a new test pattern in order to permit additional experiments which are expected to lead to a fuller understanding of the current patterns in collector resistor structures for measuring sheet resistance of thin layers; a gated van der Pauw structure is being included in the new test pattern. Design work is nearing completion on another test pattern which includes a variety of charge-coupled devices as well as more conventional test structures.

Photolithography — In connection with the definition of a program to be undertaken in this area, visits were made to 26 device manufacturers, photomask and photoresist suppliers, and manufacturers of mask alignment or inspection equipment. Indications are that major problems exist in connection with standards for line width measurement and with procedures for edge definition, inspection of both masks and unexposed photoplates for defects, and alignment of a series of photomasks. Preliminary results of an analysis of the usefulness of absolute radiometric measurements to standardize and control photoresist exposure suggest that exposure control can be improved by the use of a light integrator, but that use of absolute radiometry would not be necessary. An evaluation was made of the repeatability of a method for measuring the rotational acceleration and velocity of a wafer during the spinning process used in photoresist coating; this method is being considered for adoption by ASTM Committee F-1 on Electronics.

Epitaxial Layer Thickness — To address a need expressed by the semiconductor device industry for methods of measuring the thickness of epitaxial layers less than 2  $\mu$ m thick, a new method which makes use of the transient high-frequency capacitance-voltage characteristic of an MOS capacitor is being evaluated. This method, with some limitations, is applicable to the measurement of such thin layers when the layer and substrate are of the same conductivity type and when the substrate is much more heavily doped than the layer.

Wafer Inspection and Test — To prepare for the study of the extent of damage to microelectronic devices when examined in a scanning electron microscope, in connection with work toward non-contacting measurements on finished devices at the wafer level, measurements of the total electron beam current of the scanning electron microscope were made as a function of accelerating potential, condenser lens current, and objective lens current. In addition, a flying spot scanner is being assembled to evaluate electrical properties of devices before and after exposure to the electron beam. A cylindrical detector intended to increase the sensitivity of the scanning electron microscope in the voltage contrast mode was assembled and installed. Relatively simple relationships were developed between the carrier generation rate in an aluminum-silicon dioxide-silicon structure and the accelerating potential and the beam current of the scanning electron microscope to assist in predicting the magnitude of signals to be expected when examining MOS and bipolar devices in the electron beam induced current mode.

Interconnection Bonding - Experiments were completed which demonstrate that aluminum ribbon wire can be satisfactorily bonded to thick film copper conductors and used in typical hybrid circuit processing environments; thus, for many hybrid circuit applications it may be possible to replace gold thick films with less expensive copper thick films. On further investigation, it was found that the use of small diameter platinum wire in ultrasonic bonding to silicon device metallization is not likely to be satisfactory because of the occurrence of severe damage to the silicon wafer under the bond. A versatile instrument was built to pull beam lead devices or wire bonds made by either thermocompression or ultrasonic bonding techniques. Work was completed on the development of the metallurgical and statistical rationales for a nondestructive wire bond pull test and the determination of maximum permissible force limits applicable for a wide variety of wire sizes, both hard drawn and annealed. Destructive double-bond pull tests, conducted on a number of power devices bonded with large diameter annealed aluminum wire, revealed that the principal failure mode is breakage in the wire span and that the electrical discharge weld made to the gold plated post often forms at the perimeter of the bond in the same manner as was observed previously for ultrasonic bonds made with small diameter aluminum wire. A preliminary evaluation was made of a technique

#### **HIGHLIGHTS**

for directly observing the bond formed between small diameter aluminum wire and aluminum metallization deposited on glass slides. Mathematical modeling of the motion of an ultrasonic wire bonding tool was undertaken to determine the mechanisms by which the metallurgical weld is formed and to lay the basis for a quantitative in-process bond monitoring scheme.

Hermeticity — ASTM Committee F-1 on Electronics was assisted in prepairing a final draft procedure and schedule for the interlaboratory evaluation of the helium mass spectrometer method for testing fine capillary leaks in large volume containers. A sensitive mass spectrometer was designed and is being constructed to evaluate the use of this type of instrumentation for the measurement of trace elements in the semiconductor processing environment and on wafer surfaces as well as for the investigation of gas flow mechanisms in leaks in hermetic packages. Initial calculations were made of gas flow in leaks of a size likely to be encountered in semiconductor device packages; these calculations, which took into account both the molecular flow and laminar viscous flow mechanisms, verified the need for more realistic examination of flow mechanisms and their effect on the relationship between indicated leak rate and true leak rate. A novel procedure for a dry, quantitative gross leak test was conceived and is being evaluated.

Thermal Properties of Devices — The transient thermal response of power semiconductor devices as measured by both the pulsed heating curve technique and the cooling curve technique was studied. It was found both experimentally and theoretically that the cooling curve technique, which is more widely used because of its simplicity, is equivalent to the pulsed heating curve technique, which more closely simulates the response of interest in an application, only under idealized conditions. In general, the cooling curve technique was found to give a larger value for thermal impedance than that which would be obtained under actual single pulse operating conditions.

Microwave Diodes — As an outgrowth of the development of precise methods for characterizing the properties of X-band mixer diodes, a preliminary assessment was made of the response to gamma and neutron irradiation of Schottky-barrier diodes designed as direct replacements for military grade 1N23 point-contact diodes. No significant permanent damage effects were observed at gamma dosages up to  $10^7$  rads (Si) and neutron fluences up to  $10^{15}$  cm<sup>-2</sup>. Small effects were observed at neutron fluences of about  $5 \times 10^{-15}$  cm<sup>-2</sup>.

Dissemination Activities — Organizational activities were completed for the Workshop on Radiation Effects in MOS Technology. This workshop co-sponsored the IEEE Nuclear and Plasma Sciences Society, the IEEE Electron Devices Group, and NBS, was held December 6 and 7, 1973 in Washington. No proceedings of this workshop were printed.

Planning activity was completed for the Spreading Resistance Symposium, scheduled for June 13 and 14, 1974; at NBS Gaithersburg. This symposium is being jointly sponsored by ASTM Committee F-1 on Electronics and NBS. The proceedings, which will include summaries of discussion at the meeting, will be made available as an NBS Special Publication.

Test patterns were selected as the subject of the third ARPA/NBS Workshop scheduled for September 6 in Scottsdale, Arizona following the fall meeting of ASTM Committee F-1. This workshop, which is a logical follow-on to a mini-symposium on test patterns held as part of the January meeting of the Committee, will discuss MOS and bipolar test structures and acquisition systems for test structure data from both production and laboratory view points.

5

#### 3.1. Spreading Resistance Methods

While continuing the development of a calibration curve for the spreading resistance instrument on p-type silicon slices (NBS Tech. Note 806, pp. 9-10) erratic behavior was encountered in the instrument. This behavior was manifested by variability greater than 10 percent in the spreading resistance during periodic tests on a  $2-\Omega \cdot cm$ , chem-mechanically polished, p-type reference slice. Although this variability was thought to be due to changes in the operating characteristics of the probe tips, it could not be remedied by running about 1000 probe impressions on a lapped silicon surface, a simple technique which had previously proven successful in clearing up erratic probe behavior. Consequently, a variety of probe tips was examined microscopically and electrically to determine the nature of both good and bad tips and the relationships, if any, between tip surface morphology and electrical behavior.

In the initial investigation, styli consisting of various osmium or tungsten carbide alloys, acquired from various suppliers, and having radii of curvature from about 19 to about 250  $\mu$ m were mounted for use as spreading resistance probes. Most styli were tested as supplied by the manufacturer with the exception of two which had been conditioned by running 2000 to 4000 impressions on a lapped silicon surface to yield stable spreading resistance measurements and two on which such conditioning had been attempted but which failed to yield probes adequate for spreading resistance measurements.

To test the electrical characteristics of the probes, spreading resistance measurements were made on the *p*-type reference slice used in the calibration curve development effort to verify probe stability. A range of 600 to 1000  $\Omega$  has been found previously to be typical of the response of a good probe on this reference slice. The probes tested yielded values from

about 500  $\Omega$  to values between 10<sup>6</sup> and 10<sup>8</sup>  $\Omega$ . This latter range of response included one stylus with a nominal radius of 25  $\mu$ m, two with a nominal radius of 125  $\mu$ m, and one with a nominal radius of 250  $\mu$ m. On these four probes, no conditioning had been attempted.

Scanning electron micrographs were then taken of the various probe tips at a magnification of about 1000  $\times$  and of the damage tracks left in a polished silicon surface by these probes at a magnification of about 4000  $\times$ . Also differential interference optical photomicrographs were taken of the probe damage tracks. No damage mark was visible on a polished silicon surface under either scanning electron or differential interference optical micros-

copy for any of the four probes which yielded electrical resistance values above  $10^6 \Omega$ . In most cases the surface of the stylus tip was rather flat, perhaps 80 percent consisting of the alloy and 20 percent being small voids. A typical example is the scanning electron micrograph of one of the 125  $\mu$ m radius tips shown in figure 1.

With exception of one osmium stylus with a radius of 50  $\mu$ m which had a relatively smooth surface and reasonably low resistance, the rougher or more granular the surface of the probe, the lower was the measured spreading resistance. The ability of a rougher probe to form a number of individual microcontacts appears to enhance its ability to make a relatively low resistance contact. In fact after a very light abrasion of the other 125  $\mu$ m radius tip with fine aluminum oxide paper, the surface was greatly roughened as shown in figure 2 and the contact resistance dropped to the range 650 to 800  $\Omega$ .

In addition to low contact resistance, it is also desirable to have a contact with well defined geometry, preferably circular and compact, to aid in analytical modeling of the potential distribution beneath the contact. Furthermore, under some conditions a probe can fracture and otherwise damage the silicon surface to a depth which can complicate the interpretation of measurements of depth profiles in thin layers or in multilayered structures. Differences in probe impression characteristics are frequently not visible in Nomarski optical photomicrographs of the probe imprint but they can be seen in scanning electron micrographs under much greater magnification. Imprints of two probes with about the same contact resistance are shown in figure 3. The Nomarski optical photomicrographs of the imprints are quite similar while the scanning electron micrographs shown significant differences. The conchoidal fracture and related damage in the scanning electron micrograph of figure 3d may cause electrical punch through of thin layers and may complicate or even invalidate the results of measurements of depth profiles of thin layers or of multilayered structures. Sin damage of this type is not visible optically, it may be necessary to develop a thin film reference structure for use in verifying that a given set of probes is making electrical con tact only to the surface layer of the specimen. (J. R. Ehrstein)

6

Figure 1. Scanning electron micrograph of tip of an unconditioned tungsten carbide spreading resistance probe with a nominal radius of 125  $\mu$ m. (Magnification:  $\sim$  1000 X).

Figure 2. Scanning electron micrograph of a lightly abraded tungsten carbide spreading resistance probe with a nominal radius of 125  $\mu m$ . (Magnification:  $\sim$  1000 X).

a. Nomarski photomicrograph, Probe MSF, Magnification: ~ 850 X.

c. Scanning electron micrograph, Probe MSF, Magnification: ∿ 6400 X.

b. Nomarski photomicrograph, Probe 1WKA-1, Magnification: ~ 850 X.

d. Scanning electron micrograph, Probe 1WKA-1 Magnification: ~ 6400 X.

Figure 3. Imprints of two spreading resistance probes with about the same contact resistance.

#### 3.2. Junction Capacitance-Voltage Method

Experimental investigation of the junction capacitance-voltage (C-V) method, previously directed toward understanding of measurements on *n*-type silicon (NBS Tech. Note 788, pp. 9-11), was extended to measurements on *p*-type silicon wafers. Measurements on *p*-type silicon are generally more difficult because the surface of the wafer can be inverted due to positive charge in the oxide. In addition, the surface region is frequently depleted of dopant because of boron redistribution during oxidation.

Gated  $n^{+}p$  diodes were fabricated (see sec. 6.1.) in 11 *p*-type bulk or epitaxial wafers using test pattern NBS-2 (NBS Tech. Note 788, pp. 15-17). The diodes were about 0.5 mm (20 mils) in diameter, the diffused layer sheet resistance was about 3.5  $\Omega/\Box$ , and the junction depth was about 2.7  $\mu$ m. Capacitance-voltage measurements were made on one diode on each wafer with the gate biased at the flat band potential as determined from C-V measurements on

an MOS capacitor located near the  $n^{\tau}p$  diode. The diodes measured were located near the center of the wafer except that an off-center diode was measured on wafer 3001 which had been broken.

The junction capacitance was measured in the dark at room temperature with a capacitance meter having a test signal of 15 mV rms at 1 MHz at reverse biases ranging from about 2 V to

a maximum value V limited by the junction breakdown voltage. Each succeeding voltage was

chosen to cause the capacitance to decrease by about 10 percent from the preceding value. Dopant density profiles were then calculated from adjacent C-V pairs, taking into account both peripheral and diffused layer effects [1].

The results of these measurements are shown in table 1 where  $\overline{N}$  is the average dopant density and s is the relative sample standard deviation of each profile. Also shown in table 1 are the number of C-V pairs used in the computation, the maximum applied reverse bias,  $V_{max}$ , and the flat-band voltage,  $V_{fb}$ . The dopant profiles for the wafers are quite

flat; only one of the profiles had a relative sample standard deviation greater than

2 percent. The gold-doped wafers had a gold density of only about  $10^{13}$  cm<sup>-3</sup> which is small enough that it did not affect the profiles. It should be noted that flat profiles were achieved even though the flat-band voltage ranged from -0.5 to -12.6 V.

(R. L. Mattis and M. G. Buehler)

#### 3.3. Mathematical Models of Dopant Profiles

A mathematical model was developed for use in solving the problem of redistribution of boron in silicon during thermal oxidation and diffusion. Mathematically stated, the redistribution problem consists of finding the solution to a pair of partial differential equations which are coupled through their boundary conditions. A reformulation of this mathematical problem was effected by using the method of heat potentials [2,3], so that instead of solving the partial differential equations one need only solve a more tractable system of integral equations.

The mathematical model is built on an extension of the physical model described previously (NBS Spec. Publ. 400-1, pp. 9-11). In the physical model, two domains, the oxide and the silicon, were defined. In the extension, the oxide thickness before oxidation (t<0) may be either zero or nonzero. The oxide domain covers the region  $0 < z < z_0(t)$ ,  $t \ge 0$ , where z is a moving coordinate system referenced to the front surface of the oxide and  $z_0(t)$  is the total oxide thickness. The silicon domain in the extension of the physical model is bounded,  $y_0(t) < y < L$ ,  $t \ge 0$ , where y is the laboratory coordinate system referenced to the original front surface of the silicon (i.e.,  $y_0(0) = 0$ ),  $y_0(t)$  is the oxide-silicon interface, and L is the thickness of the silicon wafer (assumed in the previous formulation to be semi infinite, i.e.,  $L \rightarrow \infty$ ). The oxide thickness is assumed to increase parabolically with time:  $z_0(t) = z_0(0) + At^{1/2}$ . The ratio of the thickness of silicon consumed during oxidation to the increase in oxide thickness is assumed constant:  $y_0(t)/[z_0(t) - z_0(0)] = \alpha$ . The two coordinate systems are related by:  $z - z_0(t) = y - y_0(t)$ , and the origin of the z-axis is convected away from the original silicon surface with a time dependent velocity,  $(1 - \alpha)A/2t^{1/2}$ . In a third extension of the original model the initial boron distribution

in both the oxide and the silicon may vary with position. Following the method of heat potentials, the density of boron in the oxide,  $C_1(z,t)$ ,

and the density of boron in the silicon,  $C_2(y,t)$  are defined by sums of four integral expressions. These expressions contain only two unknown functions,  $Q(\tau)$  and  $R(\tau)$ . When  $Q(\tau)$  and  $R(\tau)$  satisfy two appropriate Volterra-type integral equations, it can be shown that  $C_1(z,t)$

and  $C_2(y,t)$  satisfy the diffusion equations

$\frac{\partial C_1(z,t)}{\partial t} = D_1 \frac{\partial^2 C_1(z,t)}{\partial z^2} \quad (in the oxide)$

and

$$\frac{\partial C_2(\mathbf{y}, \mathbf{t})}{\partial \mathbf{t}} = D_2 \frac{\partial^2 C_2(\mathbf{y}, \mathbf{t})}{\partial \mathbf{y}^2} \quad (\text{in the silicon})$$

with the initial conditions

9

| Specimen<br>No. | Wafer         | ₩, cm <sup>-3</sup>     | s, % | Number of<br>CV Pairs | V <sub>max</sub> , V | ۷ <sub>fb</sub> , ۷ |

|-----------------|---------------|-------------------------|------|-----------------------|----------------------|---------------------|

| 3001            | Bulk          | 1.41 × 10 <sup>15</sup> | 0.86 | 14                    | 46.6                 | -6.0                |

| 3002            | Bulk          | 1.56                    | 0.84 | 13                    | 41.5                 | -12.6               |

| 3003            | Bulk          | 1.44                    | 0.67 | 13                    | 40.5                 | -10.4               |

| 3004            | Bulk Au-doped | 1.39                    | 1.06 | 14                    | 48.5                 | -7.4                |

| 3005            | Bulk Au-doped | 1.50                    | 1.31 | 14                    | 43.3                 | -4.0                |

| 3006            | Bulk Au-doped | 1.41                    | 1.49 | 14                    | 43.3                 | -2.5                |

| 4001            | Epi           | 0.73                    | 1.82 | 12                    | 27.0                 | -6.5                |

| 4002            | Epi           | 0.79                    | 1.85 | 12                    | 30.4                 | -6.3                |

| 4003            | Epi           | 1.47                    | 2.60 | 14                    | 41.0                 | -5.0                |

| 4004            | Epi Au-doped  | 1.43                    | 1.06 | 14                    | 51.9                 | -1.9                |

| 4006            | Epi Au-doped  | 1.42                    | 1.17 | 15                    | 55.5                 | -0.5                |

Table 1 — Summary of p-Type Dopant Density Profiles, Run No. 2.5

$$C_1(z,0) = C_{b_1}(z), (0 \le z \le z_0(0))$$

and

$$C_2(y,0) = C_{b_2}(y), (y_0(0) \le y \le L)$$

and, for t>0, the boundary conditions

$$C_{1}(0,t) = C_{s}(t)$$

$$C_{2}(y_{0}(t),t) = m C_{1}(z_{0}(t),t)$$

$$(m\alpha - 1) C_{1}(z_{0}(t),t) \frac{\partial z_{0}(t)}{\partial t} = D_{1} \frac{\partial C_{1}(z,t)}{\partial z} \bigg|_{z} = z_{0}(t) - D_{2} \frac{\partial C_{2}(y,t)}{\partial y} \bigg|_{y} = y_{0}(t)$$

$$C_{2}(L,t) = C_{t}(t)$$

where  $D_1$  and  $D_2$  are the diffusion coefficients of the boron in silicon dioxide and silicon, respectively;  $C_s$  is the density of boron at the front surface of the oxide,  $C_{b_1}$  and  $C_{b_2}$  are the initial densities of boron in the oxide and in the silicon, respectively, and m is the segregation coefficient of boron.

The two Volterra-type integral equations are too complicated to solve analytically in situations of practical interest, so they are being solved numerically [4]. First, the continuous variable  $\tau$  is replaced by n uniformly spaced grid points { $\tau_i$ } with

$j = 1, 2, 3, \ldots, n$ . One then evaluates each integral equation at each grid point,  $\tau_j$ . The indefinite integrals in the equations are replaced by finite sums by employing a quadrature rule, using the set  $\{\tau_j\}$  as node points. In the usual case, the result is a solvable system of 2n equations in the 2n unknowns  $Q(\tau_i)$  and  $R(\tau_i)$ .

However, these Volterra-type equations differ in two significant ways from the type of equations usually encountered. The first difference is that the kernels of the present

equations are singular. Special care must be taken when quadrature techniques are applied to integrals with such kernels. In the present case, product integral quadrature techniques [5] are being used.

The other unusual aspect of these integral equations occurs because the time derivative of  $Q(\tau)$  appears in an integral in addition to the functions  $Q(\tau)$  and  $R(\tau)$ . Consequently, it is more convenient to use Haber's method [6] to solve the system of integral equations. In Haber's method one does not solve directly for the  $Q(\tau_j)$  and  $R(\tau_j)$ . Instead it is assumed that  $Q(\tau)$  and  $R(\tau)$  are piecewise linear in each interval  $[\tau_i, \tau_{i+1}]$  for

$j = 1, 2, 3, \ldots, n$  1. Thus, for the interval  $\tau_j \ge \tau \ge \tau_{j+1}$ ,

$$Q(\tau) \equiv Q(\tau_j) + A_Q(\tau_j)(\tau - \tau_j)$$

(1)

and

$$R(\tau) \equiv R(\tau_j) + A_R(\tau_j)(\tau - \tau_j), \qquad (2)$$

where the slopes  $A_Q(\tau_j)$ ,  $A_R(\tau_j)$ , j = 1, 2, 3, ..., n - 1 are unknown. When these piecewise linear approximations are substituted for  $Q(\tau)$  and  $R(\tau)$  in the integral equations and these integral equations are then made discrete, as described above, there results a solvable, linear algebraic system of equations in the 2(n - 1) unknown slopes  $A_Q(\tau_j)$  and  $A_R(\tau_j)$ . Once the values of these slopes are known the originally sought after values of  $Q(\tau_j)$  and  $R(\tau_j)$  can be recovered from eqs (1) and (2). The initial values,  $Q(\tau_1)$  and  $R(\tau_1)$ , follow immediately from evaluating the Volterra equations at  $\tau = \tau_1$ . A computer program employing these procedures has been written in FORTRAN IV. (S. R. Kraft<sup>\*</sup> and M. G. Buehler)

#### 3.4. Diffused Layer Sheet Resistance

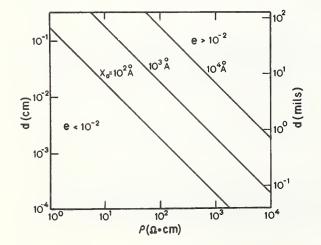

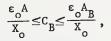

In the fabrication of semiconductor devices it is common practice to obtain the surface dopant density,  $N_0$ , of a diffused layer from the measurement of the diffused layer sheet resistance,  $R_s$ ; the junction depth,  $X_j$ ; the background dopant density,  $N_b$ ; and an assumed functional form for the diffused layer. Previously (NBS Spec. Publ. 400-1, pp. 11-14) curves of  $N_0$  as a function of  $R_{sj}$  were developed for both p- and n-type Gaussian diffused layers with various values of  $N_b$ . In developing these curves the entire diffused layer was assumed to be conducting; restricted conduction due to the penetration of the space-charge region into the layer was not considered. It is shown here that this effect becomes important for shallow junction depths and high sheet resistance values.

The problem is illustrated in figure 4 where the true surface dopant density,  $N_0(A_0\neq 0)$ , takes into account the penetration of the zero-bias space charge region  $A_0$  into the diffused layer. In a usual calculation,  $A_0$  is taken to be zero, and the apparent surface dopant density,  $N_0(A_0=0)$ , is calculated. The ratio  $N_0(A_0\neq 0)/N_0(A_0=0)$ , calculated at various  $R_s$  and  $N_b$  values, is shown in figure 5 for a *p*-type Gaussian layer with a 0.1 µm junction depth.

The procedure for computing the values shown in figure 5 is as follows. First, values for  $X_j$ ,  $N_b$ , and  $N_0$  are assumed for a Gaussian diffusion. Then  $A_0$  is found numerically [1] by equating the total junction potential (eq (12), ref 1) to the Boltzmann relation for the built-in voltage (eq (13), ref 1) while satisfying Gauss' law for the junction (eq (5), ref 1). Next, the true sheet resistance is calculated from the surface to  $A_0$  from the expression:

\* NBS Applied Mathematics Division

Figure 4. Dopant density profile of a diffused layer showing true  $[N_0(A_0\neq 0)]$  and apparent  $[N_0(A_0=0)]$  surface dopant density.

Figure 5. Ratio of true to apparent surface dopant density of a *p*-type Gaussian diffused junction, 0.1 µm deep, as a function of sheet resistance, for various values of background dopant density, N<sub>b</sub>. (A: N<sub>b</sub> =  $10^{14}$  cm<sup>-3</sup>; B: N<sub>b</sub> =  $10^{15}$  cm<sup>-3</sup>; C: N<sub>b</sub> =  $10^{16}$  cm<sup>-3</sup>; D: N<sub>b</sub> =  $10^{17}$  cm<sup>-3</sup>; E: N<sub>b</sub> =  $10^{18}$  cm<sup>-3</sup>).

$R_{s}^{-1} = q \int_{0}^{A_{0}} \mu(N - N_{b}) dx$ ,

where q is the electronic charge,  $\mu$  is given by [7]:

$$\mu = 47.7 + \left( \frac{447}{\left[ 1 + \left( \frac{N + N_b}{1.9 \times 10^{17}} \right)^{0.76} \right]} \right)$$

(in square centimetre per volt second with dopant density given in inverse cubic centimetre),  $N = N_0 \exp(-x^2/L^2)$ , and  $L = X_j [\ln(N_0/N_b)]^{1/2}$ . Finally the apparent surface dopant density is computed numerically from eq (3) using the true sheet resistance as calculated above but now assuming  $A_0 = 0$ .

The curves shown in figure 5 indicate that the effect on the surface dopant density is greater than 4 percent for sheet resistances above  $1 \ k\Omega/\Box$ . This range of values is important for high value resistors which have sheet resistance values ranging from 0.8 to 11  $k\Omega/\Box$  [8]. Other junction depth values have been studied namely, 0.05 and 0.2 µm. For these values the curves are similar to figure 5, for the curves are not strongly dependent on X<sub>1</sub> values.

(T. E. Griffin and M. G. Buehler)

(3)

#### 3.5. Reevaluation of Irvin's Curves

Irvin's curves [9], which relate the resistivity of both n- and p-type silicon to the density of dopant atoms, have been been widely used by the semiconductor industry during the past decade. There are various reasons to believe that the relationships for present day silicon deviate significantly from these curves in some regions (NBS Tech. Note 806, pp. 20-23). In particular, recent data on boron-doped silicon [7] are different from the data, mostly developed from measurements on gallium-doped silicon, used by Irvin to derive his curve for p-type silicon. In addition, uncertainties still remain in connection with the degenerate (heavily-doped) region for silicon of both conductivity types. In conjunction with the Mobility Section of ASTM Committee F-1 on Electronics, a plan

to reevaluate Irvin's curves has been established. Preliminary junction  $C-V^*$ , Hall effect, and four-probe resistivity measurements were made on a group of boron-doped silicon wafers under the auspices of the Mobility Section. The data are plotted in figure 6 with the curves of Irvin [9] and Wagner [7]. All of the experimental measurements were made at a temperature of 25 ± 2°C; the curves are for a temperature of 300 K (26.9°C). The resistivity, directly measured by the four-probe method is plotted as a function of ionized dopant density as determined by junction C-V (circles) or Hall effect (squares) measurements. In the latter, the scattering factor r, used to obtain the ionized doping density from the Hall coefficient, was taken from Runyan [10]. Care was taken to cut Hall bars from the center of a wafer where the four-probe measurements at one-half radius positions; radial variations of less than 2 percent were observed in all cases. The resistivity was also measured on the Hall bar and the values were within 2 percent of those obtained by the four-probe technique. Several of the wafers from which Hall bars were cut were from the same lot as those used for the capacitance-voltage measurements.

The abscissa for the curves of Irvin and Wagner is the total dopant density rather than the ionized density. At high impurity densities some of the impurity atoms may not be ionized so that a departure of the data points from the curves would not be surprising. Nevertheless, at present it must be concluded that the experimental data are in much better agreement with Wagner's curve than with Irvin's. (W. R. Thurber and M. G. Buehler)

#### 3.6. Computer Program to Calculate Dopant Density from Resistivity

Frequently it is desired to know the dopant density corresponding to a given value of silicon resistivity. The conversion can be done graphically by reference to the curves of Irvin [9] which have traditionally been used to relate resistivity to dopant density. However, for greater precision and convenience, it is useful to have an analytical procedure for the conversion which can be used in computer calculations. To meet this need a BASIC language [11] program was written to solve the equation which relates dopant density to resistivity. This equation can be written as follows:

$$N - \frac{1}{\rho q \mu (N)} = 0 \tag{4}$$

where N is the dopant density,  $\rho$  is the resistivity, q is the electron charge, and  $\mu(N)$  is the carrier mobility which is a function of the dopant density. The mobility equation used for *n*-type silicon is an empirical expression obtained by Caughey [12] to fit Irvin's curve. It is

$$\mu = \mu_{\min} + (\mu_{\max} - \mu_{\min}) / [1 + (N/N_{ref})^{\alpha}]$$

(5)

where  $\mu_{min} = 65 \text{ cm}^2/\text{V} \cdot \text{s}$ ,  $\mu_{max} = 1330 \text{ cm}^2/\text{V} \cdot \text{s}$ ,  $N_{ref} = 8.5 \times 10^{16} \text{ cm}^{-3}$ , and  $\alpha = 0.72$ .

The junction C-V and some of the four-probe measurements were made by B. L. Morris, Bell Telephone Laboratories, Allentown, Pa. 18103.

Figure 6. Resistivity as a function of dopant impurity density for *p*-type silicon. (The data points shown as circles were obtained from capacitance-voltage and four-probe resistivity measurements and the points shown as squares were derived from Hall effect and four-probe resistivity measurements. The curves are taken from the work of Irvin [9] and Wagner [7].)

The mobility equation for p-type silicon is from the work of Wagner [7] on boron-implanted implanted silicon. The expression is of the same form as eq (5), with the constants

$\mu_{min} = 47.7 \text{ cm}^2/\text{V} \cdot \text{s}, \ \mu_{max} = 495 \text{ cm}^2/\text{V} \cdot \text{s}, \ N_{ref} = 1.9 \times 10^{17} \text{ cm}^{-3}, \text{ and } \alpha = 0.76.$

The mobility equations were derived with the assumption that the carrier density is the same as the dopant density. This may not be the case at high dopant densities because of incomplete ionization of the dopant. This is a problem which is being studied as part of a project to reevaluate Irvin's curves (see sec. 3.5.). If new expressions for mobility result from this study, the present equations can simply be replaced with new ones.

Because of the nature of the mobility expressions it is necessary to solve a transcendental equation to obtain the dopant density. An iterative method is commonly used to solve this type of equation and the computer program to be described has been written using Newton's method of iteration. The desired solution is that value of N which satisfies eq (4) for a given value of  $\rho$ .

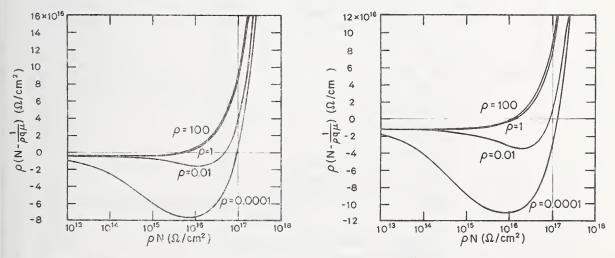

Before solving a transcendental equation it is instructive to examine a graph of the function in order to arrive at a method of solution which will give convergence. Plots of the left hand side of eq (4), multiplied by  $\rho$  for scaling purposes, as a function of  $\rho N$  are shown in figure 7 for both *n*- and *p*-type silicon with resistivity from 0.0001 to 100  $\Omega \cdot cm$ . Because of the minimum to the left of the zero crossing point in the curves for the low resistivities, it is necessary that the initial choice of N for Newton's method be on the right hand side of the minimum in order to obtain convergence. The plots in figure 7 indi-

cate that an initial choice of N by the equation N =  $1 \times 10^{17}/\rho$  will give convergence for

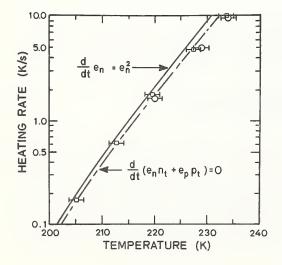

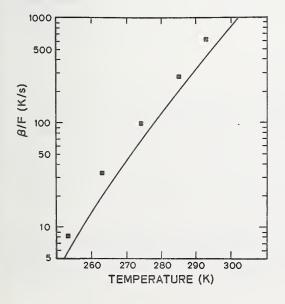

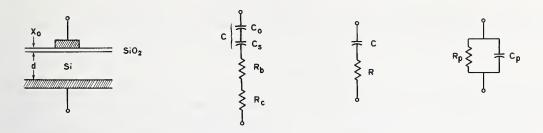

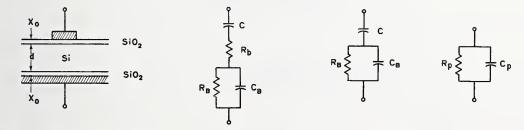

resistivities above  $10^{-4} \, \Omega \cdot \text{cm}$  for both types of silicon. For high values of resistivity there is no minimum in the curves, but it is still prudent to approach the zero crossing point from large N values.