# NBS SPECIAL PUBLICATION 400-31

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

Semiconductor Measurement Technology:

Techniques for Measuring the Integrity of Passivation Overcoats on Integrated Circuits

#### NATIONAL BUREAU OF STANDARDS

The National Bureau of Standards<sup>1</sup> was established by an act of Congress March 3, 1901. The Bureau's overall goal is strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To t end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific a technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to p mote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, the Office for Information Programs, and Office of Experimental Technology Incentives Program.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes ess tial services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industand commerce. The Institute consists of the Office of Measurement Services, and the following center and divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Center for Radiation Research — Loratory Astrophysics<sup>2</sup> — Cryogenics<sup>2</sup> — Electromagnetics<sup>2</sup> — Time and Frequency<sup>2</sup>.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of meast ment, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational in tutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials, the Office of and Water Measurement, and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services developing and promoting the use of as able technology; cooperates with public and private organizations in developing technological standards, codes, and test mods; and provides technical advice services, and information to Government agencies and the public. The Institute consists the following divisions and centers:

Standards Application and Analysis — Electronic Technology — Center for Consumer Product Technology: Proc Systems Analysis; Product Engineering — Center for Building Technology: Structures, Materials, and Safety; Build Environment; Technical Evaluation and Application — Center for Fire Research: Fire Science; Fire Safety Engineeri

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical serv designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the select acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the exutive branch for the development of Federal standards for automatic data processing equipment, techniques, and comp languages. The Institute consist of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE OF EXPERIMENTAL TECHNOLOGY INCENTIVES PROGRAM seeks to affect public policy and proto facilitate technological change in the private sector by examining and experimenting with Government policies and p tices in order to identify and remove Government-related barriers and to correct inherent market imperfections that imperfections the imperfection that imperfection the imperfection that imperfectio

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific infortion generated within NBS; promotes the development of the National Standard Reference Data System and a system of formation analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate served ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Librar, — Office of International Standards — Office of International Relations.

<sup>&</sup>lt;sup>1</sup> Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234. <sup>2</sup> Located at Boulder, Colorado 80302.

Semiconductor Measurement Technology:

# Techniques for Measuring the Integrity o-3) of Passivation Overcoats on Integrated Circuits

10-104. no. 4015-51

Werner Kern

TUS

and

Robert B. Comizzoli

RCA Laboratories Princeton, New Jersey 08540

This activity was supported by

The Defense Advanced Research Projects Agency and

The National Bureau of Standards

U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary

Dr. Betsy Ancker-Johnson, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Acting Director

Issued March 1977

Library of Congress Cataloging in Publication Data

Kern, Werner, 1925-

Techniques for measuring the integrity of passivation overcoats on integrated circuits.

(Semiconductor measurement technology) (National Bureau of Standards special publication; 400-31)

Supt. of Docs. no.: C 13.10:400-31.

1. Integrated circuits—Passivation. 2. Protective coatings—Testing. 3. Microelectronics—Quality control. I. Comizzoli, Robert B., joint author. II. Title. III. Series. IV. Series: United States. National Bureau of Standards. Special publication; 400-31. QC100.U57 no. 400-31 [TK7874] 602'.1s [621.381'73]

National Bureau of Standards Special Publication 400-31

Nat. Bur. Stand. (U.S.), Spec. Publ. 400-31, 120 pages (Mar. 1977) CODEN: XNBSAV

U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1977

#### PREFACE

This Final Report describes work performed from April 24, 1975 to April 30, 1976 in the Process and Applied Materials Research Laboratory of RCA Laboratories, Princeton, NJ, under Contract No. NBS5-35913. Paul Rappaport is the Laboratory Director, George L. Schnable is the Project Supervisor and Group Head, and Werner Kern, Member of the Technical Staff, is the Project Scientist. Additional members of the research team are Robert B. Comizzoli, Member of the Technical Staff; Edward C. Tracy, Research Associate; Ruth E. Allen and Robert D. Vibronek, Research Technicians.

The contract has been administered under Richard L. Raybold, Government Project Monitor, National Bureau of Standards, Department of Commerce, Washington, D.C. Thomas F. Leedy has been Assistant to the Government Project Monitor.

It is a pleasure to acknowledge the help of a number of individuals who have contributed to this work by the performance of specific research tasks, several analytical techniques, and sample preparation: E. C. Tracy - photomicrography, chemical etching, and uv fluorescence studies; R. E. Allen - electrical technology and photoresisting; R. D. Vibronek and A. W. Fisher - film deposition technology; B. J. Seabury - scanning electron microscopy; and G. R. Auth - profilometric measurements.

The authors wish to acknowledge especially the many fruitful discussions throughout the project with George L. Schnable, and his helpful comments and suggestions. We also acknowledge assistance by, and helpful discussions with, M. Blumenfeld, L. Greenberg, E. Jordan, W. Lawrence, and G. S. Lozier.

In some cases, for the sake of completeness or to provide desirable background information, this report contains results generated during RCA-supported research programs related to thin-film dielectrics, analytical method development, silicon device failure mechanisms and device processing.

It should be pointed out that most of the ICs shown are not standard products but were specially processed by CVD techniques and/or heat treatments to generate high densities of defects for the purpose of testing and demonstration of the analytical techniques.

#### TABLE OF CONTENTS

| Secti | on   |                                                         | Page |

|-------|------|---------------------------------------------------------|------|

| 1.    | SUMM | MARY                                                    | 2    |

| 2.    | INTR | RODUCTION                                               | 5    |

|       | 2.1  | Background and Definitions                              | 5    |

|       | 2.2  | Objective, Scope, and Approach                          | 5    |

|       | 2.3  | Organization of Report and Related References           | 6    |

| 3.    | DEFF | ECTS IN GLASS PASSIVATION LAYERS AND METHODS FOR DEFECT |      |

| ٦.    | TEST |                                                         | 7    |

|       |      |                                                         | /    |

|       | 3.1  | Types and Causes of Defects and Their Effects on IC     |      |

|       |      | Reliability                                             | 7    |

|       | 3.2  | Conventional Methods for Defect Testing                 | 8    |

|       | 3.3  |                                                         | 9    |

|       | 3.4  | Methods Investigated and Developed During This          |      |

|       |      | Research Contract                                       | 9    |

| 4.    | EXPE | RIMENTAL STUDIES AND METHOD DEVELOPMENT                 | 11   |

|       | 4.1  | Metal Demarcation Etching                               | 11   |

|       |      | 4.1.1 Principle                                         | 11   |

|       |      | 4.1.2 Materials and Equipment                           | 11   |

|       |      | 4.1.3 General Test Procedure for Demarcation Etching .  | 13   |

|       |      | 4.1.4 Examination of Glass Defects by Optical and       | 13   |

|       |      | Scanning Electron Microscopy                            | 13   |

|       |      | 4.1.5 Parameters of Selective Aluminum Etching          | 19   |

|       |      | 4.1.6 Selective Demarcation Etching of Other            | 19   |

|       | , ,  | Metal/Insulator Structures                              | 31   |

|       | 4.2  | Metal Insulator Sequential Etching                      | 31   |

|       |      | 4.2.1 Principle                                         | 31   |

|       |      | 4.2.2 Test Samples and Materials                        | 33   |

|       |      | 4.2.3 Test Procedure                                    | 33   |

|       |      | 4.2.4 Examples                                          | 35   |

|       | 4.3  |                                                         | 38   |

|       |      | 4.3.1 General Principles                                | 38   |

|       |      | 4.3.2 Equipment and Materials                           | 40   |

|       |      | 4.3.3 Test Procedure                                    | 43   |

|       |      | 4.3.4 Selection of Best Materials                       | 43   |

|       |      | 4.3.5 Investigation of Deposition Mechanism             | 44   |

|       |      | 4.3.6 Summary                                           | 51   |

|       | 4.4  | Decoration by Electrostatic Charging                    | 51   |

|       |      | 4.4.1 Corona-Charging Process                           | 51   |

|       |      | 4.4.2 Direct Decoration of Defects by Corona            |      |

|       |      | Charging                                                | 58   |

|       |      | 4.4.3 Reverse Decoration of Defects by Corona           |      |

|       |      | Charging                                                | 63   |

|       |      | 4.4.4 Sample Cleaning After Decoration                  | 74   |

# TABLE OF CONTENTS (Continued)

| Secti | on    |                                                                                                   | Page |

|-------|-------|---------------------------------------------------------------------------------------------------|------|

|       |       | 4.4.5 Nondestructiveness of Methods                                                               | 76   |

|       | 4.5   | Techniques for Quantifying Defect Density                                                         |      |

|       |       | 4.5.1 Manual Microscopic Analysis                                                                 |      |

|       | 4.6   | 4.5.2 Feasibility Study of Automated Read-out Advantages of the Reverse Decoration - Carbon Black | 77   |

|       | 4.0   | Method                                                                                            | 78   |

|       |       | 4.6.1 Speed                                                                                       | 78   |

|       |       | 4.6.2 Simplicity                                                                                  |      |

|       |       | 4.6.3 Permanence of Decoration                                                                    | 80   |

|       |       | 4.6.4 Nondestructive Nature                                                                       | 80   |

|       |       | 4.6.5 Avoidance of Junction Effects                                                               | 80   |

|       |       | 4.6.6 High Contrast                                                                               | 80   |

|       |       | 4.6.7 Ease of Observation                                                                         | 81   |

|       |       | 4.6.8 Limitation                                                                                  |      |

| _     |       |                                                                                                   |      |

| 5.    | ADVAI | NTAGES AND DISADVANTAGES OF THE METHODS INVESTIGATED                                              | 82   |

| 6.    | ADDI  | TIONAL EXAMPLES OF APPLICATIONS                                                                   | 84   |

|       | 6.1   | Metal Demarcation Etching                                                                         | 84   |

|       | 6.2   | Metal/Insulator Sequential Etching                                                                |      |

|       | 6.3   | Electrophoretic Decoration                                                                        |      |

|       | 6.4   | Direct Decoration by Corona Charging                                                              |      |

|       | 6.5   | Reverse Decoration by Corona Charging                                                             |      |

| 7.    | STANI | DARD PROCEDURES                                                                                   | 94   |

|       |       |                                                                                                   | 24   |

|       | 7.1   | Metal Demarcation Etching for Glassed Aluminum-Metal-                                             |      |

|       |       | lized ICs                                                                                         | - '  |

|       |       | 7.1.1 Determination of the Aluminum Etching Time                                                  | 74   |

|       |       | 7.1.2 Demarcation Etching Time                                                                    | 2-1  |

|       |       | 7.1.3 Examination of Etched Sample                                                                | - 1  |

|       | 7.0   | 7.1.4 Determination of Defect Density                                                             |      |

|       | 7.2   | Sequential Metal/Insulator Etching                                                                | 94   |

|       |       | 7.2.1 Determination of the Aluminum Etching and                                                   |      |

|       |       | Demarcation Etching Time                                                                          |      |

|       |       | Time                                                                                              | 94   |

|       |       | 7.2.3 Determination of Film Thicknesses                                                           | 95   |

|       |       | 7.2.4 Sequential Etching Procedure                                                                | 95   |

|       | 7.3   | Electrophoretic and Corona Decoration Methods                                                     | 95   |

|       |       | 7.3.1 Phosphor and Glass Suspensions                                                              | 95   |

|       |       | 7.3.2 Carbon Black Suspension                                                                     | 96   |

|       |       | 7.3.3 Equipment                                                                                   | 96   |

|       |       | 7.3.4 Sample Preparation                                                                          | 96   |

|       |       | 7.3.5 Electrophoretic Process                                                                     | 96   |

|       |       | 7.3.6 Corona Decoration Process                                                                   | 96   |

|       |       | 7.3.7 Cleaning Procedure                                                                          | 97   |

# TABLE OF CONTENTS (Continued)

| Section | on    |                                                                                                   | Page |

|---------|-------|---------------------------------------------------------------------------------------------------|------|

| 8.      | CONCI | LUSIONS                                                                                           | 98   |

| 9.      | RECON | MMENDATIONS FOR FUTURE WORK                                                                       | 101  |

|         | 9.1   | Extending the Applicability of the New Measuring Methods                                          | 101  |

|         | 9.2   | Mechanism of Reverse Decoration                                                                   | 101  |

|         | 9.3   | Critical Examination of Commercial ICs                                                            | 102  |

|         | 9.4   | Applicability to Inorganic and Organic Dielectric Film Evaluation in Various Technological Fields | 102  |

| REFERE  | ENCES |                                                                                                   | 103  |

#### LIST OF ILLUSTRATIONS

| Figure | e                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

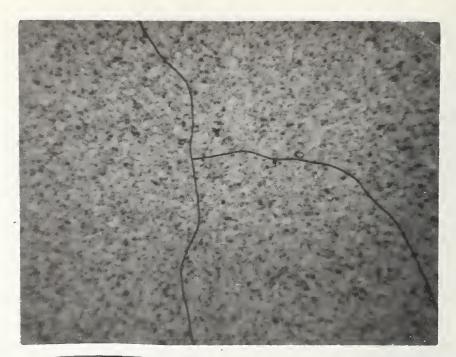

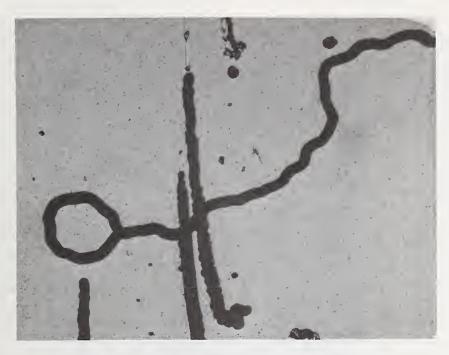

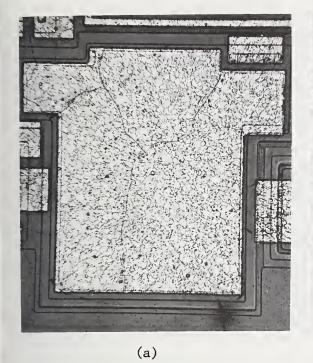

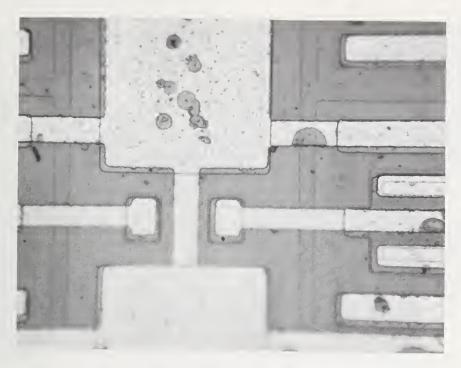

| 1.     | Optical photomicrograph of untreated cracks in a 1.4-µm-thick CVD PSG layer over a continuous 1.8-µm-thick layer of aluminum on oxidized silicon. Pinholes (if present) would be invisible because of metal grain structure (385X, brightfield)                                                                                                                                                                                          | 14   |

| 2.     | Etching-demarcated microcracks in sample shown in figure 1. Dark bands are substrate from which aluminum was removed from underneath glass layer in 10 min selective metal etching at 50°C. Glass crack is dark line in center of 15-18-µm-wide bands. No pinholes are present in this sample area (385X, Nomarski differential interference contrast)                                                                                   | 14   |

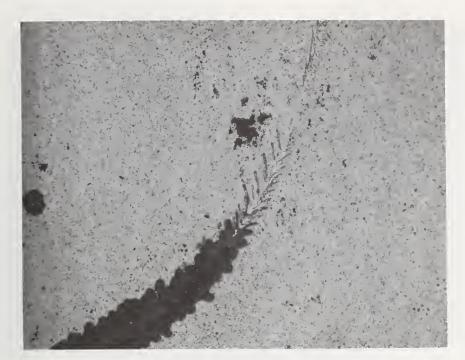

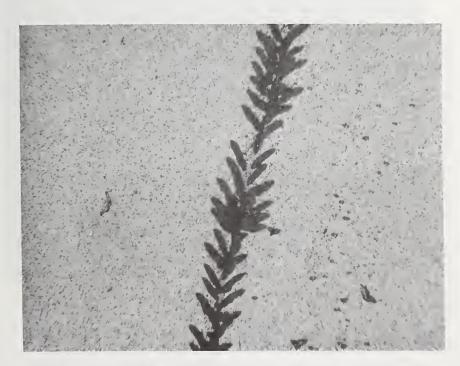

| 3.     | Scratch-induced heavy damage in glass layer made visible by 20-min aluminum etching. Scribe direction was apparently downward with increasing pressure. Sample structure as noted in figure 1 (385X, brightfield)                                                                                                                                                                                                                        | 15   |

| 4.     | Scratch-induced microcracks in glass layer similar to figure 3. Most damage occurs in V-shaped part of pattern. Maximum spread of demarcation is 80 $\mu$ m (385X, brightfield) .                                                                                                                                                                                                                                                        | 15   |

| 5.     | Optical photomicrograph of microcrack structure in 1.4- $\mu$ m-thick PSG layer on a 1.8- $\mu$ m-thick aluminum layer on oxidized silicon. (a)-incompletely demarcated by selective etching for 20 min. (b)-completely demarcated by additional 10 min of aluminum etching (500X, brightfield)                                                                                                                                          | 16   |

| 6.     | Stress- and scratch-induced cracks and several pinholes in $0.7-\mu m$ -thick PSG layer on $1.8-\mu m$ -thick aluminum layer on oxidized silicon. Demarcation-etched for 20 min. Width of circular band is 25 $\mu m$ (200X, brightfield)                                                                                                                                                                                                | 17   |

| 7.     | Circular, self-terminating crack pattern in glass layer as in figure 6 except that PSG is 1.4 $\mu m$ thick (200X)                                                                                                                                                                                                                                                                                                                       | 17   |

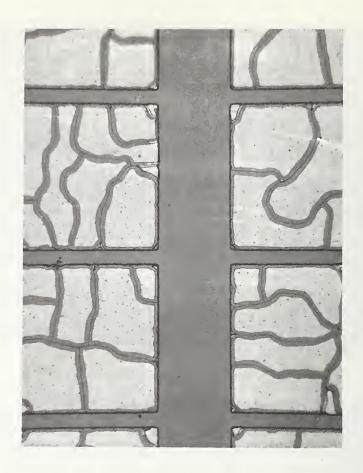

| 8.     | Optical photomicrograph of stress cracks of a CVD silicon dioxide film of 1- $\mu$ m thickness deposited over oxidized silicon with squares of 105 x 105 $\mu$ m of evaporated aluminum. Demarcation was achieved by 10-min aluminum etching. Cracks surround most of pattern along edge of aluminum. Differences in the width of the inside area are most probably caused by differences in the width of the cracks (150X, brightfield) | 18   |

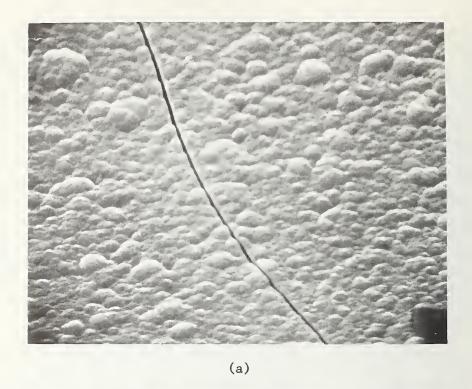

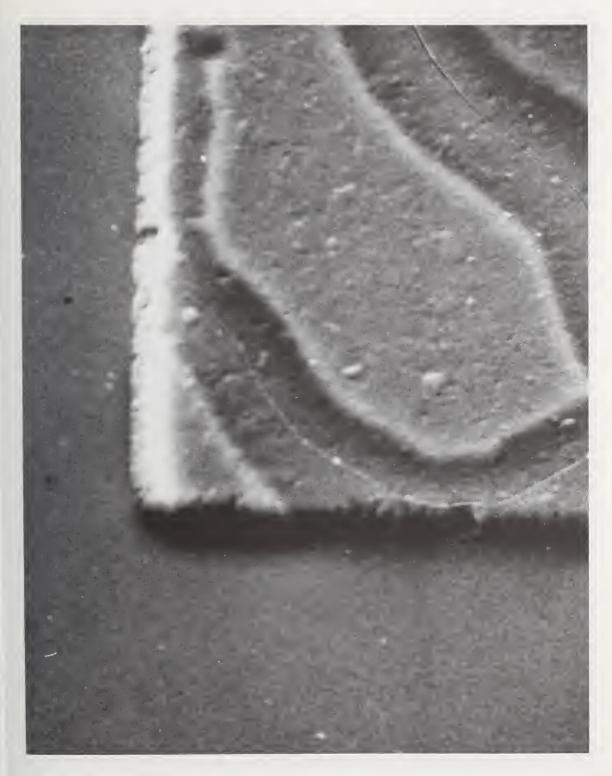

| 9.     | Scanning electron micrographs at 5000X of untreated microcrack in 1.4- $\mu$ m-thick PSG over 1.8- $\mu$ m-thick evaporated aluminum on oxidized silicon substrate wafer. Width of crack is about 0.4 $\mu$ m. (a)-45° view and (b)-25° view from perpendicular                                                                                                                                                                          | 20   |

| Figur | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

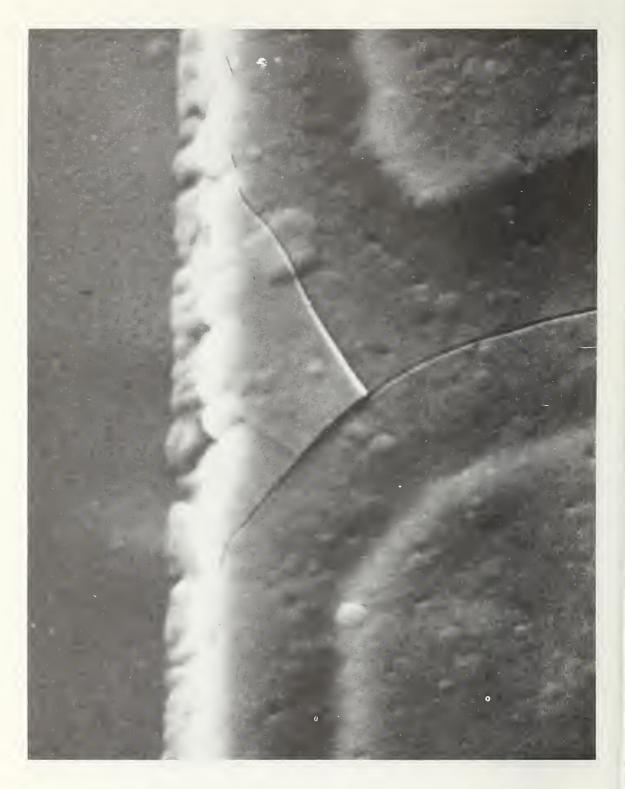

| 10.   | Scanning electron micrograph (2400X, 30°) of demarcation-<br>etched stress cracks. Sample as defined in figures 8 and<br>9. No cracks exist in overcoated oxide layer between<br>aluminum patterns                                                                                                                                                                                                                                                                                                                   | 21   |

| 11.   | Scanning electron micrograph (4800X, 30°) showing a different area of sample from figure 10. Gray channel areas are caused by differences in charging due to etched-out aluminum under glass                                                                                                                                                                                                                                                                                                                         | 22   |

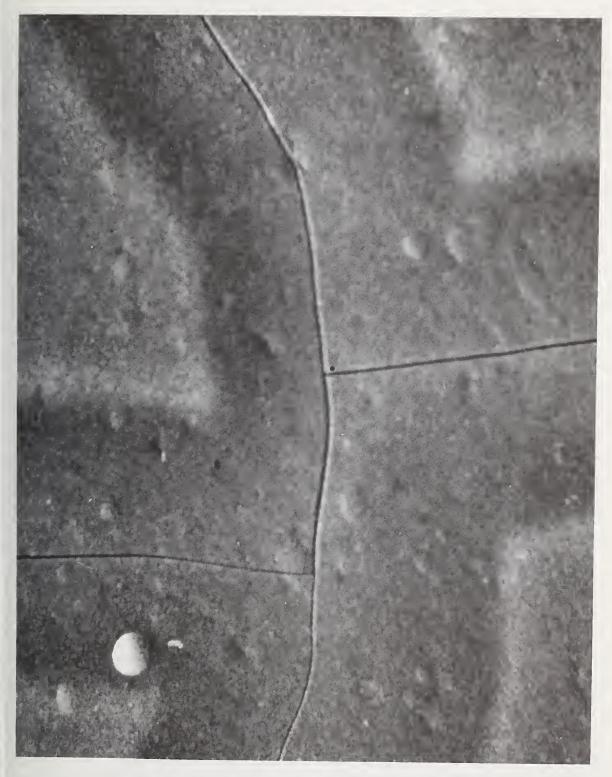

| 12.   | Glass microcracks in sample shown in figures 8, 10 and 11 as observed by SEM at 4800X and 30° from the perpendicular. Width of crack from this high-magnification photograph is approximately 0.2 $\mu m$                                                                                                                                                                                                                                                                                                            | 23   |

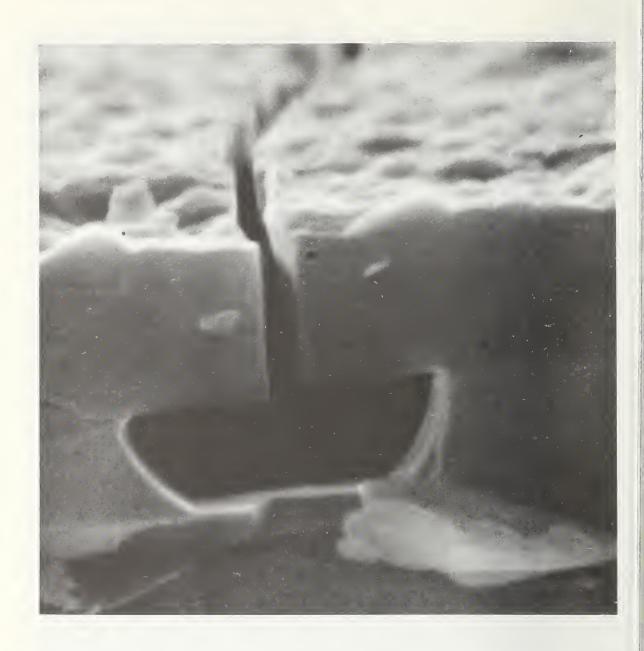

| 13.   | Cross section SEM of a demarcation-etched structure. Sample consisted of a stress-cracked CVD PSG passivation layer over aluminum on oxidized silicon. Cavity formed in aluminum by selective etching underneath glass exhibits curved side walls caused by normal isotropic etching                                                                                                                                                                                                                                 | 24   |

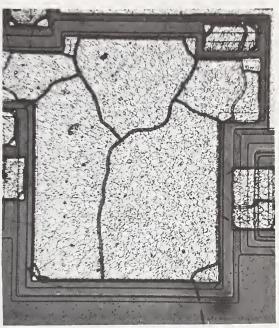

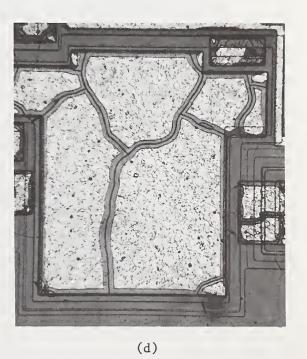

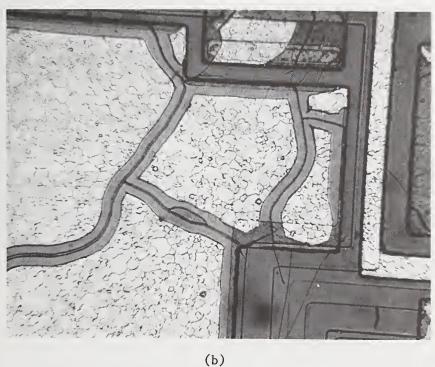

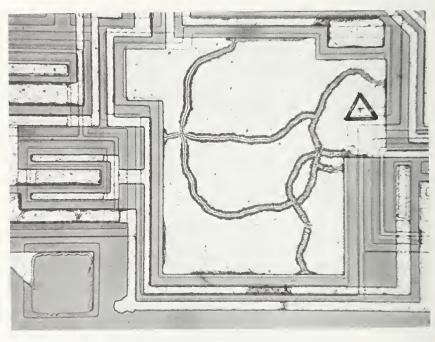

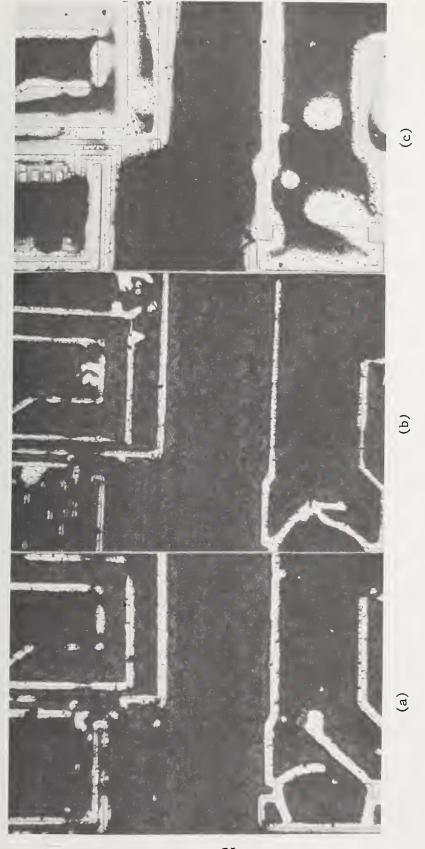

| 14.   | Optical photomicrographs of microcrack in a continuous 1.2-µm-thick silicon dioxide film over aluminum-metallized linear bipolar IC wafer. Large light area is a metallized capacitor of 430 µm length (150X, brightfield).  (a) - Untreated sample; fine microcracks are just barely visible.  (b) - Demarcation-etched in aluminum etch at 50°C by an etch time factor of 1.25; crack pattern over aluminum areas is now readily visible. Previously nondetectable defects in smaller metal areas can now be seen. |      |

|       | (c) - Additionally etched sample corresponding to an etch time factor of 2.5; cracks along the periphery of the metal areas have now become visible.                                                                                                                                                                                                                                                                                                                                                                 |      |

|       | (d) - Etch time factor of 5.0; peripheral crack demarcations are seen to be 1/2 the width of the inside area bands, indicating that they occur exactly along edge of pattern. Portions of one interconnect line are seen to be the only undamaged parts in this sample area. Differences in the width of the inside demarcation bands in various areas seem to indicate differences in width of the crack, affecting the rate of demar-                                                                              |      |

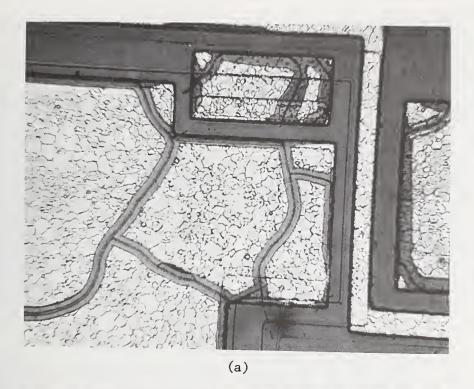

| 15.   | Detailed optical photomicrographs of demarcation-etched glass cracks. (a)-same as figure 14(c) but at 2.6X higher                                                                                                                                                                                                                                                                                                                                                                                                    | 26   |

|       | magnification. (b)-same as figure 14(d) but at 2.6X higher magnification                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29   |

| Figure | е                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

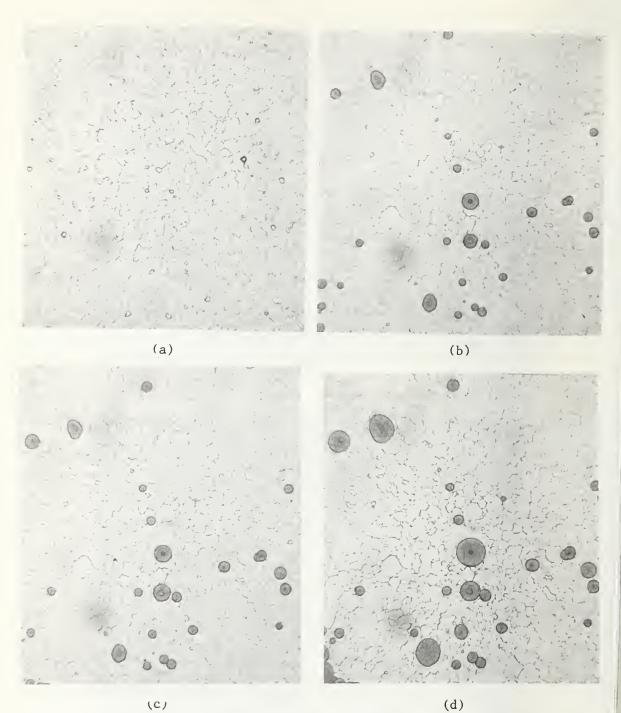

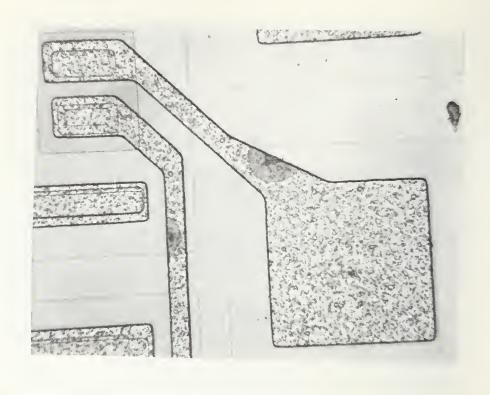

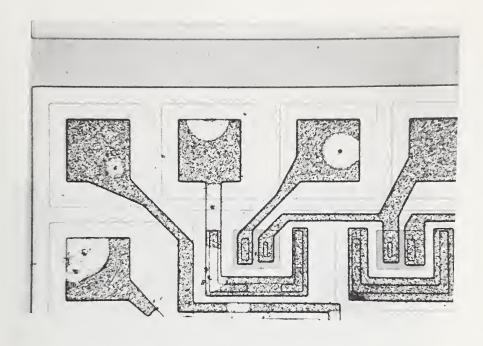

| 16.    | Optical photomicrograph of pinholes in a PSG layer over aluminum as a function of increasing etch time factor: (a)-0; (b)-1.25; (c)-2.5, and (d)-5.0. It is seen that no new pinholes become demarcated beyond a factor of 1.25. Small size demarcations (indicating small pinholes) increase much more slowly in size on continued etching than longer ones, indicating that the rate of demarcation growth depends on the defect size, as noted for microcracks (385X, brightfield) | • 30         |

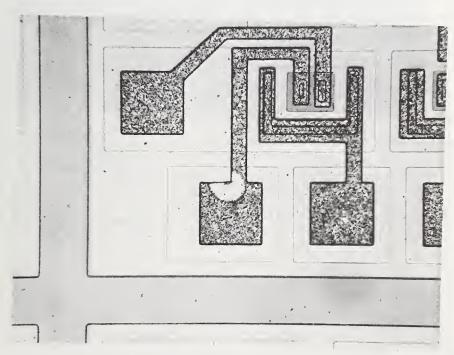

| 17.    | Developed partial pinholes in PSG passivation layer over aluminum interconnect pattern of an IC. These latent pinholes exposed the aluminum after 50% of the glass coating was removed by selective etching (385X, brightfield).                                                                                                                                                                                                                                                      | • 36         |

| 18.    | Developed thin edge coverage of PSG over edges of aluminum interconnect of an IC. The aluminum line edges became exposed in many places after 50% of the glass coating was removed by selective etching (385X, brightfield)                                                                                                                                                                                                                                                           | • 37         |

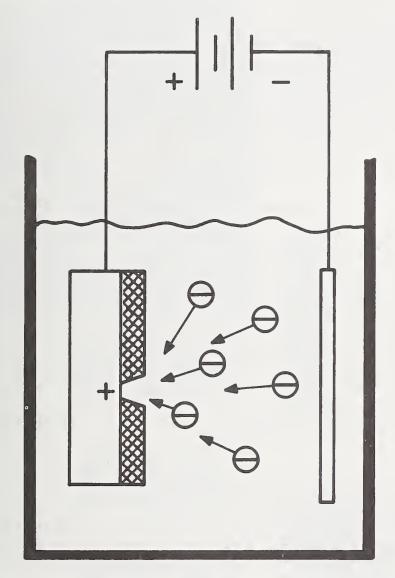

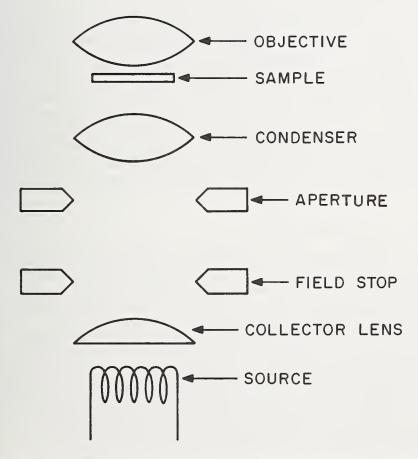

| 19.    | Schematic of electrophoretic decoration apparatus                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 39         |

| 20.    | Photoresist mask showing negative/positive precision pattern used in defect decoration resolution measurements. Thinnest line is 1 $\mu$ m (121X)                                                                                                                                                                                                                                                                                                                                     | • 41         |

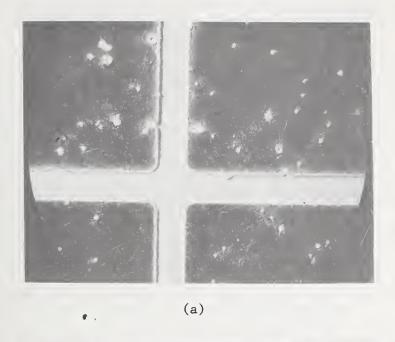

| 21.    | Micrograph of glass particles deposited on mesa-type wafer. The thermal oxide is 1.2 $\mu$ m thick, and the groove width is 0.4 mm. (a) Deposition at 50 V for 8 min. (b) Deposition at 200 V for 2 min (20X)                                                                                                                                                                                                                                                                         | • 45         |

| 22.    | Zinc oxide powder deposited by electrophoresis on thermal silicon dioxide showing pinhole decoration and background deposition. The deposition was done at 10 V for 30 s. The deposits decorating the pinholes are about 10 $\mu$ m in diameter (400X)                                                                                                                                                                                                                                | 1.6          |

| 23.    | Micrograph of zinc silicate phosphor deposited on defect on IC wafer. Deposition was done at 25 V for 10 min. (100X, brightfield)                                                                                                                                                                                                                                                                                                                                                     | • 46<br>• 46 |

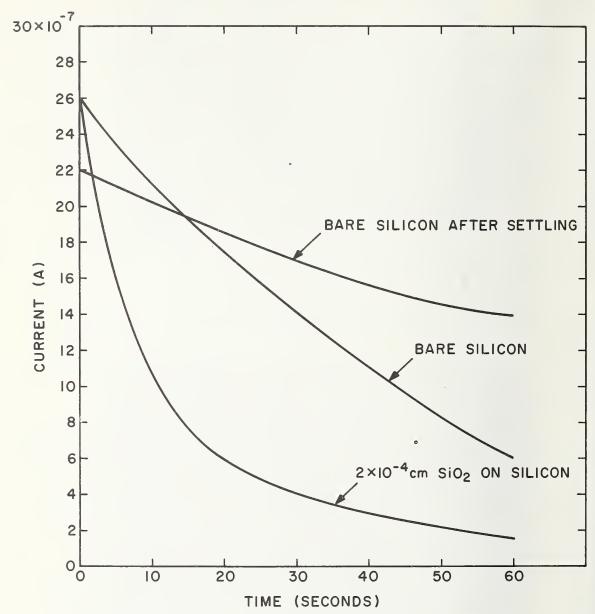

| 24.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

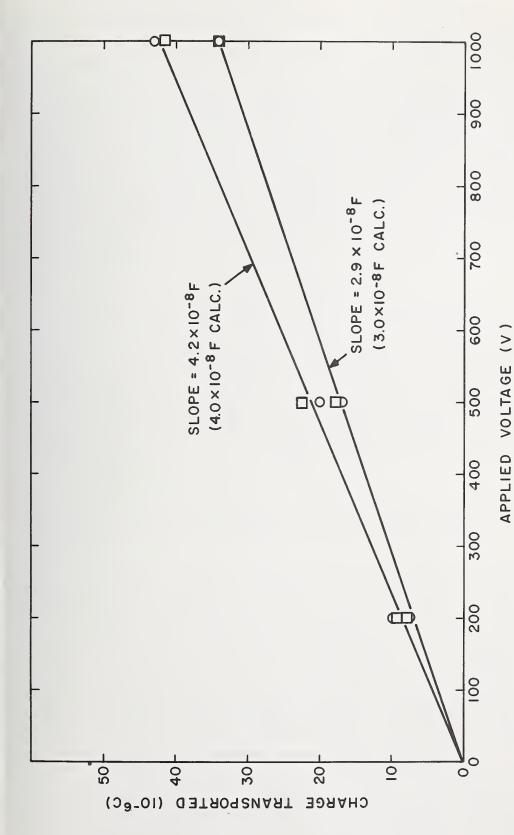

| 25.    | Plot of charge transported vs applied voltage for silicon dioxide-coated wafer. The suspension is the same as for figure 24. Sulfonate content was 0.1% to C2Cl3F3 by volume for the Operate and 0.2% for the Tarinta                                                                                                                                                                                                                                                                 |              |

|        | for the $\odot$ points and 0.2% for the $\odot$ points                                                                                                                                                                                                                                                                                                                                                                                                                                | 49           |

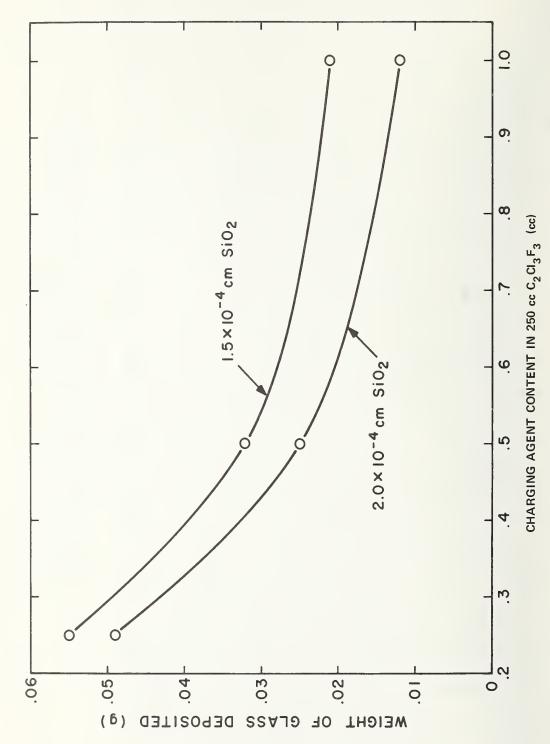

| Figur | ce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 26.   | Plot of glass deposited on silicon dioxide-coated wafers as function of concentration of petroleum barium sulfonate                                                                                                                                                                                                                                                                                                                                                                                                 | 50       |

| 27.   | Schematic of corona charging process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52       |

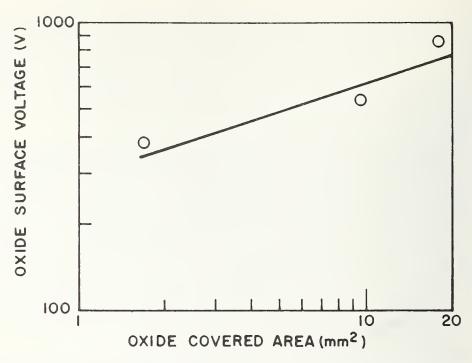

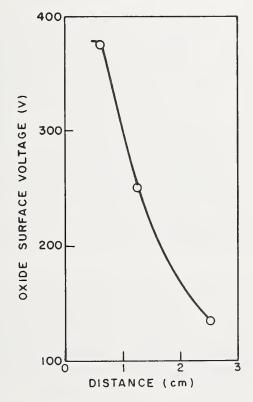

| 28.   | Oxide surface voltage charged to saturation vs area of oxide-covered surface. Oxide thickness is 10,000 Å                                                                                                                                                                                                                                                                                                                                                                                                           | 54       |

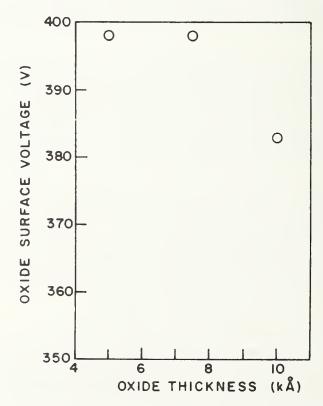

| 29.   | Oxide surface voltage charged to saturation vs oxide thickness for oxide-covered area of 1.7 $\mathrm{mm}^2$                                                                                                                                                                                                                                                                                                                                                                                                        | 54       |

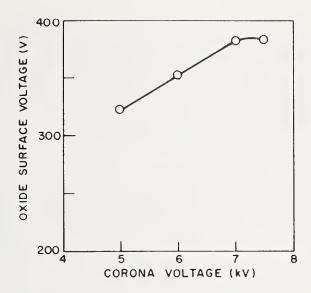

| 30.   | Oxide surface voltage charged to saturation vs voltage of corona wires for oxide 10,000 Å thick and area of 1.7 $\mbox{mm}^2$                                                                                                                                                                                                                                                                                                                                                                                       | 55       |

| 31.   | Oxide surface voltage charged to saturation vs distance from wafer to corona wires at 10 kV for oxide 10,000 Å thick                                                                                                                                                                                                                                                                                                                                                                                                |          |

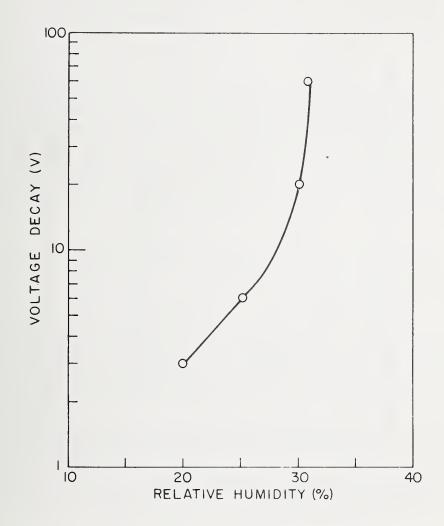

| 32.   | oxide surface voltage decay in first minute after charging vs relative humidity                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55<br>57 |

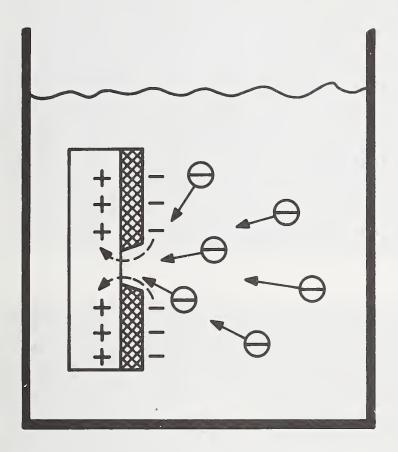

| 33.   | Direct decoration of defects after corona charging of insulator regions with ions of same sign as decorating particles in suspension                                                                                                                                                                                                                                                                                                                                                                                | 59       |

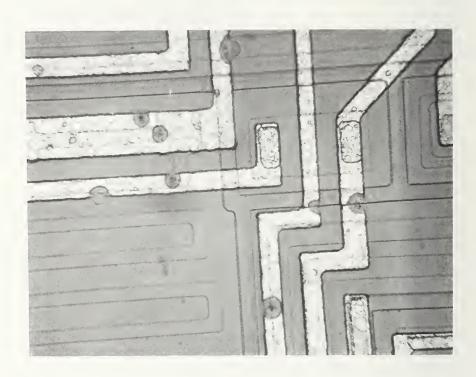

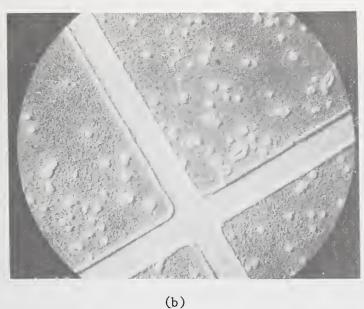

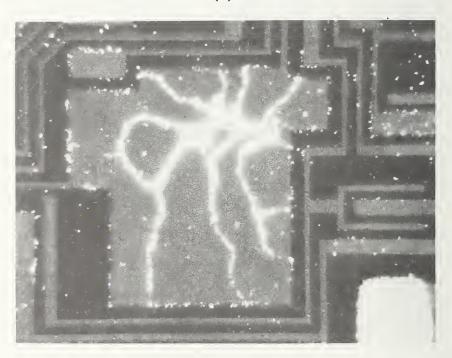

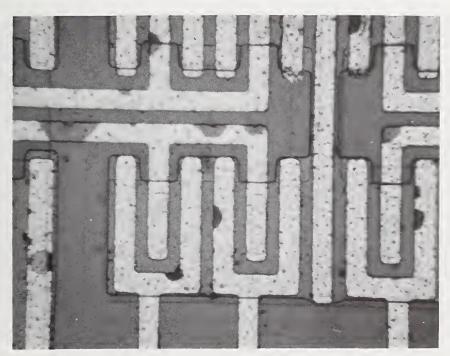

| 34.   | (a) and (b)-Phosphor deposition at 10,000 V charging voltage showing excellent crack detection. Not all isolated phosphor deposits correspond to pinholes at this high voltage. (150X, uv and brightfield). (c)-Phosphor deposition at relatively low charging voltage (6000 V). Note that cracks and large defects are detected by the phosphor (150X, uv, and brightfield illumination). (d)-Sample from (c) after phosphor stripping followed by selective aluminum etching (15 min 50°C), (150X, brightfield) 6 | 061      |

| 35.   | (a)-Phosphor decoration at a charging potential of 6000 V prior to aluminum etching (150X, uv and brightfield illumination). (b)-Sample from (a) after phosphor stripping followed by aluminum etching (5 min 80°C). The triangle encloses a defect detected by etching which had not been decorated by the phosphor                                                                                                                                                                                                | 62       |

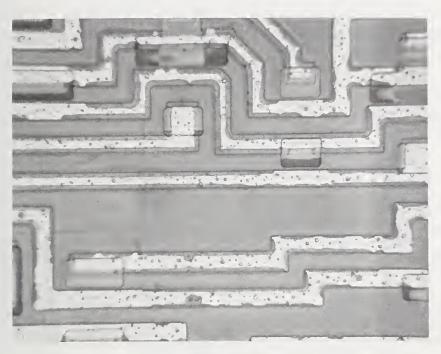

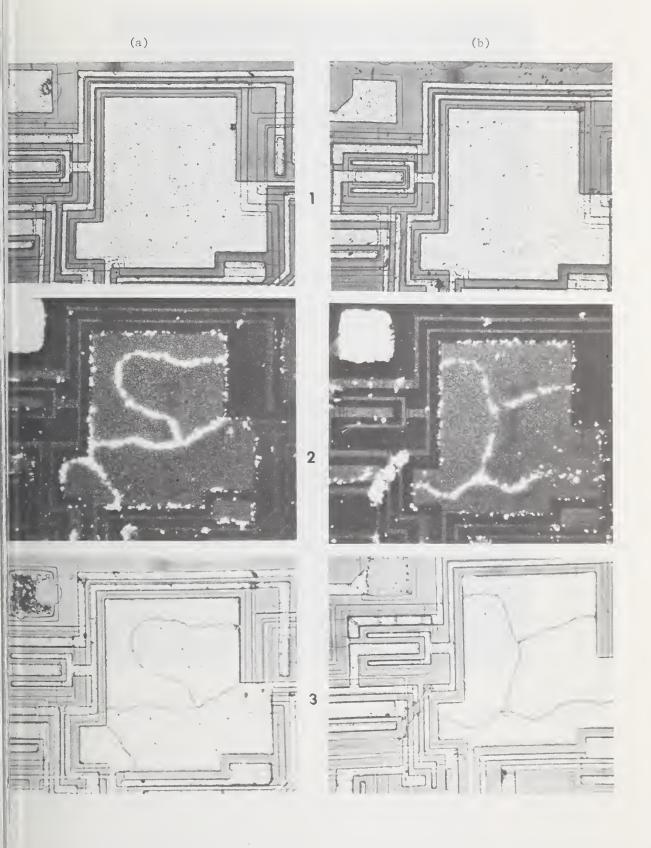

| 36.   | Corresponding photomicrographs of a glass-overcoated linear bipolar IC with stress-induced microcracks depicting two aluminum-metallized capacitor areas (a) and (b): (1) Samples before treatments, as seen under brightfield illumination (~100X). (2) Same samples electrophoretically decorated with ZnSiO <sub>4</sub> :Mn phosphor B, as seen in uv and brightfield illumination (~100X). (3) Same sample after stripping phosphor followed by 5-min aluminum etching at 50°C (~100X)                         | 64       |

| Figure | 2                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 37.    | (a)-Electrophoretic phosphor decoration of negative/positive precision test pattern etched into 5000 Å of thermally grown $SiO_2$ on silicon. Thinnest line width is 1 µm (78.5%, uv illumination). (b)-Same pattern as (a), showing feasibility of decorating "partial" pinholes or thin spots. In this case, 1000 Å of CVD $SiO_2$ was deposited over the same etched pattern used |      |

|        | for (a) to simulate 1000-A-thick-thin spots over silicon. The pattern (except the narrowest line) has become decorated, but with a lower quantity of phosphor                                                                                                                                                                                                                        | 66   |

| 38.    | ZnSiO <sub>4</sub> :Mm phosphor deposited along cracks in 15,000- $\overset{\circ}{A}$ CVD SiO <sub>2</sub> layer over IC wafer exposed to humid ambient (RH = 62%) for 2 s between charging and deposition (150X, bright-field with uv irradiation)                                                                                                                                 | 67   |

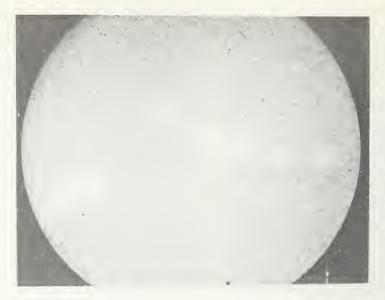

| 39.    | Reverse decoration of defects after corona charging of insulator regions with ions of opposite sign to that of decorating particles in suspension                                                                                                                                                                                                                                    | 68   |

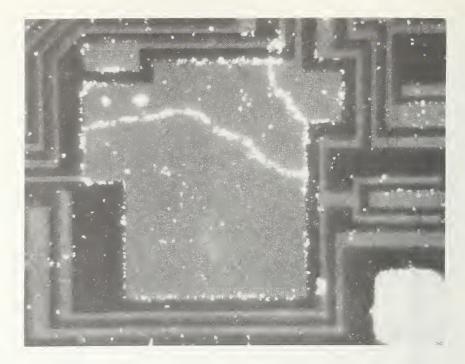

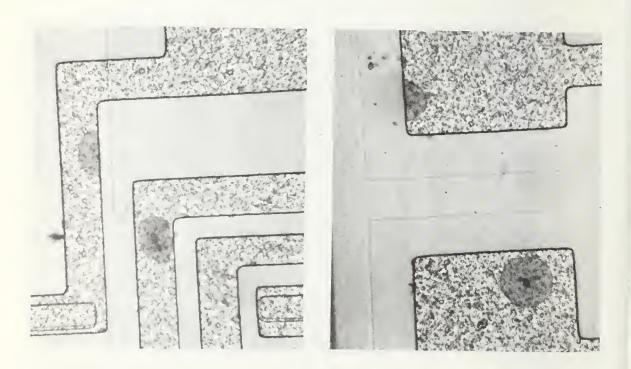

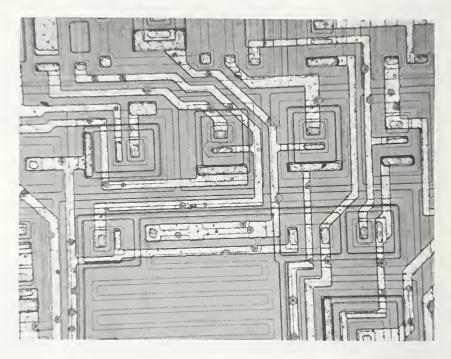

| 40.    | Carbon black deposited on device to reverse-decorate the defects. High contrast renders microscopic evaluation fast and sensitive. Width of narrowest aluminum lines (visible at right) is about 12 $\mu$ m (150X)                                                                                                                                                                   | 71   |

| 41.    | Confirmation of defect detection by the reverse-decoration method. Sample was aluminum-etched at 50°C for 5 min without removing carbon black. (a) 385X, (b) 760X                                                                                                                                                                                                                    | 72   |

| 42.    | Carbon black deposition with high threshold voltage in (a) compared to one with low threshold voltage in (b); (150X, brightfield)                                                                                                                                                                                                                                                    | 73   |

| 43.    | Carbon black reverse-decoration as function of time delay between charging and deposition. The time delays are (a) 4 s, (b) 10 s, (c) 120 s. Corona potential was +7000 V dc (78.5X, brightfield)                                                                                                                                                                                    | 75   |

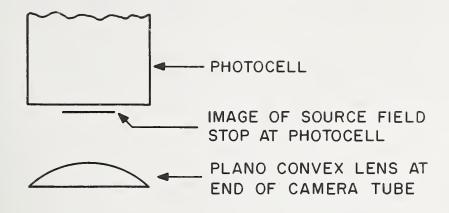

| 44.    | Schematic of microscope use for obtaining image of source field stop at photocell for reflected light measurements                                                                                                                                                                                                                                                                   | 79   |

| 45.    | Selectively demarcation-etched area pinholes in a defective passivation test layer over an aluminum-metallized IC (760X)                                                                                                                                                                                                                                                             | 85   |

| 46.    | Selectively demarcation-etched edge pinholes in a defective passivation test layer over an aluminum-metallized IC. Particulates are surface impurities left from plastic decapsulation processing (385X)                                                                                                                                                                             |      |

|        | capacitation biocessing (2024)                                                                                                                                                                                                                                                                                                                                                       | 85   |

| Figur | e                                                                                                                                                                                                                                                                                | Page    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 47.   | Variety of selectively demarcation-etched area and edge pinholes in a rf plasma-deposited silicon nitride passivation layer over an aluminum-metallized IC (385X)                                                                                                                | 86      |

| 48.   | Variety of selectively demarcation-etched area and edge pinholes in a rf plasma-deposited silicon nitride passivation layer over a gold-metallized IC (150X)                                                                                                                     | 87      |

| 49.   | Sequentially metal/glass-etched aluminum-metallized and glass-passivated IC showing numerous pinholes that were opened on glass etching (150X)                                                                                                                                   | 88      |

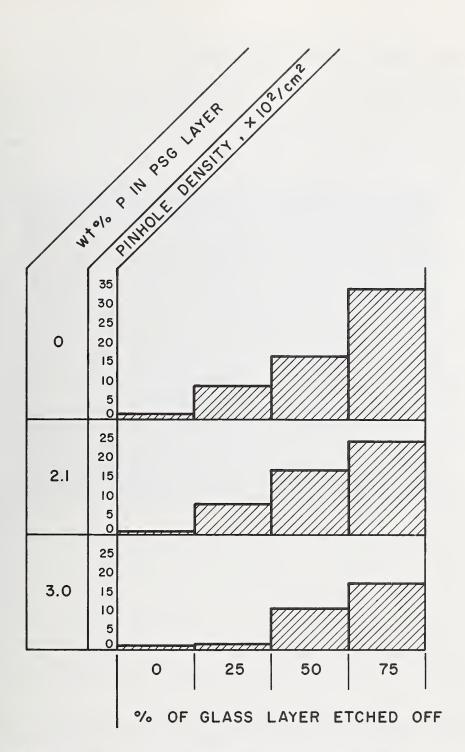

| 50.   | Density of open and partial pinholes as a function of glass composition and layer depth. Samples used were experimental aluminum-metallized IC overcoated with 1.15- $\mu$ m CVD SiO2 or PSG. The residual layer thickness are 1.15, 0.86, 0.58, and 0.29 $\mu$ m                | 89      |

| 51.   | Carbon black deposited on CMOS SOS device wafer showing defects in passivation layer (385X, brightfield)                                                                                                                                                                         | 91      |

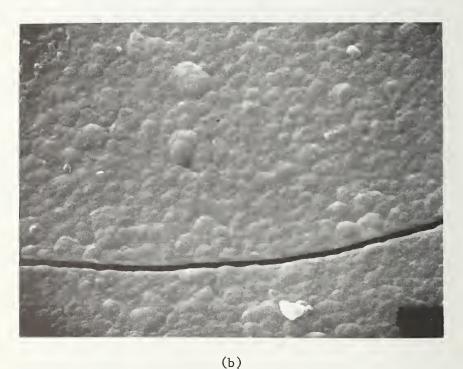

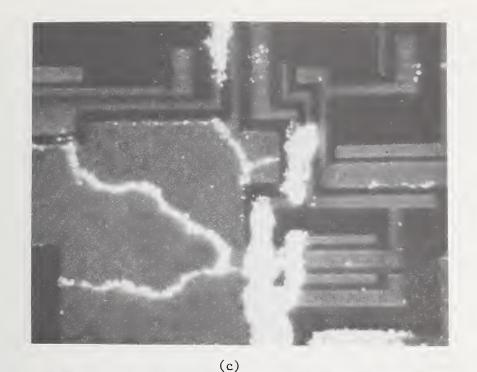

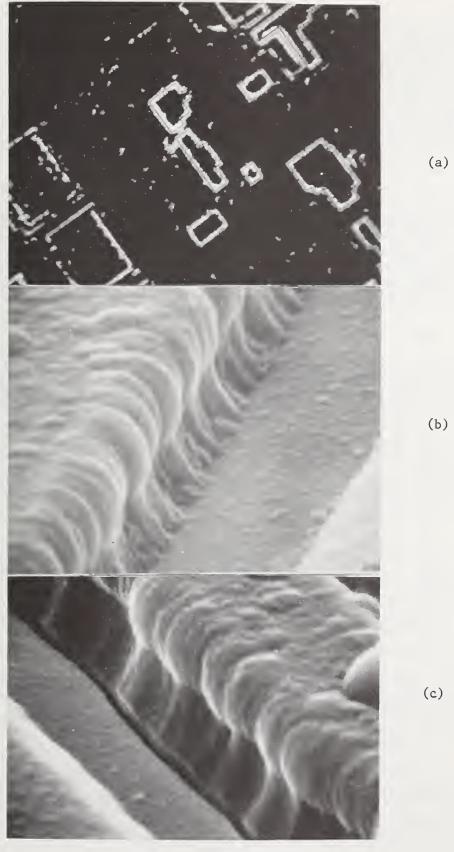

| 52.   | Example of cracking at edges of large aluminum areas due to extreme heat treatment. (a)-Cracks outlined by carbon black (150X, brightfield), (b)-SEM cannot detect cracks (20,000X), (c)-After 10-s buffered hydrofluoric acid etching the SEM does resolve the cracks (20,000X) | ,<br>92 |

#### LIST OF TABLES

| Table |                                                                                                           | Page |

|-------|-----------------------------------------------------------------------------------------------------------|------|

| 1.    | Characterization of Various Aluminum Etchant<br>Compositions at 50°C                                      | 12   |

| 2.    | Effects of Temperature and Time on Aluminum Etching                                                       | 25   |

| 3.    | Selective Demarcation Etching of Commonly Used Metal Films Coated with Oxide, Glass, or Nitride Layers    | 32   |

| 4.    | Demonstration of Sequential Metal-Glass Etching Method                                                    | 34   |

| 5.    | UV-Luminescing Powder Materials (Classified in Order of Preference for Electrophoretic Defect Decoration) | 42   |

| 6.    | Advantages and Disadvantages of Methods Investigated                                                      | 83   |

"Techniques for Measuring the Integrity of Passivation Overcoats on Integrated Circuits"

bу

Werner Kern and Robert B. Comizzoli

Conventional test methods to evaluate the quality of glass passivation overcoats on semiconductor devices are generally inadequate and/or destructive. Three new methods have been devised that overcome these problems: (1) Sequential selective chemical etching of metal/dielectric structures to detect buried, latent, or partial defects as a function of dielectric layer depth. (2) Electrophoretic cell decoration with uv phosphor particles suspended in an insulating liquid, the sample forming one electrode of the cell. (3) Electrostatic corona charging to selectively deposit surface ions from a high voltage dc discharge on the insulating surfaces of the sample, followed by placing of the charged sample in a suspension of charged carbon black particles in an insulating liquid; depending on the polarity of the ions the particles can be deposited on the insulator surface or at the defect sites. The etching method is most suitable in process research studies, and the electrophoretic technique for demarcating relatively large defects. The corona decoration method, coupled with automated instrumental read-out based on measuring the reflected light intensity, is ideal for routine testing of devices because it is fast, simple: sensitive, and nondestructive to devices such as glass passivated bipolar and MOS ICs. The practical benefits of the new test methods can be considerable in production and product control, with cost savings through early detection of production line defects and rapid corrective action.

Key words: Corona charging decoration; dielectric defect detection; electrophoretic decoration; integrated circuit quality control; selective chemical etching; and semiconductor device reliability.

<sup>&</sup>quot;This research funded by the Advanced Research Projects Agency Order 2397 through the National Bureau of Standards' Semiconductor Technology Program Contract (5-35913). The views and conclusions expressed are those of the authors and do not necessarily represent the official policies of the Department of Defense, Department of Commerce, or the United States Government. This publication is not subject to copyright."

#### 1. SUMMARY

Most integrated circuits now on the market are metallized with aluminum and passivated with an overcoat of phosphosilicate glass (PSG) and/or silicon dioxide. The quality of present-day overcoats is highly variable, indicating that more effective quality control measures are needed to improve the product and its reliability. However, test methods available for evaluating the quality of glass passivation overcoats have been inadequate and/or destructive. The objective of this research program has been the development of analytical test methods that do not suffer from these shortcomings. This goal has been accomplished successfully. We have demonstrated the applicability of the new methods to the specific requirements of this contract, as well as to the evaluation of insulating coatings in general.

The experimental approaches chosen to solve these problems were based on the following basic methods: (1) Selective chemical etching, intended primarily as an absolute standard for comparing other test methods; (2) electrophoretic cell decoration with uv phosphor particles; and (3) electrostatic corona charging to deposit surface charge followed by decoration. Techniques for quantifying the defect density were examined in conjunction with these detection and decoration methods. The major results and conclusions for each are summarized below.

The method of selective metal etching underneath the glass overcoat to demarcate localized structural defects in the overcoat has been demonstrated to be simple, fast, effective, and sensitive. It is an absolute method but has the disadvantage of being destructive. It is used primarily when the sample can be sacrificed in the test, or when an absolute standard is desired for comparison with other techniques. Microcracks in typical glass layers over aluminum can be detected down to widths of less than 500~Å.

Sequential etching of metal/insulator structures is useful for detecting buried, latent, or partial defects within the dielectric overcoat. Determination of the defect density after each pair of etching treatments then provides the defect density as a function of dielectric or insulator layer depth. The method is reliable but time-consuming; it is recommended for applications in process research. Numerous examples are presented, illustrating specific and general applications of the two selective etching methods.

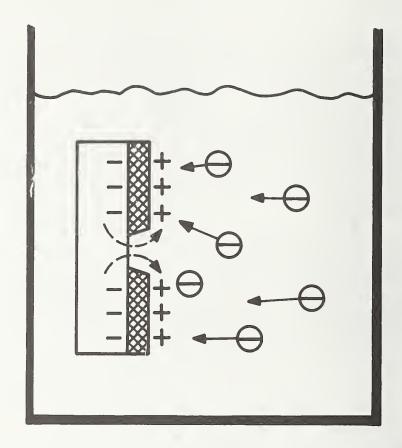

In the electrophoretic method, the sample to be decorated is placed in the suspension, and a voltage is applied between it and an opposite electrode to move the decorating particles to the defects. A rectangular stainless-steel tank is used to hold the decorating suspension. The tank is also used as one electrode. In some cases, a glass beaker is used and a stainless-steel electrode is placed opposite the sample. This method was found suitable for decoration of relatively large defects and cracks with white or uv phosphor powders. The use of insulating liquids was found to give superior results in terms of adhesion and nondestructiveness. The deposition mechanism, basically a

capacitor-charging phenomenon, was investigated in some detail. This technique is useful but less attractive than the corona-charging methods.

In the corona-charging method of decoration, surface ions from a corona discharge are deposited on the insulating surfaces of the sample. At a defect in the insulator, ions flow to the grounded substrate. After the charging step, the sample is placed in a suspension of charged decorating particles in an insulating liquid. If the electrical polarities of the ions on the sample insulating surfaces and of the charged decorating particles are opposite, then the particles are deposited on the insulating surfaces and not at the defects, resulting in reverse defect decoration. If the electrical polarities of ions and particles are the same, then the particles are deposited on the defects, resulting in direct decoration.

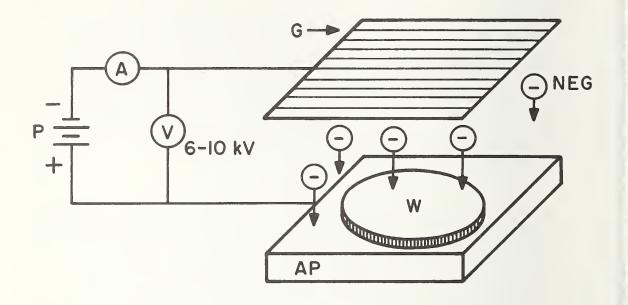

For the corona charging, a plane array of  $40-\mu m$ -diameter wires is used, spaced 2 cm from the sample, which rests on a grounded plate. For certain samples, it is necessary to place a grounded grid over the sample to limit the surface voltage of the passivating layer during the corona charging. The principles of the corona-charging mechanism were studied and related to the process; in particular, the basis for the nondestructive nature of the process is well understood.

In general, the corona-charging techniques are nondestructive, rapid, and simple. Various decorating powders were tested including silicate glasses, uv phosphors, and carbon black. The corona-charging methods are very sensitive; e.g., the carbon black reverse decoration method can detect defects not found by aluminum etching, nor by scanning electron microscopy (SEM), unless glass etching is first used to enlarge the defect. By comparison with etching, this technique has been shown to be very selective. These techniques are also capable of detecting certain partial or latent defects.

The carbon black reverse decoration by corona charging results in a very high contrast sample when viewed by reflectance microscopy. This is a particular advantage for process automation and was explored using a photocell mounted on the microscope to measure reflected light intensity, which was related to sample quality. The population density of decorated defects can thus be quantified. It is possible to automate this type of read-out technique on a step-and-repeat basis, using automatic and computerized instrumental recording of the data.

Post-decoration device recovery procedures have been developed and proven to be effective. It has been shown that device yield is not decreased by this procedure.

A good correlation has been shown to exist among the various methods developed on this contract. Advantages, disadvantages, limitations, sensitivity limits, and applicability of each have been pointed out and demonstrated experimentally in many instances.

The described methods were developed and refined specifically for the evaluation of dielectric overcoats on aluminum-metallized ICs. We have shown, however, that these methods are also applicable to analyzing other metal/dielectric structures and devices and, in fact, to evaluating insulator coatings in general.

The availability of a well-defined practical test method for evaluating the integrity of IC passivating overcoats now offers device manufacturers a much needed tool for controlling their products during Since the recommended techniques are nondestructive, a fabrication. 100 percent quality control is feasible at the device wafer level. will be possible to reprocess defective wafers at this point rather than continue their processing, thus eliminating very large potential losses that would be caused by completing defective materials into finished IC devices. Even more important, these expedient, sensitive, and nondestructive test methods allow rapid information feedback of the test results to the production line and, thus, immediate correction of faulty processing conditions. In addition to being an early, rapid detection system for defects occurring on the production line, the new test methods are a valuable tool for assessing developmental studies for improving materials and processes.

The methods developed and perfected during this program also make it possible to test finished IC devices by the manufacturer (or by the procurement agency or individual customer), and allow a reasonable degree of presently nonexisting standardization of the integrity of overcoat passivation layers on finished IC products. In summary, the practical benefits of the new test methods are very considerable, when applied to production and product control, in terms of both cost savings due to early detection of production line defects and rapid information feedback for corrective action. Batch removal and batch reprocessing of defective material in wafer form will be an additional cost-saving factor.

#### 2. INTRODUCTION

#### 2.1 Background and Definitions

Most types of silicon integrated circuits (ICs) require a passivation overcoat layer to afford scratch resistance of the metallization interconnects during processing; to prevent alkali ions and other impurities from contaminating the device, especially with plasticencapsulated devices; and to provide protection against the effects of loose particles in the case of hermetically sealed packages. sputtered or, more commonly, chemical vapor-deposited (CVD) films of silicon dioxide or phosphosilicate glass (PSG) are generally used as the passivation layer. Both bipolar- and MOS-type ICs used in recent years have been fabricated using passivation layers which, in some cases, have cracks, pinholes, or inadequate coverage of the edges of delineated lines of aluminum conductors (the metallization material most frequently used in ICs), or thin-film resistors. These defects can result in device failure as a result of corrosion of aluminum metal conductors or of oxidation of thin-film resistors. Defects of this type can clearly give rise to serious reliability problems of ICs, and must therefore be controlled and minimized.

Although specifications for high-reliability ICs generally require passivation coatings, they do not provide methods for evaluation of the integrity of these coatings or for rejection of unsuitable coatings that have the specified thickness. Known methods for defect detection and measurement have many drawbacks, which will be discussed. The purpose of this research contract was to devise and to refine suitable analytical control methods for this purpose that do not suffer from such drawbacks. This has been successfully achieved, as demonstrated in this report.

#### 2.2 Objective, Scope, and Approach

One objective of this program was to innovate and develop techniques for evaluating the integrity of passivation overcoats on metallized ICs, and, specifically, for devising practical techniques to detect localized structural defects and to measure their population density.

The techniques to be developed should be suitable for routine quality control by manufacturers, be applicable both to IC devices in wafer form and to individual pellets, and allow estimation or quantization of the number of localized structural defects (such as pinholes and microcracks) per unit area in the oxide or glass overcoat. Preferably, the method should be essentially nondestructive; that is, not damage areas that are defect-free.

Our experimental approach consisted of three main types of promising methods to be explored, developed, and assessed to allow comparison: (1) selective chemical etching of metal to make defects readily visible; (2) electrophoretic defect decoration; and

(3) electrostatic corona-charge decoration of defects. The method selected was expected to be one of these methods (or a combination) to offer the maximum amount of reliable information that can be gained with the simplest, most direct technique. A further task was to explore techniques for quantitative automated measurements of the defect density per unit area on samples where the defects had been made visible by the three methods outlined above.

#### 2.3 Organization of Report and Related References

The main sections consist of: (1) brief review of dielectric defects and methods for their detection; (2) presentation of experimental results of the new analytical methods developed and optimized; (3) critical comparison of the performance of the new methods; (4) examples of applications; and (5) recommended methods, techniques, and test procedures.

For the purpose of brevity, and to avoid duplication, extensive use is made of references to the following related basic papers we have recently published: Survey of methods for detecting and characterizing localized defects in dielectric films [1]\*, and their relation to device reliability [2]; origin of such defects [3] and their relation to electrical film properties [4]; analysis of glass passivation overcoats by selective etching techniques [5]; improved techniques for depositing and testing CVD passivation layers [6]; and, finally, survey of electrostatic and electrophoretic principles and processes [7].

In some cases, for the sake of completeness or to provide desirable background information, this report contains results generated during RCA-supported research studies.

<sup>\*</sup>Bracketed numbers pertain to citations shown on pages 103 to 105.

#### 3. DEFECTS IN GLASS PASSIVATION LAYERS AND METHODS FOR DEFECT TESTING

#### 3.1 Types and Causes of Defects and Their Effects on IC Reliability

Defects in the glass passivation overcoat of ICs can give rise to several types of failure mechanisms that may seriously impair the reliability of the device. Such defects can be classified into the following major groups: (1) localized structural and compositional defects; (2) nonlocalized chemical and physical defects; (3) defects due to chemical interactions of dielectric with metallization and moisture; (4) defects due to ionic and electronic charge motion and conductivity in glass and oxide films, on their surfaces, and along their various interfaces; and (5) assorted defects introduced during passivation processing. Each of these groups has been discussed in detail [6].

Of primary concern in the present work are the localized structural glass defects [1-6] that can originate from several sources. Particulate contaminants (dust or reaction products) in the gas or vapor streams or on the substrate surface during chemical vapor deposition interfere with film nucleation and proper growth, resulting in voids, thin spots, partial or complete pinholes, or hillocks. Particulate impurities that become embedded in the film constitute a potential device failure due to local weakening of the dielectric strength.

Pinholes in the films can also be caused by problems in photo-lithographic processing if the photoresist protects the film incompletely, if the photomask causes mechanical damage during the contact printing step [3], or if the etchants used in the chemical patterning process penetrate through pinholes or thin spots in the resist coating itself. Pinholes in the glass overcoat may also be caused by aluminum grain growth during CVD [8,9] or by impact during chip handling [1,9,10]. Cracks in the CVD oxide or glass passivation over aluminum in linear bipolar ICs seem to be the cause of increased susceptibility of metal corrosion during device operation, which led to serious field failure [11,12]. Localized structural defects, in general, often open the way to migrating ionic contaminants [13] that are always present in plastic encapsulants or on the device surfaces after chip mounting, bonding, and normal processing operations.

Next to pinholes, microfractures are a very common and important mode of a localized defect often caused by excessive stress in the glass layer covering the metallization interconnects. Microfractures can also be caused by differences in the coefficients of thermal expansion between the dielectric film and the substrate or between different types of films. Stress in films may develop during growth, deposition, pattern etching or heat treatments, especially if the linear thermal expansions of the components are mismatched. Cracks may form, particularly during thermal shock preceding or following high-temperature processing, excessive thermal contraction on cooling, or temperature stress cycling and life-testing of devices. Silicon ICs packaged in frit-sealed ceramic packages have been particularly susceptible to microcracks in

the silicon dioxide or PSG overcoat, mostly over large areas of aluminum such as those used as the counterelectrodes of capacitors [1]. cause of this failure is the relatively high temperature (530°C) needed for fusion of the glass frit sealing the ceramic package. The stress in the glass overcoat passivation becomes so great that stress release occurs by cracking, especially over large metal areas and along their edges. Device failure may occur subsequently, due to penetration of sodium ions through the cracks and lateral penetration along the metal/ glass interface or in the field oxide. The sodium originates from the glass frit and cannot be avoided in the atmosphere of the package; it is normally gettered by the PSG. Similarly, tensile cracks can occur during eutectic bonding of devices, particularly when chip bonding temperature exceeds the glass deposition temperature. This may occur when gold-silicon eutectic bonding is used, and is chiefly true when aluminum-germanium eutectic alloy with a melting point of 424°C is used to achieve a hard-solder joint containing no elements of high atomic number. During the bonding operation, internal tension in the CVD film combined with stress caused by mismatch in linear coefficients of thermal expansion of silicon dioxide (or PSG) and aluminum (or thinfilm resistor alloy), can cause cracking of the passivation layer, often along the edges of delineated patterns of conductors.

Uneven topography of the substrate being coated with a dielectric film may result in thin spots over sharp edges or film discontinuities in corners at the base of steep steps, thereby leading to electrical short-circuits. Unacceptable topographical defects, such as excessive surface roughness, may also arise during film deposition under incorrect process conditions. Recent analytical results on localized structural defects in various types of glass overcoats on bipolar and CMOS devices have shown that, in addition to pinholes [5] and microcracks [9], defects frequently encountered are due to improper glass coverage of metal lines [9].

Gas bubbles that weaken the dielectric strength in an insulator may form during chemical vapor deposition in the presence of nucleating particulate contaminants. Other localized defects include embedded foreign particles, microcrystallites, or precipitates caused by reactions in the solid state. Oxides and glasses may devitrify in local regions under certain conditions, and may deleteriously affect film integrity and dielectric strength.

### 3.2 Conventional Methods for Defect Testing

Methods for testing dielectric films for the presence of localized structural defects may simply detect the defects by observation without altering them, or may make them more readily visible by decoration, by reaction, or by etching of the substrate.

Typical examples of direct detection methods are: optical microscopy, light-scattering techniques, scanning electron microscopy, transmission electron microscopy, and replica electron microscopy [1].

Examples of decoration methods are: electrophoretic particle transport techniques [1] and electrolytic decoration with copper oxysalts [14,15]. Methods based on reaction at the defect sites are nematic liquid-crystal light-scattering in an electric field to produce readily visible vortices above the defects [8,16]; formation of trains of hydrogen gas bubbles rising from the defect sites [14]; electroautographic techniques [14]; and self-limiting dielectric breakdown [17] where a deposited thin-metal film electrode disrupts, indicating the location of a defect.

Selective etching of the substrate to produce a readily visible pit or enlarged demarcation area is one of the earliest techniques used for revealing defects in dielectric films. In the case of silicon dioxide films on silicon, the etchant can be hot chlorine gas [18,19], pyrocatechol - ethylene diamine - water mixtures [20,21], catechol-hydrazine reagent [22], aqueous 10% sodium hydroxide solution at 70°C [23], or a common silicon etchant such as 70% nitric acid with 4 to 6% volume of 49% hydrofluoric acid. Silicon dioxide films on metal substrates require different treatments. Anodization or ceric sulfate etching have been described for nickel-chromium [24]; alkaline etchants [24], concentrated acid solution [25], or phosphoric acid-based etchants [1] for aluminum; and extended hot water treatments for molybdenum [25].

The defect detection methods enumerated above have been reviewed in detail and illustrated in a recent survey [1] and therefore will not be further discussed here.

#### 3.3 Shortcomings of Conventional Methods

Critical evaluation has shown great merit in most of these methods for specific applications. However, each of the methods available at the time we started our investigation under the present contract suffered from several or all of the following shortcomings: (1) destructive, and hence, expensive; (2) not sensitive to latent or partial defects (such as thin spots); (3) inadequate for production control; (4) slow and not suitable for automation; (5) subjective, because read-out by operator is required; (6) not standardized in present form and, hence not comparative on an absolute basis; (7) results ambiguous: not reproducible consistently or not reliable; and (8) applicable only to very specific problems, rather than generally applicable for testing any dielectric.

# 3.4 Methods Investigated and Developed During This Research Contract

The methods developed for evaluating the integrity of glass passivation overcoats on metallized ICs were to be based on measurements of density of pinholes, microcracks, and thin spots in dielectric by suitable techniques. The methods were to be applicable for the analysis and process control of both device wafers and single IC pellets and, furthermore, for detection of localized structural defects in dielectric layers on conductive substrates in general. The shortcomings of present methods listed in the previous sections were to be eliminated or, at least, minimized as much as possible.

From exploratory research performed prior to this contract we felt that a developmental research program based on the following methods would be most promising:

(1) Metal demarcation etching.

(2) Metal/Insulator sequential etching.

(3) Electrophoretic decoration with intensely uv-luminescing phosphor or powder particles.

(4) Electrostatic charging followed by direct or reverse decoration with phosphors or carbon black particles.

(5) Techniques for quantifying the defects found by the above techniques.

Method (1) is a conventional selective etching technique that would be optimized primarily as a baseline standard for comparing the performance of new techniques. Method (2) was intended to provide unique information on defect density as a function of dielectric layer The electrophoretic method (3) had been previously demonstrated to be feasible [1], but had not been optimized in any way. The electrostatic method (4) had also been outlined and demonstrated as feasible [1] and appeared to offer remarkable possibilities. Indeed, this method has proven to be the most useful and sensitive technique for dielectric defect detection now available, as will become apparent in the course of the presentations to follow. The measuring technique (5) was intended for rapid and quantitative read-out, preferably by optical techniques and suitable for automation. Standard optical and electron microscopic methods were to be used extensively for direct examination of defect sites. Finally, the best method(s) and techniques were to be formulated into one practical and reliable procedure suitable for routine device wafer quality control by manufacturers, as well as for acceptance testing and reliability analysis of single IC pellets.

#### 4. EXPERIMENTAL STUDIES AND METHOD DEVELOPMENT

#### 4.1 Metal Demarcation Etching

#### 4.1.1 Principle