# NBS SPECIAL PUBLICATION 400-25

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

# Semiconductor Measurement Technology

Progress Report

July 1 to December 31, 1975

100 157 10.400-25

#### NATIONAL BUREAU OF STANDARDS

The National Bureau of Standards was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of the Office of Measurement Services, the Office of Radiation Measurement and the following Center and divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Center for Radiation Research: Nuclear Sciences; Applied Radiation — Laboratory Astrophysics <sup>2</sup> — Cryogenics <sup>2</sup> — Electromagnetics <sup>2</sup> — Time and Frequency <sup>2</sup>.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials, the Office of Air and Water Measurement, and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry.

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services to promote the use of available technology and to facilitate technological innovation in industry and Government; cooperates with public and private organizations leading to the development of technological standards (including mandatory safety standards), codes and methods of test; and provides technical advice and services to Government agencies upon request. The Institute consists of the following divisions and Centers:

Standards Application and Analysis — Electronic Technology — Center for Consumer Product Technology: Product Systems Analysis; Product Engineering — Center for Building Technology: Structures, Materials, and Life Safety; Building Environment; Technical Evaluation and Application — Center for Fire Research: Fire Science; Fire Safety Engineering.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical services designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the selection, acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the executive branch for the development of Federal standards for automatic data processing equipment, techniques, and computer languages. The Institute consists of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific information generated within NBS and other agencies of the Federal Government; promotes the development of the National Standard Reference Data System and a system of information analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate services to ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of the following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Library — Office of International Relations — Office of International Standards.

<sup>&</sup>lt;sup>1</sup> Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

<sup>2</sup> Located at Boulder, Colorado 80302.

# Semiconductor Measurement Technology

Progress Report, July 1 to December 31, 1975

+ specon protection.

W. Murray Bullis, Editor

Electronic Technology Division Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234

Jointly Supported by:

The National Bureau of Standards,

The Navy Strategic Systems Projects Office,

The Space and Missile Systems Organization,

The Defense Nuclear Agency, and

The Defense Advanced Research Projects Agency

U.S. DEPARTMENT OF COMMERCE, Elliot L. Richardson, Secretary

Edward O. Vetter, Under Secretary

Dr. Betsy Ancker-Johnson, Assistant Secretary for Science and Technology

U. S. NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Acting Director

National Bureau of Standards Special Publication 400-25

Nat. Bur. Stand. (U.S.), Spec. Publ. 400-25, 87 pages (Oct. 1976)

CODEN: XNBSAV

### TABLE OF CONTENTS

#### SEMICONDUCTOR MEASUREMENT TECHNOLOGY

|                                            |                                                                                                                                                                    | PAGE                                       |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Prefa                                      | ace                                                                                                                                                                | viii                                       |

| 1.                                         | Introduction                                                                                                                                                       | . 2                                        |

| 2.                                         | Highlights                                                                                                                                                         | . 3                                        |

| 3.<br>3.1.<br>3.2.<br>3.3.                 | Resistivity                                                                                                                                                        | . 7<br>. 8                                 |

| 4.<br>4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5. | Physical Analysis Methods                                                                                                                                          | . 14<br>. 15<br>. 16<br>. 19               |

| 5.<br>5.1.<br>5.2.<br>5.3.<br>5.4.         | Test Structure Applications                                                                                                                                        | <ul><li>24</li><li>25</li><li>27</li></ul> |

| 6.<br>6.1.<br>6.2.<br>6.3.<br>6.4.         | Materials and Procedures for Wafer Processing Oxidation Furnace Contamination Ion Implantation Parameters Passivation Integrity Process Chemicals Characterization | . 29<br>. 31<br>. 33                       |

| 7.<br>7.1.                                 | Photolithography                                                                                                                                                   |                                            |

| 8.<br>8.1.<br>8.2.<br>8.3.<br>8.4.<br>8.5. | Emitter-Base Electrical Alignment Test Structure                                                                                                                   | . 39<br>. 40<br>. 41<br>. 43               |

| 9.<br>9.1.<br>9.2.<br>9.3.                 | Wire Bond Pull Test                                                                                                                                                | . 46<br>. 47                               |

| 10.1<br>10.1<br>10.2<br>10.3               | . Gas Infusion into Double Hermetic Enclosures                                                                                                                     | <ul><li>53</li><li>55</li></ul>            |

#### TABLE OF CONTENTS

| PI                                                         | AGE |

|------------------------------------------------------------|-----|

| 11. Device Inspection and Test                             | 58  |

| 11.1. Dual-Laser, Flying-Spot Scanner                      |     |

| 11.2. Automated Scanning Low Energy Electron Probe         |     |

| 11.3. Scanning Electron Microscopy — Voltage Contrast Mode |     |

| 11.4. Scanning Acoustic Microscopy                         |     |

| 12. Thermal Properties of Devices                          | 62  |

| 12.1. Thermal Resistance — Power Transistors               |     |

| 12.2. Thermal Resistance — Integrated Circuits             |     |

| 13. References                                             | 65  |

| Appendix A Semiconductor Technology Program Staff          | 70  |

| Appendix B Semiconductor Technology Program Publications   | 71  |

| Appendix C Workshop and Symposium Schedule                 | 73  |

| Appendix D Standards Committee Activities                  | 74  |

| Appendix E Solid-State Technology & Fabrication Services   | 76  |

| Index                                                      | 77  |

## LIST OF FIGURES

|     |                                                                                                                                                                                                                                                                                           | PA | GE |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|

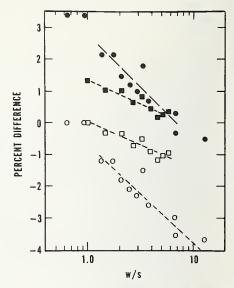

| 1.  | Percent difference between calculated and actual resistivity as a function of the ratio of the thickness, w, of a 25-mm diameter slice to the probe spacing, s                                                                                                                            |    | 8  |

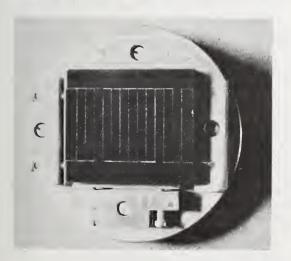

| 2.  | Photograph of typical specimen block                                                                                                                                                                                                                                                      |    | 9  |

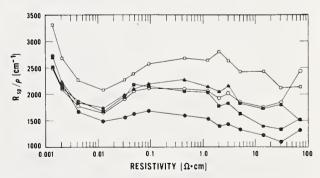

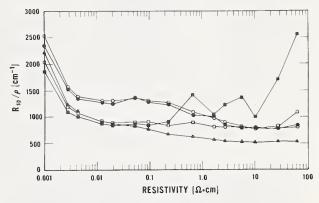

| 3.  | Ratio of spreading resistance, $R_{\rm sp}$ , to resistivity, $\rho$ , as a function of resistivity as measured with a variety of probe tips on a (111) $n$ -type silicon surface chem-mechanically polished with silica sol and baked out                                                |    | 9  |

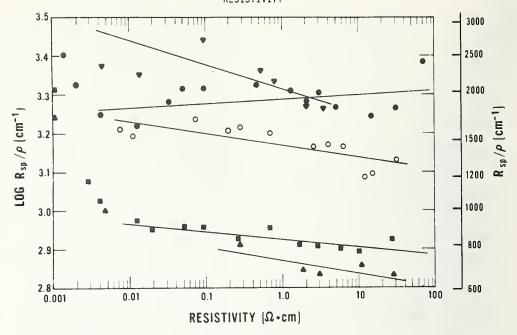

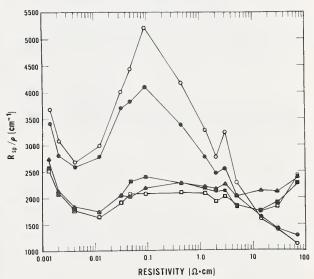

| 4.  | Ratio of spreading resistance, $R_{\text{Sp}}$ , to resistivity, $\rho$ , (logarithmic scale) as a function of resistivity as measured with freshly conditioned osmiumtungsten alloy probe tips on a variety of silicon surfaces chem-mechanically polished with silica sol and baked out |    | 10 |

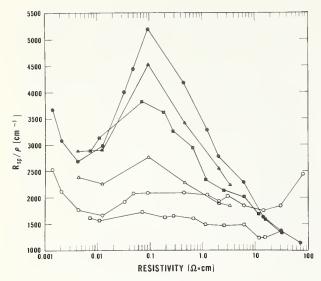

| 5.  | Ratio of spreading resistance, $R_{\rm sp}$ , to resistivity, $\rho$ , as a function of resistivity as measured with freshly conditioned osmium-tungsten alloy probe tips on (111) $p$ - and $n$ -type silicon surfaces prepared in various ways                                          |    | 11 |

| 6.  | Ratio of spreading resistance, $R_{\rm sp}$ , to resistivity, $\rho$ , as a function of resistivity as measured with freshly conditioned osmium-tungsten alloy probe tips on $n$ -type silicon surfaces showing extremes of behavior                                                      |    | 12 |

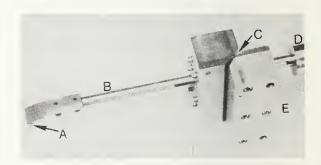

| 7.  | Hinged probe-arm assembly                                                                                                                                                                                                                                                                 |    | 12 |

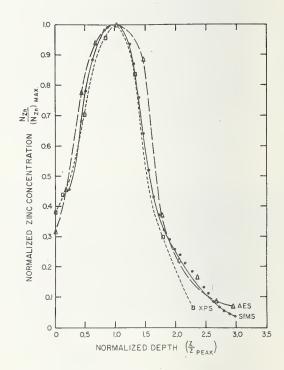

| 8.  | Normalized zinc concentration depth profiles as measured by secondary ion mass spectrometry, Auger electron spectroscopy, and X-ray photoelectron spectroscopy                                                                                                                            |    | 14 |

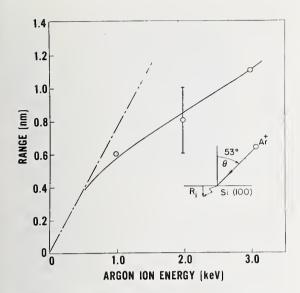

| 9.  | Energy dependence of argon ion range (penetration depth) in [100] direction of silicon                                                                                                                                                                                                    |    | 17 |

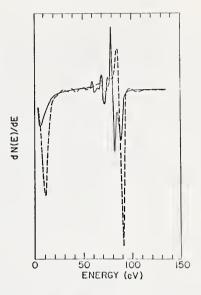

| 10. | Auger spectra from a (100) silicon surface                                                                                                                                                                                                                                                |    | 17 |

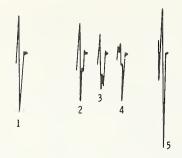

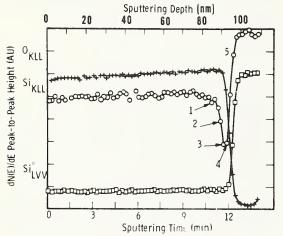

| 11. | Chemical depth profiles through about 100 nm of silicon dioxide thermally grown on a (100) silicon surface                                                                                                                                                                                |    | 18 |

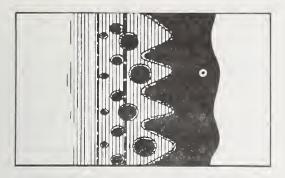

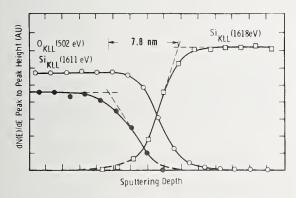

| 12. | Details of interface region                                                                                                                                                                                                                                                               |    | 19 |

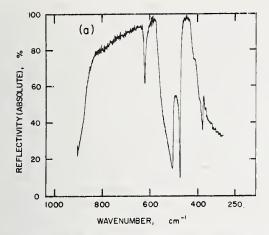

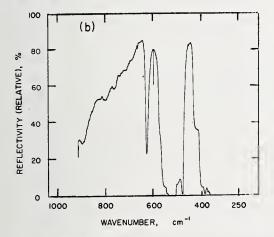

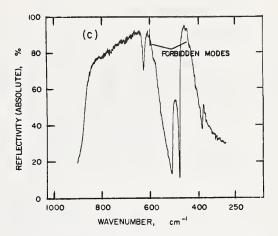

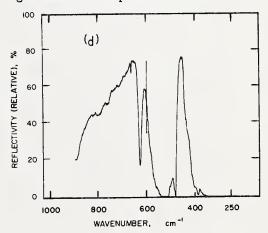

| 13. | Reflection spectra of undamaged and damaged sapphire                                                                                                                                                                                                                                      |    | 23 |

| 14. | Redistribution profile of boron in silicon following an 18-min steam oxidation at 1100°C                                                                                                                                                                                                  |    | 25 |

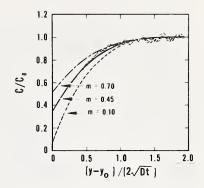

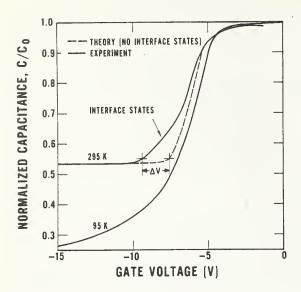

| 15. | Distortion of the room temperature high frequency C-V characteristic of an <i>n</i> -type silicon MOS capacitor which results from the presence of interface states                                                                                                                       |    | 26 |

| 16. | Thermally stimulated current response of interface states in an $n$ -type silicon MOS capacitor for various values of gate voltage, $V_g$                                                                                                                                                 |    | 26 |

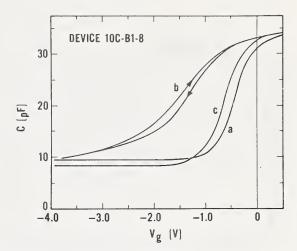

| 17. | Effect of electron-beam irradiation on the capacitance-voltage characteristics of an <i>n</i> -type silicon MOS capacitor                                                                                                                                                                 |    | 27 |

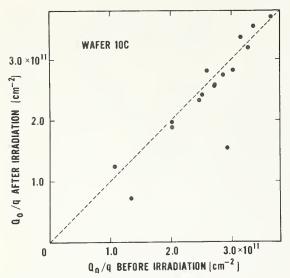

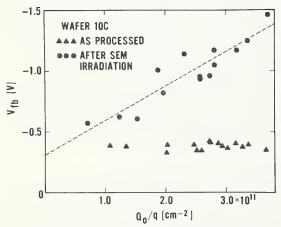

| 18. | Comparison of mobile ion density, $Q_0/q$ , before and after electron beam irradiation and thermal anneal                                                                                                                                                                                 |    | 28 |

| 19. | Flat-band voltage, $V_{fb}$ , as a function of mobile ion density, $Q_o/q$ , before and after electron beam irradiation and thermal anneal                                                                                                                                                |    | 28 |

| 20. | Experimental arrangement for sodium detection in a semiconductor processing furnace by resonance fluorescence                                                                                                                                                                             |    | 29 |

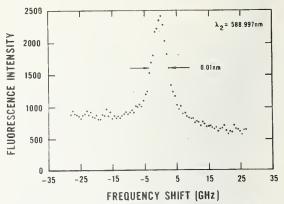

| 21. | Typical sodium fluorescence signal detected in an intentionally contaminated quartz furnace tube at atmospheric pressure and 1000°C                                                                                                                                                       |    | 30 |

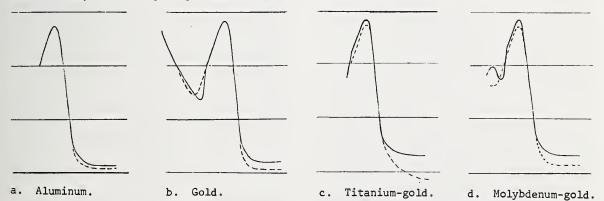

| 22. | Representation of capacitance-voltage profiles for four Schottky barrier                                                                                                                                                                                                                  |    | 31 |

#### LIST OF FIGURES

|     |                                                                                                                                                                                                       |   |      | P. | AGE |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|-----|

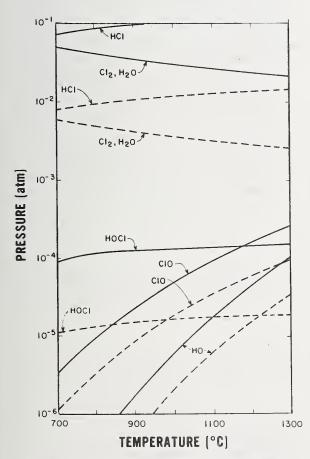

| 23. | Equilibrium partial pressures in 2% HCl-98% $\rm O_2$ and 20% HCl-80% $\rm O_2$ mixtures                                                                                                              |   |      |    | 35  |

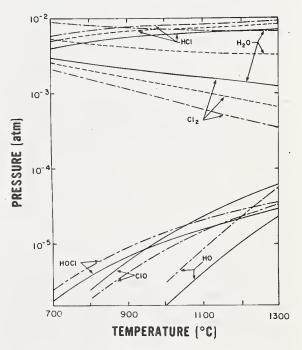

| 24. | Equilibrium partial pressures in $1\%$ HCl-99% $O_2$ mixtures with 0, 0.26%, and 0.66% added water vapor                                                                                              |   |      |    | 35  |

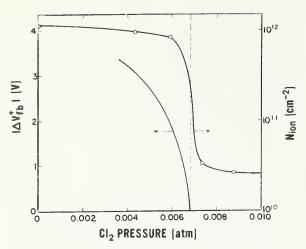

| 25. | Mobile ion density, $N_{ion}$ , and magnitude of the flat-band voltage shift, $\Delta V_{fb}^{\dagger}$ , as a function of equilibrium chlorine pressure in HCl oxidations on (100) silicon at 1150°C |   |      |    | 36  |

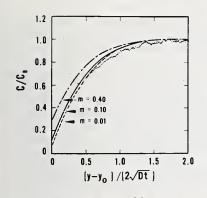

| 26. | Exposure time required to obtain a critical chromophore concentration, $M_{\text{C}}$ , in an infinitesimal layer located at the extreme thickness of the film                                        |   |      |    | 38  |

| 27. | Magnitude of resistivity measurement errors for four-probe arrays                                                                                                                                     |   |      |    | 39  |

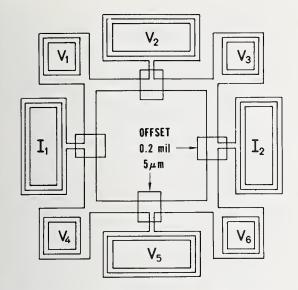

| 28. | Emitter-base alignment resistor                                                                                                                                                                       |   |      |    | 41  |

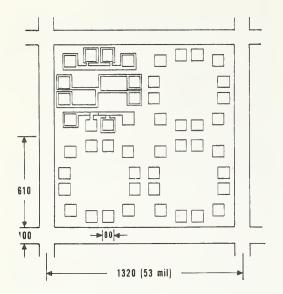

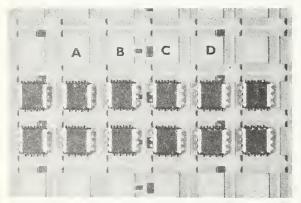

| 29. | Test pattern with four 4 by 4 square test cells                                                                                                                                                       | • |      |    | 42  |

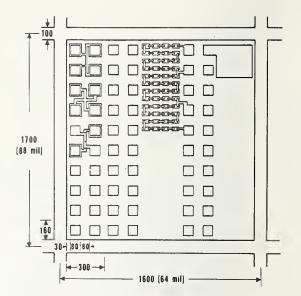

| 30. | Test pattern with 2 by 10 rectangular test cells                                                                                                                                                      |   |      |    | 42  |

| 31. | Photomicrograph of test pattern NBS-3 fabricated on 2-in. (50 mm) diameter wafer                                                                                                                      | • | <br> |    | 42  |

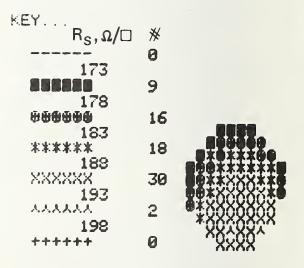

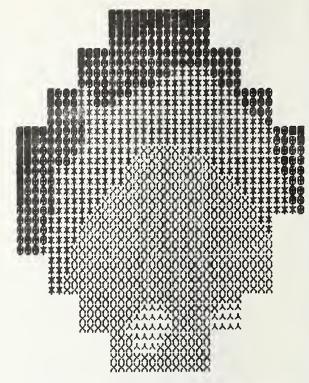

| 32. | Base sheet resistance wafer map with data points only                                                                                                                                                 |   | <br> |    | 42  |

| 33. | Base sheet resistance wafer map with interpolated points                                                                                                                                              |   |      |    |     |

| 34. | Photomicrograph of a patterned substrate showing chromium oxide areas (stained black) and bonded beam-lead devices                                                                                    |   |      |    |     |

| 35. | Photomicrograph of a portion of a patterned substrate from which bonded beam-lead devices have been pulled off                                                                                        |   | <br> |    | 46  |

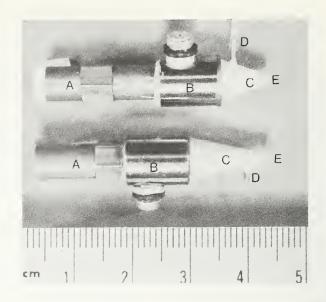

| 36. | Two acoustic emission detectors with waveguide probes and die-vacuum cups .                                                                                                                           |   | <br> |    | 48  |

| 37. | Substrate detector mounts                                                                                                                                                                             |   | <br> |    | 48  |

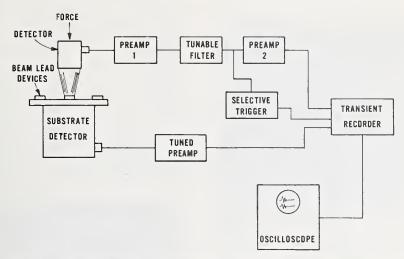

| 38. | Schematic diagram of acoustic emission detection apparatus                                                                                                                                            |   | <br> |    | 49  |

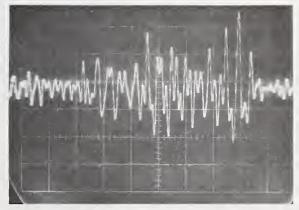

| 39. | Combined substrate-die acoustic emission waveform from a device with a poorly bonded corner beam lead stressed to 6 gf (59 mN)                                                                        | • | <br> |    | 49  |

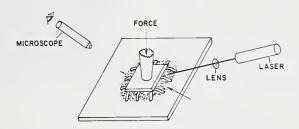

| 40. | Illustration of use of static interference pattern to observe the thres-hold of mechanical movement                                                                                                   | • | <br> |    | 49  |

| 41. | Scanning electron micrograph of a double-grooved, tungsten carbide tool for ultrasonic bonding                                                                                                        |   | <br> |    | 50  |

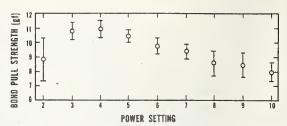

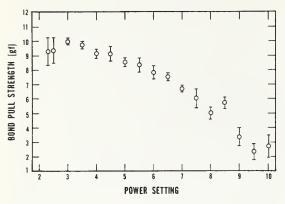

| 42. | Bond pull strength as a function of first-bond power setting for ultrasonic bonds made with 25- $\mu$ m diameter gold wire                                                                            |   | <br> |    | 50  |

| 43. | Scanning electron micrographs of typical gold ultrasonic wire bonds made under referred conditions with a double-grooved tool                                                                         |   | <br> |    | 50  |

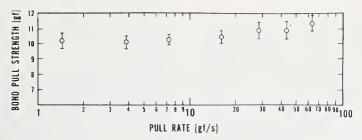

| 44. | Bond pull strength as a function of pull rate for ultrasonic bonds made with 25- $\mu$ m diameter gold wire under preferred conditions                                                                |   | <br> |    | 51  |

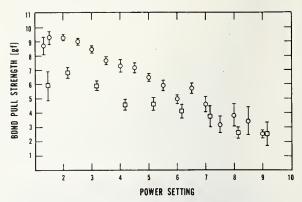

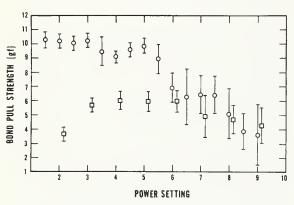

| 45. | Bond pull strength as a function of first-bond power setting for ultrasonic wire bonds made with aluminum-1% silicon wire                                                                             |   | <br> |    | 52  |

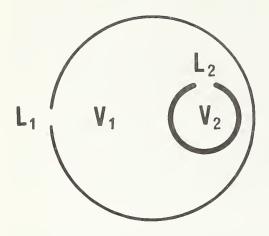

| 46. | Schematic diagram of double hermetic enclosure                                                                                                                                                        |   | <br> |    | 54  |

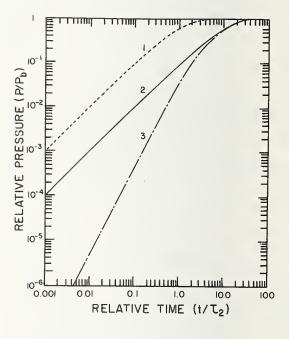

| 47. | Pressure-time curves for enclosures immersed in a gas of pressure $P_{\hat{b}}$ at time $t$ = 0                                                                                                       |   | <br> |    | 54  |

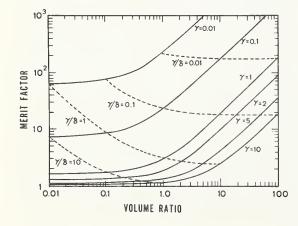

| 48. | Merit factor for double hermetic enclosures for various values of leak size ratios $(\gamma)$ and volume ratios $(\delta)$                                                                            |   | <br> |    | 54  |

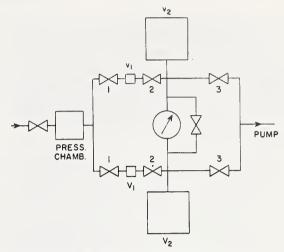

| 49. | Schematic diagram of apparatus for static-expansion, differential-pressure gross leak test                                                                                                            |   | <br> |    | 55  |

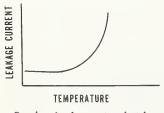

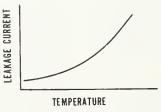

| 50. | Leakage current-temperature characteristics for dew point sensors                                                                                                                                     |   |      |    | 56  |

#### LIST OF FIGURES

|     | PAGE                                                                                                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------|

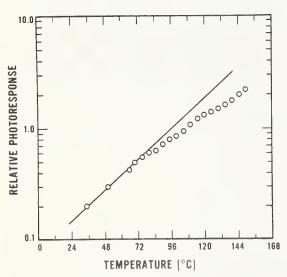

| 51. | Photoresponse of substrate $p-n$ junction as a function of temperature                                                       |

| 52. | X-ray topograph of a 63-mm diameter silicon wafer containing process-induced defects                                         |

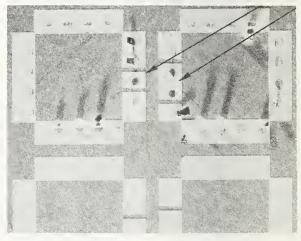

| 53. | ASLEEP image of 2.5 by 2.5 mm area of portion of silicon wafer showing polishing damage                                      |

| 54. | ASLEEP image of 6.3 by 6.3 mm area of portion of silicon wafer showing damage due to spin cleaning                           |

| 55. | ASLEEP image of 2.5 by 2.5 mm area of portion of silicon wafer showing apparent dislocation lines                            |

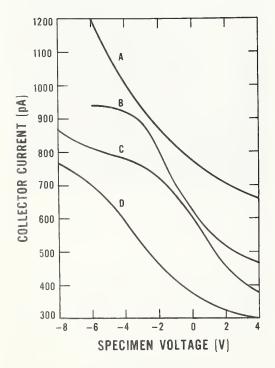

| 56. | Output of cylindrical detector for various operating conditions as given in table 10                                         |

| 57. | Cooling curves for a transistor operated with a collector current of 4 A and various emitter-collector voltages              |

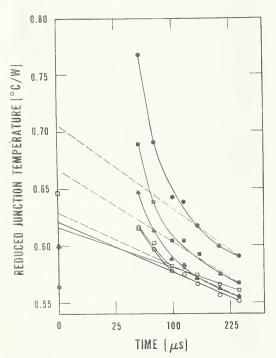

| 58. | Computed cooling curves for square heat sources of various sizes located at the top surface of a semi-infinite plane         |

| 59. | Photomicrograph of integrated transistor array with each transistor individually pinned out                                  |

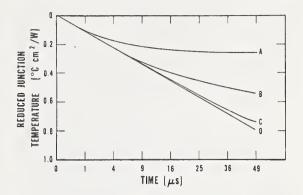

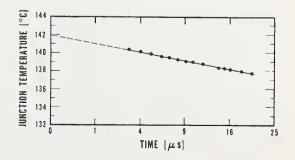

| 60. | Cooling curve for typical individually pinned-out integrated circuit transistor for a case temperature of 50°C               |

|     | LIST OF TABLES                                                                                                               |

|     | PAGE                                                                                                                         |

| 1.  | Values of the Correction Factor $G_7(w/s)$ for Finite Specimen Thickness                                                     |

| 2.  | Linear Regression Coefficients for Spreading Resistance Calibration Plots 10                                                 |

| 3.  | Hardness of Probe Tip Materials                                                                                              |

| 4.  | Substrate Purity Evaluation                                                                                                  |

| 5.  | Sodium Trace Contamination Measurements by Flame Emission Spectrometry 20                                                    |

| 6.  | Calculated Optical Constants for $(\overline{11}02)$ Sapphire with Various Surface Polishes, S Polarization                  |

| 7.  | Effect of Constant Reflectance Error, ΔR, Introduced in Calculation of Optical Constants for (1102) Sapphire, S Polarization |

| 8.  | Capacitor and Redistribution Parameters                                                                                      |

| 9.  | Resistivity Correction Factors for Square Four-Probe Arrays                                                                  |

| 10. | Detector Bias Conditions                                                                                                     |

The Semiconductor Technology Program serves to focus NBS efforts to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in specifying materials and devices in national and international commerce and for use by industry in controlling device fabrication processes. Its major thrusts are the development of carefully evaluated and well documented test procedures and associated technology and the dissemination of such information to the electronics community. Application of the output by industry will contribute to higher yields, lower cost, and higher reliability of semiconductor devices. The output provides a common basis for the purchase specifications of government agencies which will lead to greater economy in government procurement. In addition, improved measurement technology will provide a basis for controlled improvements in fabrication processes and in essential device characteristics.

The Program receives direct financial support principally from two major sponsors: the Defense Advanced Research Projects Agency (ARPA) $^*$  and the National Bureau of Standards (NBS). Tn addition, the Program receives support from the Defense Nuclear Agency (DNA), § Air Force Space and Missiles Systems Organization, and the Navy Strategic Systems Project Office. # The ARPA-supported portion of the Program, Advancement of Reliability, Processing, and Automation for Integrated Circuits with the National Bureau of Standards (ARPA/IC/NBS), addresses critical Defense Department problems in the yield, reliability, and availability of digital monolithic integrated circuits. Other portions of the Program emphasize aspects of the work which relate to the specific needs of the supporting agency. Measurement oriented activity appropriate to the mission of NBS is an essential aspect in all parts of the Program.

Essential assistance to the Program is also received from the semiconductor industry through cooperative experiments and technical exchanges. NBS interacts with industrial users and suppliers of semiconductor devices through participation in standardizing organizations; through direct consultations with device and material suppliers, government agencies, and other users; and through periodically scheduled symposia and work-

shops. In addition, progress reports, such as this one, are regularly prepared for issuance in the NBS Special Publication 400sub-series. More detailed reports such as state-of-the-art reviews, literature compilations, and summaries of technical efforts conducted within the Program are issued as these activities are completed. Reports of this type which are published by NBS also appear in the Special Publication 400- subseries. Announcements of availability of all publications in this sub-series are sent by the Government Printing Office to those who have requested this service. A request form for this purpose may be found at the end of this report.

Another means of interaction with the electronics community is by direct contact. In particular, comments from readers regarding the usefulness of the results reported herein and relating to directions of future activity in the Program are always welcome.

#### Disclaimer

Certain commercially available materials or instruments are identified in this publication for the purpose of providing a complete description of the work performed. The experiments reported do not constitute a complete evaluation of the performance characteristics of the products so identified. In no case does such identification imply recommendation or endorsement by the National Bureau of Standards nor does it imply that the items identified are necessarily the best available for the purpose.

<sup>\*</sup>Through ARPA Order 2397, Program Code 6D10 (NBS Cost Center 4257555). All contract work was funded from this source.

<sup>†</sup>Through Scientific and Technical Research Services Cost Center 4257100.

Through Inter-Agency Cost Reimbursement Order 76-806 (NBS Cost Center 4259522).

Through MIPR FY76 167600366 (NBS Cost Center 4259560).

<sup>\*\*</sup>Code SP-23, through project order NO016475P070030 administered by Naval Ammunition Depot, Crane, Indiana (NBS Cost Center 4251533).

#### SEMICONDUCTOR MEASUREMENT TECHNOLOGY

PROGRESS REPORT

July 1 to December 31, 1975

Abstract: This progress report describes NBS activities directed toward the development of methods of measurement for semiconductor materials, process control, and devices. Both in-house and contract efforts are included. The emphasis is on silicon device technologies. Principal accomplishments during this reporting period included (1) preliminary results of a systematic study of the effects of surface preparation on spreading resistance measurements; (2) development of an optical test for surface quality of sapphire; (3) development of a basis for an exposure sensitivity specification for photoresists; and (4) development of a modular cell concept for test structure design and layout. Also reported are the results of work on four-probe resistivity measurements, comparison of techniques for surface analysis, ion microprobe mass analysis, analysis of process chemicals with flame emission spectrometry, redistribution profiles, thermally stimulated current response of interface states, bias-temperature stress test measurements on MOS capacitors, a high voltage capacitance-voltage method for measuring characteristics of thick insulator films, hydrogen chloride oxidation, ion implantation parameters, methods for determining integrity of passivation overcoats, measurement of free sodium in an oxidation furnace by resonance fluorescence, a square array collector resistor test structure, an electrical alignment test structure, two dimensional wafer maps, test pattern design and analysis for silicon-on-sapphire MOS device technologies, a nondestructive acoustic emission test for beam-lead bonds, wire bond pull test, bondability of doped aluminum metallizations, leakage into double hermetic enclosures, a static expansion dry gas gross leak test, correlation of moisture infusion in semiconductor packages with leak size and device reliability, an automated scanning lowenergy electron probe, an optical flying-spot scanner, scanning electron microscopy, scanning acoustic microscopy, and thermal resistance measurements on power transistors and simple integrated circuits. Supplementary data concerning staff, publications, workshops and symposia, standards committee activities, and technical services are also included as appendices.

Key Words: Acoustic emission; Auger electron spectroscopy; beam-lead bonds; bias-temperature stress test; boron redistribution; capacitance-voltage methods; dopant profiles; electrical properties; electronics; four-probe method; hermeticity; interface states; ion implantation; ion microprobe mass analysis; leak tests; measurement methods; microelectronics; moisture infusion; optical flying-spot scanner; passivation overcoats; photoresist; pull test; resistivity; scanning acoustic microscope; scanning electron microscope; scanning low energy electron probe; semiconductor devices; semiconductor materials; semiconductor process control; silicon; silicon dioxide; silicon on sapphire; spreading resistance; test patterns; thermal resistance; thermally stimulated current; ultrasonic wire bonding; voltage contrast mode; X-ray photoelectron spectroscopy.

#### 1. INTRODUCTION

This is a report to the sponsors of the Semiconductor Technology Program on work during the twenty-ninth and thirtieth quarters of the Program. It summarizes work on a wide variety of measurement methods for semiconductor materials, process control, and devices that are being studied at the National Bureau of Standards. The Program, which emphasizes silicon-based device technologies, is a continuing one, and the results and conclusions reported here are subject to modification and refinement.

The work of the Program is divided into a number of tasks, each directed toward the study of a particular material or device property or measurement technique. This report is subdivided according to these tasks. Highlights of activity during the quarters are given in section 2. Subsequent sections deal with each specific task area. References cited are listed in the final section of the report.

The report of each task includes a narrative description of progress made during this reporting period. Additional information concerning the material reported may be obtained directly from individual staff members identified with the task in the report.

Background material on the Program and individual tasks may be found in earlier progress reports as listed in Appendix B. From time to time, publications are prepared that describe some aspect of the program in greater detail. Current publications of this type are also listed in Appendix B. Reprints or copies of such publications are usually available on request to the author.

In addition tutorial videotapes are being prepared on selected measurement topics for dissemination to the electronics community. Currently available videotapes and procedures for obtaining them on loan are also listed in Appendix B.

Communication with the electronics community is a critical aspect both as input for guidance in planning future program activities and in disseminating the results of the work to potential users. Formal channels for such communication occur in the form of workshops and symposia sponsored or cosponsored by NBS. Currently scheduled seminars and workshops are listed in Appendix C. In addition, the availability of proceedings from past workshops and seminars is indicated in the appendix.

An important part of the work that frequently goes beyond the task structure is participation in the activities of various technical standardizing committees. The list of personnel involved with this work given in Appendix D suggests the extent of this participation. In most cases, details of standardization efforts are reported in connection with the work of a particular task.

Technical services in areas of competence are provided to other NBS activities and other government agencies as they are requested. Usually these are short-term, specialized services that cannot be obtained through normal commercial channels. To indicate the kinds of technology available to the Program, such services provided during the current calendar year are listed in Appendix E.

#### 2. HIGHLIGHTS

Highlights of progress in the various technical task areas of the program are listed in this section. Unless otherwise identified the work was performed at the National Bureau of Standards.

Particularly significant accomplishments during this reporting period included (1) preliminary results of a systematic study of the effects of surface preparation on spreading resistance measurements; (2) development of an optical test for surface quality of sapphire; (3) development of a basis for an exposure sensitivity specification for photoresists; and (4) development of a modular cell concept for test structure design and layout.

<u>Resistivity</u> — The range of validity of existing correction factors for measurement of the resistivity of wafers with finite diameter by the four-probe method was studied experimentally for specimens of intermediate thickness. The results of this study enable measurements of resistivity on specimens in a range of diameter and thickness not previously covered by ASTM standards.

A systematic study of the effect of surface preparation, surface orientation, probe material, and probe condition on measured spreading resistance was nearly completed. The initial results suggest that there is no significant dependence of the form of the relationship between spreading resistance and resistivity on probe material or condition; however, statistically significant differences were observed between wafers of various surface orientation and conductivity type for all probe materials. In addition, differences were observed between various surface preparation techniques.

Further work on the development of the highspeed spreading resistance probe at RCA Laboratories was concerned principally with the problem of excessive probe wear.

Physical Analysis Methods — Comparison of impurity profiles measured by ion microprobe mass analysis, Auger electron spectroscopy, and x-ray photoelectron spectroscopy showed that in the absence of calibration standards, only relative results could be obtained. Further, in the case of the latter two spectroscopies, difficulties were encountered in calibrating the penetration depth so that both the density and depth scales could only be determined on a relative basis.

Development of calibration standards for ion microprobe mass analysis at Texas Instruments continued with characterization of machine parameters, characterization of silicon wafers to be used for specimen preparation, and implantation of specimens with phosphorus dots.

Initial results of the study of Auger electron spectroscopy, being conducted jointly by Stanford University and Varian Associates, included observation of the desorption of oxygen by an electron beam on both silicon dioxide and unsaturated silicon oxides and the use of the chemical shift of the Auger Si<sub>KLL</sub> transition to develop a model for the silicon-silicon dioxide interface. The latter data suggest that the microscopic mixture model is preferred to the random bonding model for unsaturated silicon oxides. In addition, results were obtained relating to ion penetration depth, ion stimulated Auger transitions, and carbon contamination.

Sodium contamination in a variety of materials used for fabrication of semiconductor devices was determined by means of flame emission spectrometry. This technique provides a sensitive method for monitoring trace sodium content in both solid and liquid materials. No significant trends in sodium contamination level were observed when the results obtained were compared with the results published 2 to 7 years ago.

Additional work on the rapid, nondestructive infrared reflectance technique being developed at RCA Laboratories to determine the surface quality of sapphire substrates has demonstrated that there is correlation between the infrared reflectance signal and the surface roughness of a substrate.

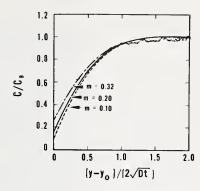

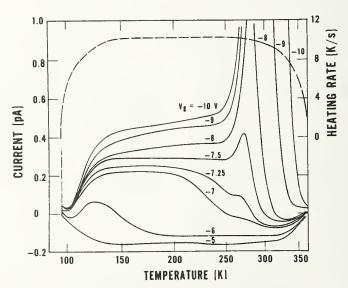

Test Structure Applications — The boron redistribution profile of an oxidized silicon wafer was measured by means of the dynamic MOS C-V deep depletion method; the experimentally measured profile could be fitted by that derived theoretically if appropriate values of the boron diffusion and distribution coefficients were chosen.

The thermally stimulated current response of the energy states found at the oxide-silicon interface of an *n*-type MOS capacitor were observed. The response can be modeled by a continuum of energy levels in the forbidden gap of silicon, but no detailed analysis was undertaken.

Comparison of flat band voltage shifts obtained by means of the bias-temperature stress test before and after electron beam irradiation without bias suggests that there is a correlation between the shift due to radiation and the mobile charge density in the oxide and that irradiation does not appear to affect the density of mobile charge. No further work on the bias-temperature stress test is planned.

Further instrumental improvements were made in the extended-range high voltage capacitance apparatus being developed at RCA Laboratories to measure capacitance-voltage characteristics of thick insulators. The previously incorporated bias protection circuitry was shown to be effective in preventing damage to the capacitance meter following breakdown of the specimen.

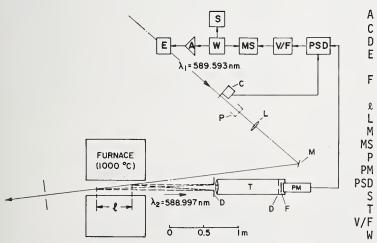

Materials and Procedures for Wafer Processing - In connection with the development of qualification procedures for oxidation furnaces, a tunable dye laser has been used to detect, by means of resonance fluorescence, sodium in an open quartz tube oxidation furnace operated at 1000°C. The detection limit for free sodium was estimated to be approximately 5  $\times$  10  $^{5}$  cm<sup>-3</sup>. A sodium density of about 2  $\times$  10  $^{7}$  cm<sup>-3</sup> was observed in an intentionally contaminated furnace; preliminary analysis suggests that much more sodium is present in other forms than is present as free sodium and that, even with its great sensitivity, the resonance fluorescence technique may be inadequate for monitoring sodium contamination during oxidation.

Data collection continued in connection with the study of ion implantation parameters at Hughes Research Laboratories. The characteristics and limitations of the Schottky barrier capacitance-voltage technique for measuring implanted profiles were investigated for various experimental conditions. Additional data were collected on profiles for a number of impurities; preliminary data were obtained on the sensitivity of the profile to the angle of incidence and crystallographic direction. In addition, initial experiments related to measurement of total dose were carried out with emphasis on the study of suppression of secondary electron emission; these results will be reported in detail at a later date.

In the study of methods for measuring the integrity of passivation overcoats at RCA Laboratories, optimum etch conditions were es-

tablished for use with the selective chemical etch method, nonluminescing materials were found to be less suitable than luminescing materials for defect decoration, and the corona decoration method was shown to be superior to the more commonly employed electrophoretic cell method.

In the study of methods for characterizing process chemicals, being conducted at Pennsylvania State University, calculations of the equilibrium partial pressures of the various species in the chlorine-hydrogen-oxygen system was carried out. The effect of the presence of excess water vapor was also investigated. Comparison with published experimental data suggests that the chlorine pressure is the critical parameter and that it can be controlled by a combination of the amount of added hydrogen chloride gas and the water vapor concentration.

<u>Photolithography</u> — An analysis of the photoresistance exposure process was undertaken to establish a basis for specification of exposure sensitivity. The results suggest that a set of material-related parameters can be used to determine the speed of photoresist materials appropriate to a particular exposure apparatus.

Analysis of automated methods for inspecting photomasks was completed at Lawrence Livermore Laboratories; a report on this work is being prepared. Preliminary evaluation of a diffraction-based optoelectronic method for measuring small dimensions was completed at Recognition Systems, Inc. In this work, which will be reported in detail at a later date, it was shown that resolution comparable with that obtained in the scanning electron microscope could be achieved without the necessity of a vacuum chamber.

Theoretical studies have been initiated on the effect on the adjacent line on line-width measurements with an optical microscope used in the conventional fashion. In addition, work has been initiated on application of the spatial filtering technique to line-width measurement with an optical microscope. Preliminary results have been obtained in both studies and detailed reports are being prepared.

<u>Test Patterns</u> — The square array collector resistor test structure was analyzed to determine correction factors for use when the backside of the structure is conducting. It was found that the correction can be ignored for most cases of practical interest.

An electrical test structure was designed for the purpose of evaluating the amount of misalignment between emitter and base regions in a bipolar process.

Investigation of modular concepts for test structure design and test pattern layout led to the selection of a rectangular cell with a 2 by 10 probe pad array as the basis for standardization. Modularization of the pattern in the cells is crucial to the testing strategy and permits standardization of the entire test structure design including probe pads and metallization runs. In order to implement these concepts in connection with a specific integrated circuit technology, a T<sup>2</sup>L test pattern which includes a simple NAND gate is being designed and fabricated.

Computer programs were developed to permit the display of the geometrical variation of parameters obtained from measurements on test structures as whole wafer density maps. The program permits interpolation of data between actually measured points which facilitates the interpretation of the wafer map.

The design of the test structures for use in the test pattern being developed at RCA Laboratories for SOS/LSI technology was completed and fabrication of the mask set was initiated.

Interconnection Bonding — Procedures were refined for fabricating beam-lead devices with a few weak bonds for use in studying the non-destructive acoustic emission test for evaluating the quality of beam-lead bonds. In addition, several instrumental changes were made to improve detection sensitivity. In the course of this study, a novel method was developed to determine the downward force necessary to produce threshold deflections of a bonded beam-lead die.

A study showed that there is no dependence of the measured pull strength on the rate of pull of ultrasonic gold wire bonds. A similar result had been obtained previously for ultrasonic aluminum wire bonds, but verification for gold wire was desired to increase the scope of a pull test method being developed by ASTM Committee F-1 on Electronics. During this study it was found that a double deep-grooved bonding tool was most suitable for making ultrasonic bonds with fine gold wire.

The suitability of silicon- and copper-doped aluminum metallizations for ultrasonic bonding of aluminum ribbon and round wire was

determined. A satisfactory bonding schedule could be developed for all metallizations studied; as with pure aluminum metallization, it was found that ribbon wire exhibited a higher pull strength for a broader range of bonding conditions than round wire.

Hermeticity — An analysis was made of the infusion of dry gas into a hermetic double enclosure with specified leak sizes in each container. It was found that simply surrounding one hermetic enclosure by another does not assure hermetic improvement, although it is obviously a protection against a badly leaking inner enclosure. Significant enhancement was obtained only if the leak size in the outer enclosure was less than 10 times that of the inner enclosure or if the free volume of the outer enclosure was at least 10 times that of the inner one.

The dry gas, static-expansion, differential-pressure gross leak test was analyzed to determine the relationship between the meter indication and leak size in the device under test. It was found that the leak size is related to the rate of rise of the meter indication at very early times and that the internal free volume of the device under test is related to the equilibrium indication.

The initial effort on moisture measurements in integrated circuit packages was completed at Martin Marietta-Orlando. Preliminary calibrations were run on the dew point sensors and an instability of the microvent leaks which was observed under pressure was corrected by modifying the design.

<u>Device Inspection and Test</u> — The automated scanning low energy electron probe, being developed at the Naval Research Laboratory, was applied to the study of wafer defects. Evidence of both surface contamination and crystal defects was observed, but additional work will be necessary to permit detailed correlation of the observations with appropriate causes.

The photoresponse of the substrate diode of an integrated circuit to low-power 1.15-µm laser irradiation was calibrated in terms of device temperature as an additional example of the usefulness of the optical flying-spot scanner for thermal mapping. Significant deviations from the curve predicted by simple theory were observed at temperatures above about 75°C.

Tests of the cylindrical secondary electron detector intended to improve the sensitivity

of the scanning electron microscope in the voltage contrast mode showed that the voltage sensitivity was substantially improved. However, as it is presently constructed, the spatial resolution of this detector is inadequate for use in examining integrated circuits; additional modifications are not planned at the present time.

Studies of scanning acoustic microscopy as a technique for the inspection of semiconductor devices and integrated circuits were initiated at Hughes Research Laboratories and Stanford University. This technique has been shown to have  $2\text{--}\mu\text{m}$  resolution and it is thought to be capable of observing subsurface defects.

<u>Thermal Properties of Devices</u> — It was found that the electrical switching transients which occur on switching a transistor out of the quasi-saturation mode do not permit ac-

curate measurements of thermal resistance to be made using the standard emitter-only switching technique. This mode of operation occurs in some devices under the high current, low voltage conditions often used for making thermal resistance measurements.

A study of several techniques for measuring thermal resistance of integrated circuits was completed. It was found that the forward voltage of the collector-substrate isolation junction is not a satisfactory temperature sensitive parameter for determining the peak temperature of an integrated circuit. Peak temperature determination by electrical means appears to be possible only if the heat generating element is accessible at the pins of the circuit. The sensitivity of the forward voltage of the isolation junction as the temperature sensitive parameter for determining the quality of the die attach of integrated circuits remains to be evaluated.

#### 3.1. Four-Probe Method

Resistivity measurements by the four-probe method are covered by ASTM standard test methods only if the slice thickness is less than the probe spacing [1] or if it is greater than four times the probe spacing [2]. Slices with thickness between one and four times the probe spacing are frequently used for production control of silicon crystal growth and for spreading resistance calibration sets. This task was undertaken to identify appropriate geometrical correction factors for use in this range.

Geometrical correction factors in these standards are derived from the basic equation for resistivity,  $\rho$ , measured with a collinear, equally-spaced, four-probe array [3]:

$$\rho = 2\pi s \frac{V}{\tau} , \qquad (1)$$

where V is the potential difference between the inner pair of probes, I is the current between the outer pairs of probes and s is the spacing between adjacent probes. The ASTM method for four-probe measurements on semi-infinite solids [2] requires the use of no correction factors for geometry; eq (1) is corrected only for non-uniform probe spacing and for temperature variation of resistivity:

$$\rho = 2\pi s F_{SP} F_{T} \frac{V}{I} , \qquad (1a)$$

where  $F_{sp} = 1 + 1.25[1-(s_2/s)]$ .  $s_2$  is the spacing between the inner two probes, s is the average probe spacing,  $F_T = 1 - C_T(T-23)$ ,  $C_T$  is the temperature coefficient of resis-

Table 1 — Values of the Correction Factor  $G_7(w/s)$  for Finite Specimen Thickness

| w/s                                                                           | G <sub>7</sub> (w/s)                                                         |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1.000<br>2.000<br>3.000<br>4.000<br>5.000<br>6.000<br>7.000<br>8.000<br>9.000 | 1.5045<br>1.0939<br>1.0306<br>1.0134<br>1.0070<br>1.0041<br>1.0026<br>1.0017 |

| 10.000                                                                        | 1:0007                                                                       |

tivity [1], and T is the temperature, in degrees Celsius, of the specimen at the time of measurement. In this method it is stated that the maximum error introduced by geometrical effects is less than 2 percent if the thickness of the specimen and the distance from any probe to the nearest point on the edge are at least four times the probe spacing.

Valdes [3] derived, from the method of images, a factor,  $G_7(w/s)$  to correct eq (1) for finite thickness, w:

$$\rho = \frac{2\pi s}{G_7(w/s)} \frac{V}{I} , \qquad (1b)$$

where  $G_7(w/s)$  is tabulated in table 1. In the limit of a very thin sheet,  $G_7(w/s)$  approaches the value of (2s/w) ln2 and the resistivity becomes

$$\rho = \frac{\pi}{\ln 2} \le \frac{V}{I} . \tag{2}$$

Smits [4] has reported an equivalent factor, F(w/s), calculated from formulae given by Uhlir [5], to correct eq (2) for finite values of w:

$$\rho = \frac{\pi}{\ln 2} \text{ w } F(\text{w/s}) \frac{\text{V}}{\text{I}}, \qquad (2a)$$

where  $F(w/s) = 2 \ln 2 s/[w G_7(w/s)]$ . For  $0 \le w \le (s/2)$ , F(w/s) lies between 1.0000 and 0.9974.

Smits [4] also calculated a factor, C, to correct eq (2) for measurements at the center of a circular specimen of finite diameter:

$$\rho = wC \frac{V}{I}$$

, (2b)

where C has the value  $\pi/\ln 2$  = 4.532 in the limit of infinite diameter.

The ASTM method for four-probe resistivity measurements on circular slices [1] assumes that correction factors F(w/s) and  $C^*$  can be combined multiplicatively provided that  $w \le s$  and the diameter,  $d \ge 10s$ :

$$\rho = wC F(w/s) \frac{V}{I}. \qquad (2c)$$

The factor C is designated  $F_2$  in ASTM Method F 84.

The method also provides other multiplicative correction factors to account for non-uniform probe spacing and for temperature variation of resistivity:

$$\rho = wC F(w/s) F_{sp}F_{T} \frac{V}{I}, \qquad (2d)$$

where in this case  $F_{\rm sp}=1+1.082[1-(s_2/s)]$ . Thus the regime  $s\le w\le 4s$  is not covered by either standard method. Since analytical determination of appropriate correction factors for thick specimens with small diameter appears to be intractable, an empirical study was carried out.

A 21-mm thick slice was cut from a 3-in. (76-mm) diameter p-type silicon crystal with a nominal room temperature resistivity of 10  $\Omega \cdot cm$ . Only the central 1.0-in. (25 mm) diameter region was used since the radial resistivity variation in the remainder of the slice was judged to be too great for use. The resistivity was measured at the center of the slice with a four-probe array with the standard [1] 1.59 mm probe spacing. The slice was fractioned and the resulting slices were repetitively thinned and remeasured at the center until the thickness was about 1 mm. Slices with thickness between about 5 mm and 1 mm were also measured with a probe with nominal 1.0 mm spacing. The results, expressed as the percent difference between resistivity calculated from measurements in the thinnest slices using eq (2d) and the resistivity calculated using either eq (2d) or (1a) as a function of slice thickness normalized by probe spacing, are plotted in figure 1.

Although some scatter would be expected since each of the measured V/I ratios has an uncertainty typified by a relative sample standard deviation of 0.3 to 0.5 percent, data from a given slice tended to be grouped along a well defined curve. It can be seen that if eq (2d) is used when w/s  $\leq$  2.5 and if eq (1a) is used when w/s  $\geq$  2.5, errors introduced by geometrical considerations are less than 2 percent provided the measurement is made at the center of the slice and provided that the diameter is at least 16 times the probe spacing. For larger diameter slices, smaller errors are expected.

(J. R. Ehrstein and D. R. Ricks)

#### 3.2. Spreading Resistance Methods

An extensive series of experiments was undertaken to determine the effect of specimen

Figure 1. Percent difference between calculated and actual resistivity as a function of the ratio of the thickness, w, of a 25-mm diameter slice to the probe spacing, s. (circles: s = 1.59 mm; squares: s = 1.02 mm; solid points: calculated from eq (la); open points: calculated from eq (2d).)

surface preparation and probe material on the empirical calibration between specimen resistivity and spreading resistance. These results are prerequisite to the investigation of the validity of using bulk silicon specimens to calibrate spreading resistance measurements on epitaxial silicon wafers.

In the present study specimens were cut from 1.5- to 2.0-in. (38- to 51-mm) diameter Czochralski-grown silicon crystals. Fifteen crystals each of n- and p-type silicon were grown in the [111] direction and twelve crystals of n-type silicon were grown in the [100] direction. Crystal orientation was specified to  $\pm 3$  deg and was not rechecked at NBS.

Slices 0.25-in. (6.3 mm) thick were cut perpendicular to the growth axis of each crystal to provide specimens with exposed (111) or (100) faces. Extra slices 0.12-in. (3.0-mm) thick were cut from seven [111] crystals of each type; these were used to provide specimens with exposed (110) faces by cutting along the diameter parallel to the orientation flat. The slices, except for those cut from three high resistivity [111] n-type crystals had a resistivity range not exceeding 5 percent between half radius points along a diameter. The resistivity was measured at

the center of each slice by the four-probe method (see sec. 3.1.); it was judged to be known to  $\pm 2$  percent except for the slices with excessive resistivity variation for which it was judged to be known to  $\pm 3$  percent. For each set of like orientation and conductivity type the resistivities were distributed relatively uniformly over the range  $10^{-3}$  to  $10^2$   $\Omega \cdot \text{cm}$ .

Rectangular parallelipipeds, 0.50-in. (12.7-mm) long and 0.25-in. (6.3 mm) thick, were cut from the central region of each slice along a diameter. The width of the oriented face varied from 1.3 to 3.0 mm depending on the number of slices in the set; the total width of all specimens in a set was about 20 mm. Sets of like orientation and conductivity type were mounted on a common block as shown in figure 2, with the oriented face upward and arranged so that the resistivity was a somewhat random function of position. The common mounting and partial randomization were to ensure that surface preparation would be as nearly identical for all specimens in a group and that there would be no systematic relationship between surface preparation and resistivity.

Six different surface preparations are being studied: lap with 5- $\mu m$  alumina, chemical polish with CP4 etch [6], chem-mechanical polish with slica sol [7], chem-mechanical polish with zirconium silicate [8], mechanical polish with 0.3- $\mu m$  alumina polish in aqueous slurry, and mechanical polish with 0.3- $\mu m$  alumina in a non-aqueous commercial thinner designed for diamond polishing. Measurements are being made with four probe ma-

Figure 2. Photograph of typical specimen block.

terials: tungsten-ruthenium alloy of nominal radius 0.75 mil (19  $\mu$ m) [9], tungsten carbide of nominal radius 1.0 mil (25  $\mu$ m) [10], osmium of nominal radius 1.0 mil (25  $\mu$ m) [11], and osmium-tungsten alloy of nominal radius 1.0 mil (25  $\mu$ m) [12]. Two sets of the last type of probes were used; one set was relatively blunt from extensive use while the other was new and freshly conditioned [13].

A commercial two-probe instrument which determines the logarithm of the ratio of the current through the probes to a current through a standard resistor, each driven by a constant, 10-mV source is being used to make the spreading resistance measurements. The probes, which are loaded with 45 g, are stepped across the composite blocks in a direction perpendicular to the long axis of the parallelepipeds at intervals of 250 µm. Measurements are being made on each block for each surface preparation with each of the five sets of probes. In addition, measurements are being repeated on all surfaces prepared with aqueous media (except CP4 etch) following a bakeout at about 160°C for 20 min in room air; this bakeout has been observed to greatly improve the spreading resistance measurements on p-type specimens with resistivity of 1  $\Omega$  cm or more [14].

The results obtained so far show no significant dependence of the form of the spreading resistance-resistivity ( $R_{\rm sp}$ - $\rho$ ) relation on probe material. This is illustrated in figure 3 which shows the results of measurements with the various probe tips on the (111) n-

Figure 3. Ratio of spreading resistance,  $R_{\rm Sp}$ , to resistivity,  $\rho$ , as a function of resistivity as measured with a variety of probe tips on a (111) n-type silicon surface chemmechanically polished with silica sol and baked out. ( $\bullet$ : blunt osmium-tungsten alloy;  $\bullet$ : tungsten carbide;  $\square$ : tungsten-ruthenium alloy;  $\bullet$ : osmium.)

#### RESISTIVITY

Figure 4. Ratio of spreading resistance,  $R_{\rm sp}$ , to resistivity,  $\rho$ , (logarithmic scale) as a function of resistivity as measured with freshly conditioned osmium-tungsten alloy probe tips on a variety of silicon surfaces chemmechanically polished with silica sol and baked out. ( $\bullet$ : (111) n-type;  $\blacktriangledown$ : (110) n-type;  $\bullet$ : (110) n-type; solid lines are least squares fits to the data with parameters as listed in table 2.)

type silicon surfaces chem-mechanically polished with silica sol and baked out. Differences in absolute value of the spreading resistance response can be seen; these appear to be primarily related to differences in effective contact radius of the various probe tips. However, statistically significant differences were observed between wafers of various surface orientation and conductivity type for all probe materials. Figure 4 and table 2 illustrate these differences for the case of measurements with the freshly conditioned osmium-tungsten alloy tip on surfaces chem-

Table 2 — Linear Regression Coefficients for Spreading Resistance Calibration Plots

| Surface<br>Orientation | Conductivity<br>Type | b <sup>a</sup> | s <sub>b</sub> <sup>a</sup> | mª     | s <sub>m</sub> a | Total<br>Data<br>Points | Excluded<br>Data<br>Points <sup>b</sup> |

|------------------------|----------------------|----------------|-----------------------------|--------|------------------|-------------------------|-----------------------------------------|

| (111)                  | р                    | 2.926          | 0.005                       | -0.020 | 0.004            | 15                      | 1-3,15                                  |

| (111)                  | n                    | 3.290          | 0.012                       | -0.011 | 0.009            | 15                      | 1,2                                     |

| (100)                  | n                    | 3.169          | 0.009                       | -0.032 | 0.008            | 12                      | none                                    |

| (110)                  | p                    | 2.872          | 0.013                       | -0.036 | 0.015            | 7                       | 1,2                                     |

| (110)                  | n                    | 3.316          | 0.023                       | -0.037 | 0.019            | 7                       | none                                    |

|                        |                      |                |                             |        |                  |                         |                                         |

$a \log(R_{sp}/\rho) = (b\pm s_b) + (m\pm s_m) \log \rho$

<sup>&</sup>lt;sup>b</sup>Data points (counting from leftmost point) excluded when  $R_{\rm sp}$  < 10  $\Omega$  (see text) except for point 15 for case of (111) p-type case which was apparently high because of incomplete post polish bakeout.

mechanically polished with silica sol and baked out. The calibration plots in the figure are presented as log  $R_{\mbox{sp}}/\rho$  against log  $\rho$ . As compared with the more usual log  $R_{\mbox{sp}}$  against log  $\rho$  plots, the present format emphasizes both deviations from linearity in a given plot and differences between plots made for different conditions.

Discrepancies in linearity of the R -p relationship for resistivities below 0.01  $\Omega \cdot cm$ are believed to be instrumental in nature. Shifts in the direction of high spreading resistance were observed for all probe-specimen combinations for which the measured spreading resistance was less than about 10  $\Omega$ . One cause may be an increase in series resistance due to spreading resistance into the probe material. Spreading resistances of 1.5 to 2.5 Ω have been measured for the probe materials under several conditions. If this is subtracted from the spreading resistance measured on silicon specimens, an otherwise linear relation is generally continued down to 0.001 Ω·cm. A second possible cause concerns the inability of the current source to operate in the constant voltage mode under the high current conditions associated with small résistive loads. T

The response on variously prepared (111) surfaces, both p- and n-type, is illustrated in figure 5 for the case of the freshly conditioned osmium-tungsten alloy tip. For p-type material, the response on the various surface preparations does not appear to be significantly different except that chemmechanically polished specimens with resistivity 0.5  $\Omega$ ·cm or more show large fluctuations unless baked out [14]. (The 60  $\Omega$ ·cm point on the baked out chem-mechanically polished surface is high because of an incomplete bake cycle and should be disregarded.)

For *n*-type material, the response on lapped surfaces is distinctly different from that on polished surfaces. On lapped surfaces, with or without bakeout, a strong peak in the ratio of R to  $\rho$  is observed for resistivities in the vicinity of 0.1  $\Omega \cdot \text{cm}$ ; the effect is more pronounced after bakeout. Polished surfaces

a. p-type.

b. n-type.

Figure 5. Ratio of spreading resistance,  $R_{\rm Sp}$ , to resistivity,  $\rho$ , as a function of resistivity as measured with freshly conditioned osmium-tungsten alloy probe tips on (111) p- and n-type silicon surfaces prepared in various ways. (circles: lapped with 5- $\mu$ m alumina; squares: chem-mechanically polished with silica sol; triangles: mechanically polished with 0.3  $\mu$ m alumina in non-aqueous thinner; solid points: not baked out; open points: baked out.)

The exact cause of the deviation from linearity at low specimen resistivity should have virtually no effect on the interpretation of measurements on bulk specimens having the same surface condition as the calibration specimens. However, interpretation of data on graded or multilayered structures may well be affected depending on the algorithm used, and certainly any detailed modeling of the spreading resistance phenomenon, such as inclusion of pressure dependent effects, will be influenced by an understanding of the dependence of measured spreading resistance upon resistivity.

Figure 6. Ratio of spreading resistance,  $R_{\rm Sp}$ , to resistivity,  $\rho$ , as a function of resistivity as measured with freshly conditioned osmium-tungsten alloy probe tips on n-type silicon surfaces showing extremes of behavior. (circles: (111) surface; triangles: (110) surface; squares: (100) surface; solid points: lapped with 5- $\mu$ m alumina and baked; open points: chem-mechanically polished with silica sol and baked.)

show a more nearly linear response than do the lapped surfaces; the response of surfaces chem-mechanically polished in aqueous media is not improved by bakeout.

Extremes of behavior for three orientations of n-type surfaces are illustrated in figure 6; the measurements reported were made with the freshly conditioned osmium-tungsten alloy tip. The most nearly linear response occurs on the chem-mechanically polished (100) surface; data shown were taken following bakeout but are essentially the same as data taken prior to bakeout.

Additional measurements to complete the matrix are underway; preferred surface preparation procedures can better be established following the conclusion of the experiment.

(J. R. Ehrstein and D. R. Ricks)

#### 3.3. High-Speed Spreading Resistance Probe

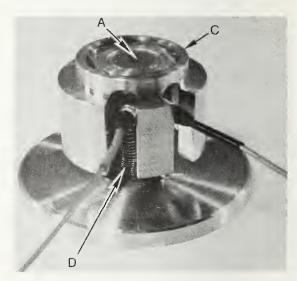

Additional tests were conducted with the prototype high-speed spreading resistance probe (NBS Spec. Publ. 400-19, pp. 10-13). The response of the instrument was found

to be excessively noisy under light load conditions which are best from the standpoint of probe wear. To correct this problem, hinged probe arm supports, pictured in figure 7, were designed and built. Results of measurements made with the previous holder suggest that the use of probe points with relatively large tip radius minimizes both noise and probe wear. The most suitable tips appear to be those with a large number of small, uniform micropoints; one way to achieve this condition is to dress the points with a stone of 6µm diamond in an epoxy matrix. Experience with osmium alloy and tungsten carbide probe points with tip radius from 1/4 to 6 mil (6 to 150 µm) showed that wear occurred principally as a result of breakage of micropoints (so that increasingly larger loading was necessary to maintain good electrical contact) or, under heavier loads, sheartype fracture of larger pieces (resulting in the formation of deeply gouged tracks). Small changes in the tip micropoint configuration do not appear to have more than a secondary effect on the relationship between spreading resistance and resistivity.

A compilation of the hardness of silicon and a variety of commercially available point materials is presented in table 3. It was found that the materials which are softer than silicon, hardened Inconel, steel, and tungsten, did not make good contact. The tracks were only faintly visible and the readings were very noisy. Points of all materials harder than silicon, tested to date, produced good track marks when the point tips were in good condition.

- A Probe tip

- B Arm

- C Hinge

- D Counterweight

- E Base

Figure 7. Hinged probe-arm assembly.

#### RESISTIVITY

Table 3 - Hardness of Probe Tip Materials

| Material Identification    | Constituents                     | Vickers Hardness <sup>a</sup> | Knopp Hardness |

|----------------------------|----------------------------------|-------------------------------|----------------|

| Inconel 718, hardened [15] | nickel-chromium-molybdenum-iron  | 530                           | 480            |

| Tungsten [11]              |                                  | 535                           | 490            |

| Carbon steel [11]          |                                  | 790-870                       | 730-750        |

| Silicon [11]               |                                  | 1150-1400                     | 900-1110       |

| Carballoy 55A [16]         | 87% tungsten carbide, 13% cobalt | 1180~1380                     | 1000-1200      |

| Carballoy 779 [16]         | 91% tungsten carbide, 9% cobalt  | 1300-1400                     | 1150-1250      |

| Osmium Alloy [11]          | osmium, tungsten, cobalt         | >1150                         | >1000          |

| Fidelitone K75 [9]         | tungsten-ruthenium               | 1650                          | 1500           |

| Carballoy 883 [16]         | 94% tungsten carbide, 6% cobalt  | 1650-1750                     | 1500-1600      |

| Carballoy 895 [16]         | 94% tungsten carbide, 6% cobalt  |                               | 2000           |

<sup>&</sup>lt;sup>a</sup>Hardness figures quoted are derived from a variety of sources and were obtained by using different methods. Therefore comparisons between various materials are not precise and the data given should be used only as a rough guide.

The instrument was shown to respond to various surface preparations in a manner similar to that previously found using a commercially available stepping-type instrument although the traces on the high-speed instrument were frequently somewhat noisier. For example, the effects of the strong inversion layer on air-dried chemmechanically polished p-type (111) surfaces were removed by baking in air at  $160^{\circ}$  to  $170^{\circ}$ C for 15 min while no such effect was observed on chem-mechanically polished n-type (100) surfaces. Beveled speci-

mens, prepared by high-speed diamond grinding [15] showed no distinct step in resistance when traversing from the original surface of the wafer onto the beveled surface. Repeated traces (slightly displaced) along the diameter of a heavily striated wafer, taken with an osmium alloy tip of 0.4-mil (10- $\mu$ m) radius loaded with 60 g, were able to resolve features 50 to 100  $\mu$ m in extent. It was possible to traverse a 3.0-in. (76-mm) diameter, taking a measurement every 250  $\mu$ m, in 5 min with a reset time of 3-1/3 min.

(A. Mayer and N. Goldsmith )

Work performed at RCA Laboratories under NBS Contract No. 5-35914. NBS contact for additional information: J. R. Ehrstein.

#### 4. PHYSICAL ANALYSIS METHODS

#### 4.1. Comparative Study of Surface Analysis Techniques

Several other aspects of the comparative study of surface analysis techniques (NBS Spec. Publ. 400-12, pp. 17-18) have been completed. The boron-implanted silicon specimen was profiled by secondary ion mass spectrometry (SIMS) using two different instruments, a direct imaging ion microscope and an ion microprobe. The specimen was a phosphorus-doped silicon wafer with room temperature resistivity in the range 5 to 10  $\Omega \cdot {\rm cm}$  and (100) surfaces. The 150-keV  $^{11}{\rm B}$  implant was misaligned by 7 deg with respect to the [100] direction to minimize channelling effects and then annealed at 1000°C in a non-oxidizing atmosphere for 1 h to electrically activate the boron.