# NBS SPECIAL PUBLICATION 400-12

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

# Semiconductor Measurement Technology

Quarterly Report July 1 to September 30, 1974

QC 100 157 .400-12 1975 1.2 The National Bureau of Standards<sup>1</sup> was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of a Center for Radiation Research, an Office of Measurement Services and the following divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Nuclear Sciences<sup>2</sup> — Applied Radiation<sup>2</sup> — Quantum Electronics<sup>3</sup> — Electromagnetics<sup>3</sup> — Time and Frequency<sup>3</sup> — Laboratory Astrophysics<sup>3</sup> — Cryogenics<sup>3</sup>.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry.

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services to promote the use of available technology and to facilitate technological innovation in industry and Government; cooperates with public and private organizations leading to the development of technological standards (including mandatory safety standards), codes and methods of test; and provides technical advice and services to Government agencies upon request. The Institute consists of a Center for Building Technology and the following divisions and offices:

Engineering and Product Standards — Weights and Measures — Invention and Innovation — Product Evaluation Technology — Electronic Technology — Technical Analysis — Measurement Engineering — Structures, Materials, and Life Safety <sup>4</sup> — Building Environment <sup>4</sup> — Technical Evaluation and Application <sup>4</sup> — Fire Technology.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical services designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the selection, acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the executive branch for the development of Federal standards for automatic data processing equipment, techniques, and computer languages. The Institute consists of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific information generated within NBS and other agencies of the Federal Government; promotes the development of the National Standard Reference Data System and a system of information analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate services to ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of the following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Library — Office of International Relations.

<sup>&</sup>lt;sup>1</sup>Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

<sup>&</sup>lt;sup>2</sup> Part of the Center for Radiation Research.

<sup>&</sup>lt;sup>3</sup> Located at Boulder, Colorado 80302.

<sup>\*</sup> Part of the Center for Building Technology.

# <sup>9</sup> 1975 Semiconductor Measurement Technology Quarterly Report, July 1 to September 30, 1974

W. Murray Bullis, Editor

10-12

S,

Electronic Technology Division Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234

Jointly Supported by: The National Bureau of Standards, The Defense Nuclear Agency, The Defense Advanced Research Projects Agency, and The Navy Strategic Systems Project Office

t'Special publication no. 400-12

#### U.S. DEPARTMENT OF COMMERCE NATIONAL BUREAU OF STANDARDS, Richard W. Roberts, Director

Issued May 1975

National Bureau of Standards Special Publication 400-12

Nat. Bur. Stand. (U.S.), Spec. Publ. 400-12, 59 pages (May 1975) CODEN: XNBSAV

> U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1975

For sale by the Superintendent of Documents, U.S. Government Printing Office, Washington, D.C. 20402 (Order by SD Catalog No. C13.10:400-12). Price \$1.15 cents (Add 25 percent additional for other than U.S. mailing).

## TABLE OF CONTENTS

#### SEMICONDUCTOR MEASUREMENT TECHNOLOGY

|                         |                                                      |   |     |     |   |   |   |   |   |   |   |   | PAGE                 |

|-------------------------|------------------------------------------------------|---|-----|-----|---|---|---|---|---|---|---|---|----------------------|

| Prefa                   | ce                                                   | • |     |     |   |   |   |   |   |   |   |   | vi                   |

| 1.                      | Introduction                                         |   | •   |     |   |   |   |   |   |   |   |   | 1                    |

|                         | Highlights                                           |   |     |     |   |   |   |   |   |   |   |   | 3                    |

| 3. 1<br>3.1.<br>3.2.    | Resistivity; Dopant Profiles                         |   | •   |     |   |   |   |   |   |   |   |   | 6<br>6<br>6          |

| 4.<br>4.1.<br>4.2.      | Crystal Defects and Contaminants                     | s | •   | ••• | • | • | • | • | • | • | • | • | 8<br>8<br>11         |

| 5. (<br>5.1.<br>5.2.    | Dxide Film Characterization                          |   | •   |     |   |   |   |   |   |   |   |   | 15<br>15<br>17       |

| 6. 2<br>6.1.<br>6.2.    | Test Patterns                                        |   | •   |     |   |   |   |   |   |   |   |   | 19<br>19<br>22       |

| 7. 1<br>7.1.<br>7.2.    | Epitaxial Layer Thickness                            |   | • • |     |   |   |   |   |   |   |   |   | 26<br>26<br>26       |

| 8. 1<br>8.1.<br>8.2.    | Vafer Inspection and Test                            |   |     | •   |   |   |   | • |   |   |   | • | 27<br>27<br>28       |

| 9. 2.<br>9.2.<br>9.3.   | Interconnection Bording                              | • | • • | •   | • | • | • | • | • | • | • | • | 29<br>29<br>30<br>31 |

| 10. 1<br>10.1.          | Hermeticity                                          |   |     |     |   |   |   |   |   |   |   |   | 33<br>33             |

| 11. 2<br>11.1.<br>11.2. | Chermal Properties of Devices                        |   |     | •   | • |   | • | • | • | • | • | • | 35<br>35<br>37       |

| 12. 1                   | References                                           | • | • • | •   | • | • | • | • | • | • | • | • | 41                   |

| Append                  | lix A. Semiconductor Technology Program Staff        | • | • • | •   | • | • | • | • | • | • | • | • | 44                   |

| Append                  | lix B. Semiconductor Technology Program Publications | • | • • | •   | • | • | • | • | • | • | • | • | 45                   |

| Append                  | lix C. Workshop and Symposium Schedule               | • | • • | •   | • | • | • | • | • | • | • | • | 47                   |

| Append                  | dix D. Standards Committee Activities                | • | • • | •   | • | • | • | • | • | • | • | • | 48                   |

| Append                  | lix E. Solid-State Technology & Fabrication Services | ٠ | • • | •   | • | • | • | • | • | • | • | • | 50                   |

| Index                   |                                                      | • | • • |     |   | • |   | • | • | • | • | • | 51                   |

### LIST OF FIGURES

PAG

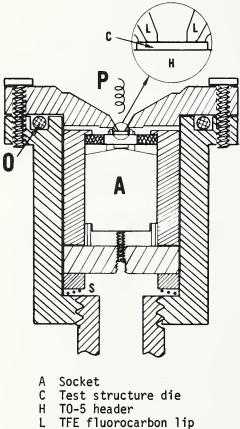

| 1.  | Cross sectional view of holder designed for the determination of dopant density profiles by the incremental sheet resistance method                                                                                                                        | 6       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

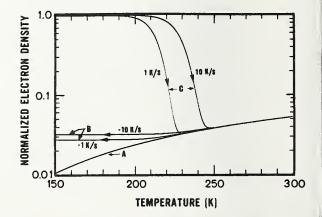

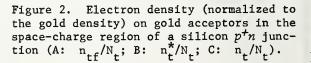

| 2.  | Electron density on gold acceptors in the space-charge region of a silicon $p^{+}n$ junction                                                                                                                                                               | 8       |

| 3.  | Schematic representation of the distribution of charge throughout the space-charge region of a $p^+n$ junction during the discharge of electrons from uniformly distributed acceptor defects                                                               | 9       |

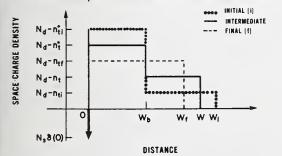

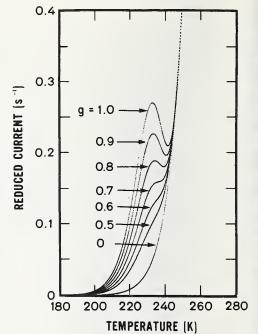

| 4.  | Calculated reduced thermally stimulated current, $I_1(p^+n)/qAW_0N_t$ , from gold acceptor defects in a silicon $p^+n$ junction as a function of temperature for $\beta = 10$ K/s, $W_b = 0$ , and several values of the ratio $N_d/N_t \dots \dots \dots$ | 10      |

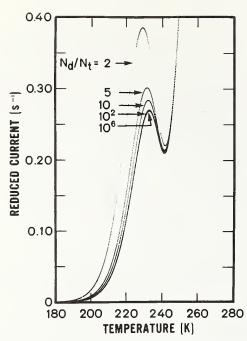

| 5.  | Calculated reduced thermally stimulated current, $I_1(p^+n)/qAW_0N_t$ , from gold acceptor defects in a silicon $p^+n$ junction as a function of temperature for $W_b = 0$ , $N_d/N_t = 100$ , and several values of $\beta$                               | 10      |

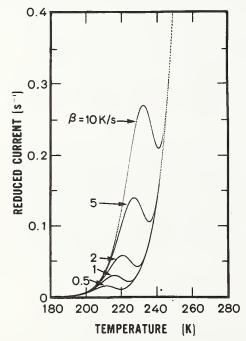

| 6.  | Calculated reduced thermally stimulated current, $I_2(p^+n)/qAW_0N_t$ , from gold acceptor defects in a silicon $p^+n$ junction as a function of temperature for $\beta = 10 \text{ K/s}$ , $N_d/N_t = 100$ , and several values of g                      | 10      |

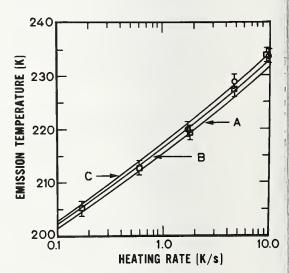

| 7.  | Emission temperature of the phase I current response of gold acceptor defects in $n$ -type silicon as a function of heating rate for various conditions                                                                                                    | :<br>10 |

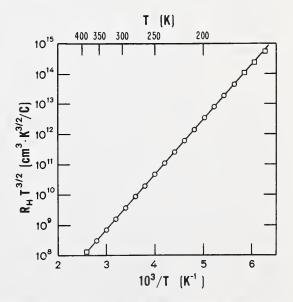

| 8.  | Hall effect activation energy plot for the gold donor in initially $n$ -type silicon converted to $p$ -type by diffusion with gold                                                                                                                         | 11      |

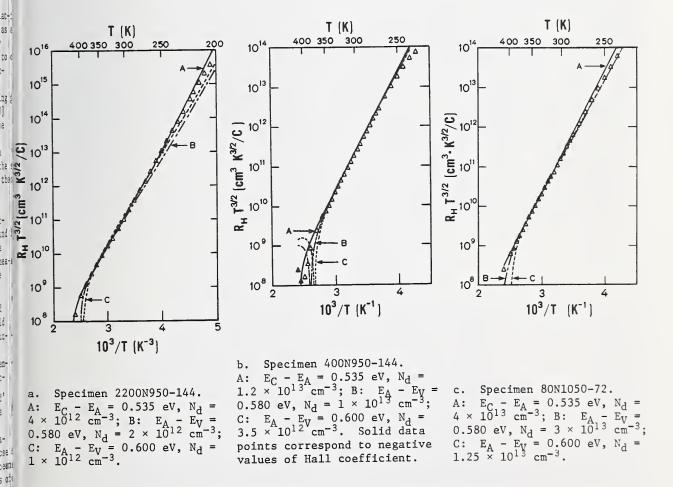

| 9.  | Experimental data and theoretical curves for determining the energy level of the gold acceptor in initially <i>n</i> -type silicon converted to <i>p</i> -type by diffusion with gold                                                                      | 13      |

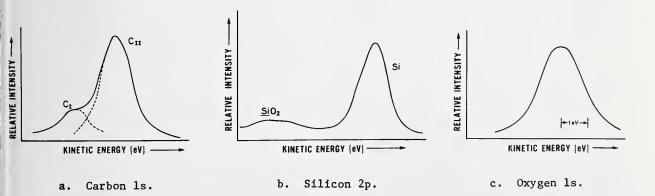

| 10. | X-ray photoelectron spectra of carbon, silicon, and oxygen from an air-stabilized silicon specimen                                                                                                                                                         | 15      |

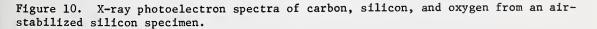

| 11. | Relative areas of x-ray photoelectron spectral peaks as a function of electron emission angle                                                                                                                                                              | 16      |

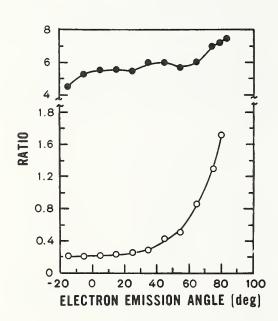

| 12. | Ratios of the relative areas of the x-ray photoelectron peaks due to carbon and silicon as a function of electron emission angle $\ldots$                                                                                                                  | 16      |

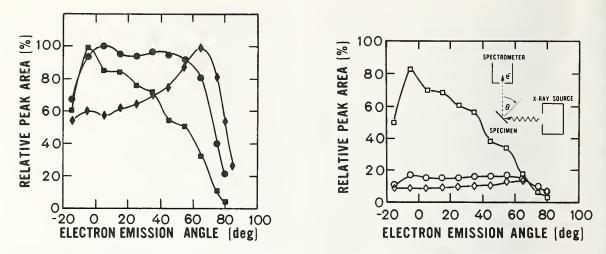

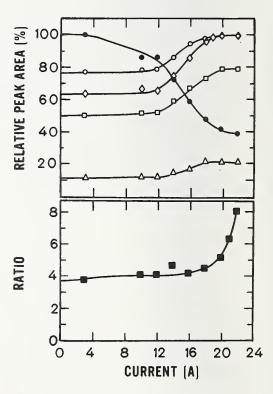

| 13. | Relative areas of x-ray photoelectron spectral peaks of cleaned silicon<br>surface heated in an ultralow pressure of oxygen as a function of heater<br>current and ratio of relative areas of the peaks due to carbon                                      | 16      |

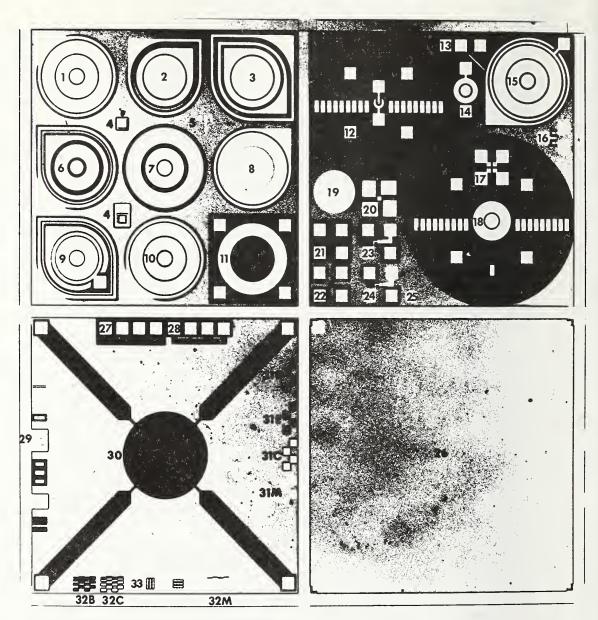

| 14. | Test pattern, NBS-3, for characterizing the resistivity-dopant density relation in silicon                                                                                                                                                                 | 20      |

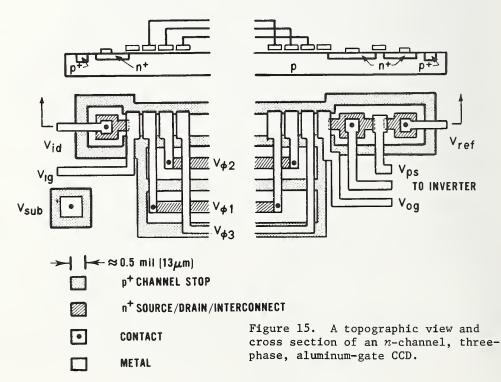

| 15. | A topographic view and cross section of an <i>n</i> -channel, three-phase, aluminum-gate CCD                                                                                                                                                               | 22      |

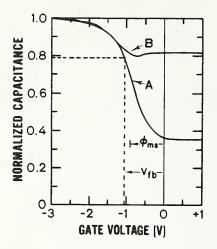

| 16. | High-frequency capacitance-voltage characteristics of a $p$ -MOS capacitor<br>and an $n$ -channel, 32-bit CCD connected as an MOS capacitor $\ldots$                                                                                                       | 24      |

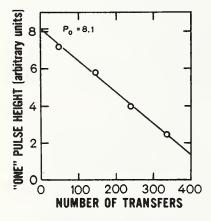

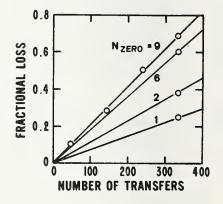

| 17. | Pulse height of a "one" preceded by 9 zeros as a function of the number<br>of transfers around a 32-bit circular CCD operating at 125 kHz                                                                                                                  | 24      |

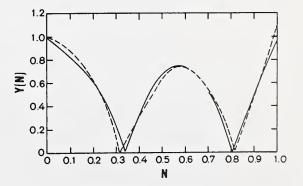

| 18. | Fractional charge loss per <b>tra</b> nsfer from a "one" preceded by N zeros<br>and transferred 336 times around a 32-bit circular CCD operating at 125 kHz                                                                                                | 24      |

| 19. | Fractional charge loss from a "one" preceded by N $_{\rm zero}$ zeros as a function of the number of transfers around a 32-bit circular CCD operating at 125 kHz $_{\rm .}$ .                                                                              | 24      |

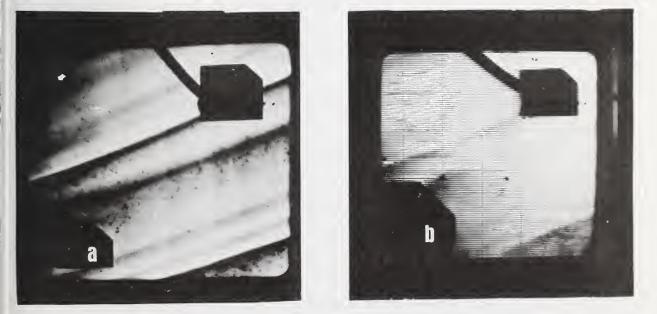

| 20. | Electron beam induced current response and unmodulated 0.633- $\mu$ m laser beam induced current response of a 0.76-mm square, unbiased, silicon $p-n$ junction diode                                                                                      | 27      |

#### LIST OF FIGURES

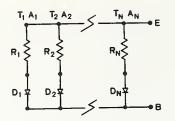

| 21. | Measured and calculated normalized vibration amplitudes of ultrasonic bonding tools mounted in inverted positions                                                                                                                                                                   | 29 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

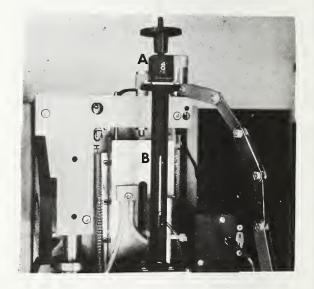

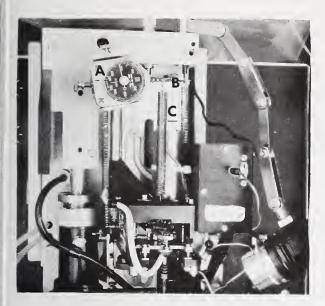

| 22. | Beam-lead force indicator as supplied with the beam-lead bonder                                                                                                                                                                                                                     | 30 |

| 23. | Modified beam-lead force gauge assembly                                                                                                                                                                                                                                             | 31 |

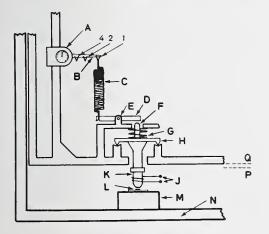

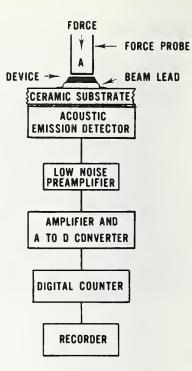

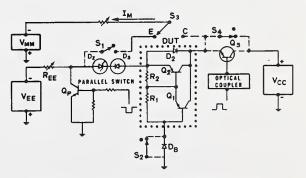

| 24. | Block diagram of acoustic emission test system                                                                                                                                                                                                                                      | 32 |

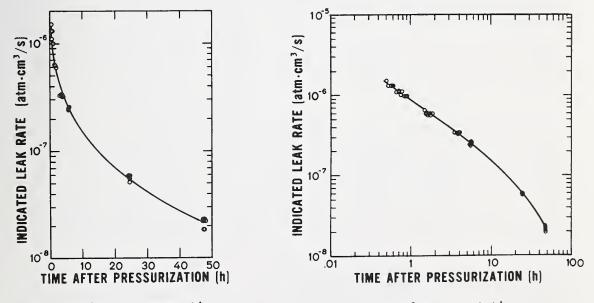

| 25. | Indicated leak rate for sealed-off borosilicate glass capsules of same<br>outer dimensions as test leak capsules as a function of time after pressuri-<br>zation at 75 psia for 20 h in helium                                                                                      | 33 |

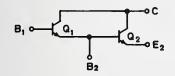

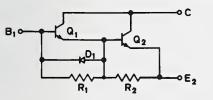

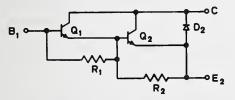

| 26. | Commercially available Darlington circuits                                                                                                                                                                                                                                          | 35 |

| 27. | Circuit diagram of emitter-only switching circuit for measuring thermal resistance modified to allow use of a variety of junction voltages as temperature sensitive parameters                                                                                                      | 35 |

| 28. | Model used for simulating the way in which the emitter-base voltage averages the junction temperature                                                                                                                                                                               | 38 |

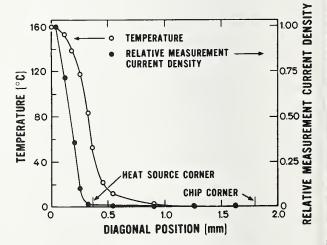

| 29. | Temperature and relative measurement current density along a diagonal of a 0.51-mm square heat source on a 2.54-mm square silicon chip                                                                                                                                              | 38 |

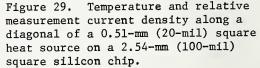

| 30. | The computed ratio of the average junction temperature to the peak<br>junction temperature as a function of heat source size for a 2.54-mm<br>square silicon chip corrected to account for the increased measurement<br>current density compared to the calibration current density | 39 |

|     |                                                                                                                                                                                                                                                                                     |    |

## LIST OF TABLES

|    |                                                                    | PAGE |

|----|--------------------------------------------------------------------|------|

| 1. | Properties of Gold-Doped Silicon Specimens                         | 13   |

| 2. | Specimens for the Comparative Study of Surface Analysis Techniques | 17   |

| 3. | Planar Test Structures on Test Pattern NBS-3                       | 21   |

| 4. | Epitaxial Layer Thickness by Three Methods                         | 26   |

| 5. | Bonding Tool Material Properties                                   | 30   |

| 6. | Thermal Resistance of a Type d Darlington Device                   | 36   |

| 7. | Peak Temperature Determination                                     | 39   |

v

The Semiconductor Technology Program serves to focus NBS efforts to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in specifying materials and devices in national and international commerce and for use by industry in controlling device fabrication processes. Its major thrusts are the development of carefully evaluated and well documented test procedures and associated technology and the dissemination of such information to the electronics community. Application of the output by industry will contribute to higher yields, lower cost, and higher reliability of semiconductor devices. The output provides a common basis for the purchase specifications of government agencies which will lead to greater economy in government procurement. In addition, improved measurement technology will provide a basis for controlled improvements in fabrication processes and in essential device characteristics.

The Program receives direct financial support principally from three major sponsors: the Defense Advanced Research Projects Agency (ARPA), the Defense Nuclear Agency (DNA), and the National Bureau of Standards (NBS). In addition, the Program receives support from the U.S. Navy Strategic Systems Project Office. The ARPA-supported portion of the Program, Advancement of Reliability, Processing, and Automation for Integrated Circuits with the National Bureau of Standards (ARPA/IC/NBS), addresses critical Defense Department problems in the yield, reliability, and availability of integrated circuits. The DNA-supported portion of the Program emphasizes aspects of the work which relate to radiation response of electron devices for use in military systems. There is considerable overlap between the interests of DNA and ARPA. Measurement oriented activity appropriate to the mission of NBS is a critical element in the achievement of the objectives of both other agencies.

Essential assistance to the Program is also received from the semiconductor industry through cooperative experiments and technical exchanges. NBS interacts with industrial users and suppliers of semiconductor devices through participation in standardizing organizations; through direct consultations with device and material suppliers, government agencies, and other users; and through periodically scheduled symposia and workshops. In addition, progress reports, such as this one, are regularly prepared for issuance in the NBS Special Publication 400 sub-series. More detailed reports such as state-of-the-art reviews, literature compilations, and summaries of technical efforts conducted within the Program are issued as these activities are completed. Reports of this type which are published by NBS also appear in the Special Publication 400 subseries. Announcements of availability of all publications in this sub-series are sent by the Government Printing Office to those who have requested this service. A request form for this purpose may be found at the end of this report.

Through ARPA Order 2397, Program Code 5D10 (NBS Cost Center 4259555).

<sup>&</sup>lt;sup>T</sup> Through Inter-Agency Cost Reimbursement Order 75-816 (NBS Cost Center 4259522).

Through Scientific and Technical Research Services Cost Centers 4251126, 4252128, and 4254115.

<sup>&</sup>lt;sup>3</sup> Code SP-23, Administered by Naval Ammunition Depot, Crane, Indiana, through project order N0016475P070030 (NBS Cost Center 4251533) and Code SP-27, through IPR SP6-75-4 (NBS Cost Center 4251547).

#### SEMICONDUCTOR MEASUREMENT TECHNOLOGY

QUARTERLY REPORT July 1 to September 30, 1974

Abstract: This quarterly progress report describes NBS activities directed toward the development of methods of measurement for semiconductor materials, process control, and devices. The emphasis is on silicon device technologies. Principal accomplishments during this reporting period include (1) completion of Hall effect measurements to determine activation energies of the gold donor and acceptor levels in silicon; (2) successful direct measurement of fast interface state density with the circular CCD test structure; and (3) demonstration of the feasibility of the use of acoustic emission as a non-destructive means for testing individual beam-lead bonds. Results are also reported on a holder for semi-automated sheet resistance measurements, progress on development of mathematical models of dopant profiles, analysis of thermally stimulated current and capacitance measurements on junction diodes, X-ray photoelectron spectroscopy, a comparative study of surface analysis techniques, design and fabrication of a test pattern for resistivity-dopant density evaluation, epitaxial layer thickness measurement; use of the flying-spot scanner, initial work on the scanning low energy electron probe, mathematical modeling of ultrasonic bonding, an improved method for force adjustment and measurement on beam-lead bonders, helium mass spectrometry for leak testing, thermal resistance measurements on Darlington pairs, and transistor thermal response measurements. Supplementary data concerning staff, publications, workshops and symposia, standards committee activities, and technical services are also included as appendices.

Key Words: Acoustic emission; beam-lead bonds; boron redistribution; Darlington pairs; dopant profiles; electrical properties; electronics; epitaxial layer thickness; flyingspot scanner; gold-doped silicon; hermeticity; incremental sheet resistance; measurement methods; microelectronics; micrometrology; MOS devices; oxide films; resistivity; scanning low energy electron probe; semiconductor devices; semiconductor materials; semiconductor process control; silicon; test patterns; thermal resistance; thermal response; thermally stimulated current; ultrasonic bonding; wire bonds; x-ray photoelectron spectroscopy.

#### 1. INTRODUCTION

This is a report to the sponsors of the Semiconductor Technology Program on work during the twenty-fifth quarter of the Program. It summarizes work on a wide variety of measurement methods for semiconductor materials, process control, and devices that are being studied at the National Bureau of Standards. The Program, which emphasizes silicon-based device technologies, is a continuing one, and the results and conclusions reported here are subject to modification and refinement.

1

The work of the Program is divided into a number of tasks, each directed toward the study of a particular material or device property or measurement technique. This report is subdivided according to these tasks. Highlights of activity during the quarter are given in section 2. Subsequent sections deal with each specific task area. References cited are listed in the final section of the report.

The report of each task includes a narrative description of progress made during this reporting period. Additional information concerning the material reported may be obtained directly from individual staff members identified with the task in the report. The organization of the Program staff and telephone numbers are listed in Appendix A.

Background material on the Program and individual tasks may be found in earlier quarterly reports as listed in Appendix B. From time to time, publications are prepared that describe some aspect of the program in greater detail. Current publications of this type are also listed in Appendix B. Reprints or copies of such publications are usually available on request to the author.

Communication with the electronics community

is a critical aspect both as input for guid ance in planning future program activities and in disseminating the results of the wor to potential users. Formal channels for such communication occur in the form of workshops and symposia sponsored or cosponsored by NBS. Currently scheduled semi nars and workshops are listed in Appendix C In addition, the availability of proceeding from past workshops and seminars is indicated in the appendix.

An important part of the work that frequent ly goes beyond the task structure is partic ipation in the activities of various techni cal standardizing committees. The list of personnel involved with this work given in Appendix D suggests the extent of this participation. In most cases, details of standardization efforts are reported in con nection with the work of a particular task.

Technical services in areas of competence are provided to other NBS activities and other government agencies as they are requested. Usually these are short-term, specialized services that cannot be obtained through normal commercial channels. To indicate the kinds of technology available to the Program, such services provided during the period covered by this report are listed in Appendix E. Particularly significant accomplishments during this reporting period include (1) completion of Hall effect measurements to determine activation energies of the gold donor and acceptor levels in silicon; (2) successful direct measurement of fast interface state density with the circular CCD test structure; and (3) demonstration of the feasibility of the use of acoustic emission as a non-destructive means for testing individual beam-lead bonds. Highlights of progress in these and other technical task areas are listed below.

<u>Resistivity; Dopant Profiles</u> — A plastic specimen holder was designed and fabricated to facilitate measurement of doping profiles by the incremental sheet resistance method. The holder is intended for semi-automated measurements on a van der Pauw resistor test structure to obtain data for use in the reevaluation of Irvin's curves which relate resistivity and dopant density for n- and ptype silicon. In addition, the development of mathematical models for dopant profiles, especially for the redistribution of boron during oxidation, has taken a more fruitful approach based on a finite difference algorithm.

<u>Crystal Defects and Contaminants</u> — Analysis of the thermally stimulated current and capacitance response of mid-gap acceptor-type

defects in a  $p^{+}n$  junction identified the heating rate, the ratio of donor density to defect density, and the spatial fraction of the space charge region in which the defects are initially charged as the three parameters which influence the shape of the dynathermal current response curve.

Activation energies of both the gold acceptor and gold donor were found from Hall effect measurements on initially n-type silicon wafers converted to p-type by the addition of gold. The more precise value found for the gold donor is in good agreement with the published values of others. To obtain an accurate value for the gold acceptor, it is necessary to determine the temperature variation of the energy of the acceptor level with respect to the band edges; this in turn requires improved formulas for calculating carrier mobilities in the presence of charged impurity centers. These are being sought in connection with the reevaluation of Irvin's curves, discussed previously; further work on the energy level model for gold will be deferred so that the mobility problem can be attacked.

Oxide Film Characterization — Study of xray photoelectron spectra from the surface of air-stabilized silicon demonstrated the usefulness of the angular dependence of the intensity of spectral peaks in qualitatively locating the depth of surface impurities and determining the thickness of surface films. Other experiments on low-carbon silicon suggested that the previously observed carbon film arises from external sources and not from the surface or bulk of the silicon.

A series of measurements was initiated to compare various electron, ion, and photon beam measurement technologies for determination of impurities in silicon and silicon dioxide. In these preliminary measurements, ion implanted specimens are being used to provide a reasonably well known density of impurity at a reasonably well defined location. Boron and zinc implanted silicon and aluminum and sodium implanted silicon dioxide are being measured by ion microprobe mass analysis, ion scattering mass analysis, Auger electron spectroscopy, and other techniques in laboratories associated with the manufacturer of an instrument or in laboratories associated with semiconductor analysis or device production.

The fourth ARPA/NBS Workshop on Surface Analysis for Silicon Devices is being organized to determine the present qualitative and quantitative capabilities and future prospects of modern analytical beam techniques as applied to the analysis of silicon, and associated insulator films and device structures. Of particular interest are determinations of impurity profiles, surface contamination, and interface characteristics. Techniques utilizing impinging electron, ion, neutral, or photon beams will be considered. The workshop, scheduled for April 23 and 24 at NBS, Gaithersburg, is intended to foster discussions among analysts, users of their results, and instrument manufacturers.

<u>Test Patterns</u> — Test patterns were the subject of the third ARPA/NBS Workshop held in Scottsdale following the September meeting of ASTM Committee F-1 on Electronics. About 70 scientists and engineers, representing 38 organizations, attended the workshop. Seven speakers from industry and government addressed various aspects of test pattern analysis and use. The Workshop was particularly

#### HIGHLIGHTS

significant in disclosing the value of test patterns in manufacturing for rapid start up of new processes and control of ongoing processes and, in the market place, for evaluation of incoming materials for processing, for device-vendor intercomparisons, and for device specifications. There was general agreement that full utilization of test patterns will require both increased understanding of the interpretation of the measurement results and improved data acquisition, analysis, and display systems.

An initial fabrication run of the new test pattern, NBS-3, was completed. Preliminary experiments were conducted on the collector resistor and incremental sheet resistance (van der Pauw) test structures.

The CCD test pattern being developed by the Naval Electronics Laboratory Center with ARPA funding has been fabricated and the correlation of its test structures begun. The CCD can be connected and satisfactorily operated as an MOS capacitor, but some extraneous capacitance is observed in the inversion region of the CCD C-V characteristics. Threshold voltages and channel mobilities of the CCD structure connected as an MOS transistor agree reasonably well with those of an ordinary MOS transistor. Most importantly, the effectiveness of the circular CCD structure was demonstrated in connection with the direct determination of interface state density by the double-pulse method because the number of transfers is

A computer-controlled data acquisition and

analysis system was received from the vendor in July. Following preliminary checkout and familiarization tests, the system was set up together with an automatic wafer prober to obtain real time wafer maps of base sheet resistance using the appropriate test structure on test pattern NBS-2. In addition the system has been used to acquire capacitance-voltage (C-V) data from a gated p-n junction and calculate and plot the dopant density profile employing peripheral and diffused layer corrections; acquire C-V data from an MOS capacitor and calculate dopant density, flat-band voltage, and oxide charge density; and generate a curve of capacitance as a function of time for an MOS capacitor fabricated on an epitaxial specimen, fit the portions of the curve which represent relaxation in the substrate and relaxation in the epitaxial layer, and calculate the layer thickness from the intersection of the two fits.

Photolithography --- Work in the task which has been initiated to develop procedures for primary line width measurement calibrations, to provide calibrated line width measurement artifacts for use with optical microscopes, and to develop improved theory and experimental verification for accurate measurements with optical systems is currently being concentrated on construction of essential measurement equipment. A two directional interferometer is being designed and built for use in improving the line center to line center distance measurement between two parallel lines. A modified Bennett polarizing interferometer, which measures the movement of a mirror mounted on the stage of a scanning electron microscope (SEM) relative to a fiducial mirror by measuring the angle of polarization of the light produced by the relative movement of the two mirrors is being constructed for prototype in situ measurements. In addition, measurements are being made both on a gold-nickel thin-line laminate designed for use in calibrating the magnification of an SEM and on commercially produced patterns of chromium lines on glass with both filar and w image shearing attachments to a conventional microscope. This task was undertaken in response to particularly strong statements which have been received from the integrated circuits industry emphasizing the critical need for the development of NBS line width standards in the 1 µm range to assist the

The system is built around an oscilloscope in which the displayed waveform can be divided into 512 channels in the horizontal direction. In an associated memory each channel is represented by a 10-bit word which, together with the scale factor information for the oscilloscope input, defines the amplitude of the signal within that channel. Each 10-bit word can be stored in 6.5 µs, so that a waveform composed of 512 data points can be stored in less than 3.5 ms. An associated minicomputer, which has a 24,000 bit memory and computes with four significant figures, is able to process the stored waveforms as necessary. BASIC commands are available to activate and control programmable voltage and current supplies. A digital temperature indicator can also be interfaced with the system. Peripheral equipment includes a CRT display terminal, a hard copy unit which can copy whatever is displayed on the CRT, and a paper tape reader/punch.

industry in meeting the micrometrology requirements associated with high resolution photomasks.

The state-of-the-art review of available technologies for automated photomask inspection was completed [1], and detailed analyses of the identified specific technologies identified were begun.

Epitaxial Layer Thickness — Cleave-andstain measurements were made of thickness of several epitaxial layers previously measured by the step-relaxation method. The agreement, although somewhat better than achieved between other methods and the steprelaxation method, was not fully satisfactory. A technique was developed for making aluminum-photoresist-silicon capacitors for use with the step-relaxation and rampvoltage methods. These capacitors are made without subjecting the specimen to high temperature processing steps.

Wafer Inspection and Test -- The characteristics of the laser flying spot scanner were measured and preliminary scans were made on a group of devices which were also investigated in the scanning electron microscope operating in the electron beam induced current mode. A survey was initiated to determine the state of activity within the semiconductor device industry in the areas of application of laser scanning for wafer testing and other purposes, application of the SEM to topological inspection and electrical testing of silicon wafers, and study of SEM-induced damage during inspection or test in order to establish directions of future NBS work in these areas.

Work was begun at the Naval Research Laboratory on the development of an automated scanning low energy electron probe as a noncontacting non-damaging wafer test technique; this work was initiated with the design and construction of the electron gun and initiation of procurement of the control computer.

Interconnection Bonding — Experimental verification of the uniform beam model for analysis of the vibration of an ultrasonic bonding tool continued with study of tools mounted in an inverted position so that the cross section of the vibrating portion was uniform.

An improved mechanism was designed and constructed to measure and control the force applied during beam-lead bonding. Initial studies of a non-destructive acoustic emission test to determine the bond quality of beam-lead, flip-chip, or other gang bonded devices demonstrated the feasibility of this approach. Well bonded beamlead devices gave little or no noise while devices with one or two beams bonded to areas rendered intentionally defective gave noise bursts at applied test forces low enough not to deform the beams.

Two new bond test methods based on work carried out at NBS, a hot-melt-glue destructive pull test for beam-lead bonds and a nondestructive wire bond pull test, were prepared for ASTM Committee F-1 on Electronics. An intercomparison of the double-bond destructive pull test between NBS and another laboratory was conducted in preparation for a complete interlaboratory evaluation of this method.

<u>Hermeticity</u> — Progress in conducting the interlaboratory evaluation of the helium mass spectrometer method for leak testing semiconductor devices and integrated circuits was delayed by difficulties encountered in the back pressurization phase. These difficulties were traced to outgassing of helium which diffused into the glass walls of the test leaks during pressurization and procedures for reducing this effect were developed.

The interlaboratory evaluation of the radioisotope method for leak testing semiconductor devices is proceeding as scheduled.

Thermal Properties of Devices — A modified emitter-only-switching thermal resistance test circuit was successfully used to separate thermal effects of the input and output transistors of a monolithic Darlington circuit. This simple two-transistor circuit is an elemental integrated circuit in that leads to all regions of each device are not available at the exterior terminals so that it is not possible to measure all desired junction voltages independently; hence localization of effects to a particular device must be inferred from the results of several measurements made under different conditions.

A method was developed for estimating peak junction temperature from the electrically generated heating and cooling response of medium power transistors. Results obtained on several transistors showed good agreement with peak junction temperatures measured by an infrared microradiometer.

#### 3.1. Incremental Sheet Resistance

A specimen holder was fabricated to facilitate the measurement of dopant profiles by the incremental sheet resistance method [2]. It was designed so that the repeated sequence of anodic oxidation, oxide stripping with hydrofluoric acid, and sheet resistance measurement can be done without removing the specimen from the holder. A cross sectional view of the holder, which is an adaptation of existing designs [3,4], is shown in figure 1. The critical aspect of the design and fabrication is the achievement of a liquid-tight seal around the area to be anodized. In the apparatus shown the seal is made by pressing the specimen against a TFE fluorocarbon lip (L) by means of pressure applied by a spring (S) in the bottom of the

- 0 0-ring seal

- P Platinum cathode

- S Spring

Figure 1. Cross sectional view of holder designed for the determination of dopant density profiles by the incremental sheet resistance method. holder. The holder is intended for use with test structure 30 of Test Pattern NBS-3 (see sec. 6.1.). This structure is a van der Pauw [5] sheet resistor with a diameter of 0.76 mm and symmetrically placed contact arms which extend to contact pads at each corner of the square chip, 2.54 mm (100 mil) on a side. The test structure die (C) is mounted on a TO-5 header (H), which is placed in the holder beneath a 1.25 mm diameter opening in the lip. The 0.4 mm wide seal between the lip and the die protects the contact pads, the bonded lead wires which connect the pads to posts on the header, and the header from the electrolyte used for anodic oxidation.

In the course of overcoming various design and fabrication difficulties, certain precautions became evident. One is the importance of precisely machining the sealing lip to obtain a smooth, scratch-free surface and then handling the piece carefully so that it does not acquire scratches and dents during use. To aid in putting the holder together without damaging the sealing lip, it has been extremely helpful to use a ring around the holder to center the top piece as it makes contact with the bottom section.

All external parts of the holder are made of TFE fluorocarbon so that the entire apparatus may be immersed in the electrolyte. Alternatively, the electrolyte acid can be confined to the top reservoir. For removal of the oxide layer, hydrofluoric acid can be poured into the reservoir only. There is a tendency for an air bubble to be trapped just above the specimen when liquids are introduced into the reservoir so it is often necessary to use a small brush to clear away the bubble. Not shown in figure 1 are the wires going to the socket (A) and the plastic tubing and elbows through which the wires run. The holder can be varied for use in either a vertical or horizontal position by appropriate elbow and tubing changes. The apparatus has been tested numerous times with an ethylene glycol mixture as the electrolyte and found to be adequate. However, much more experience in actual profiling is needed before the design can be considered to be fully satisfactory.

(W. R. Thurber and L. M. Smith)

#### 3.2. Mathematical Models of Dopant Profiles

Work continued in the project to develop a mathematical model which can be solved for

the redistribution of boron in silicon during thermal oxidation and diffusion. A computational scheme described previously (NBS Spec. Publ. 400-8, p. 14) was based on the numerical solution of a system of integral equations (NBS Spec. Publ. 400-4, pp. 9-11). Study of this scheme has revealed the need to add several additional quadrature subroutines in order to resolve various numerical difficulties. Since the program is already long and complex and hence very difficult to check, work was shifted to a shorter and more promising finite difference algorithm. Using this algorithm [6], a computer program has been written for the moving boundary value problem (NBS Spec. Publ. 400-1, pp. 9-11). In order to solve the two diffusion equations, one in the oxide and one in the silicon, and to satisfy the segregation and conservation of mass boundary conditions, the double sweep method [7] was used. Results of several computer runs are being studied with regard to their convergence to the closed form solution of Grove *et al.* [8]. (S. R. Kraft\* and M. G. Buehler)

NBS Mathematical Analysis Section, Applied Mathematics Division.

#### 4.1. Thermally Stimulated Current and Capacitance Measurements

Analysis of thermally stimulated current and capacitance measurements continued with emphasis on the thermally stimulated current response of mid-gap acceptor-type defects in

a  $p^{\neq}n$  junction. The parameters which influence the response of a particular defect center have been identified as the heating rate,  $\beta$ ; the ratio of the donor density to the defect density,  $N_d/N_t$ ; and the spatial

fraction of the space-charge region over which defects are initially charged, g.

Recall that the experiment is conducted by cooling the junction to a low temperature with a small bias which corresponds to a space-charge width  $W_b$ , then reverse biasing the junction to increase the space-charge

width to  $W_i$ , and then observing the current as the junction is warmed up [9]. The temperature dependence of the electron density on the defects in the space-charge regions can be found by solving numerically eqs (7a) and (7c) of reference [9]. As an example consider the gold acceptor in silicon for which the electron and hole emission rates, in inverse seconds, are [10]

$$e_{1} = 1.97 \times 10^{7} T^{2} exp(-6348/T)$$

and

$$e_{p} = 5.82 \times 10^{6} T^{2} exp(-6847/T),$$

respectively, where T is the absolute temperature in kelvin. The results are illustrated in figure 2 and discussed in the following paragraphs.

In equilibrium, the electron and hole emission rates govern the electron density on the defects in the space-charge region according to the relation

$$n_{tf} = e_p N_t / (e_n + e_p)$$

where  $n_{tf}$  is the isothermal, steady-state electron density. The ratio  $n_{tf}^{N_t}$  is the lowest curve in the figure. If the spacecharge region is cooled from high temperatures at a finite rate, the actual electron density,  $n_t^*$ , will be larger than  $n_{tf}$  as depicted in the figure for two typical cooling rates. Nevertheless, electrons occupy only a very small fraction of the defects and in this portion of the space-charge region, the defects are essentially uncharged. Once cooled to the desired temperature,  $n_t^*(=n_{ti}^*)$

remains essentially unchanged until the warm up period is begun.

In the neutral region, essentially all the defects are occupied by electrons since the Fermi energy is well above the defect energy. When the space-charge region is increased from  $W_b$  to  $W_i$  at low temperature the electron density on the defect centers in this portion,  $n_t$ , does not change, so the defects are initially essentially fully charged  $(n_{ti} \approx N_t)$ .

The initial distribution of charge in both portions of the space-charge region is shown by the dotted line in figure 3. During warm up the electron density on the defects in the initially uncharged portion between 0 and  $W_b$ ,  $n_t^*$ , follows the appropriate cooldown curve (see fig. 2) until it reaches the value  $n_{tf}$ . The electron density in the initially charged portion between  $W_b$  and  $W_i$ ,  $n_t$ , remains essentially constant until it begins to fall rapidly toward the value  $n_{tf}$ at a temperature which depends on the heating rate as shown by the upper curves in

figure 2. Referring to figure 3, the charge distribution in the space-charge region (which contracts as the defects discharge) shown by the solid line is for an intermediate temperature where  $n_t$  is changing rapid-

ly, and the final distribution occurs at high temperature where  $n_t^* = n_t = n_{tf}^*$ .

During the discharging of the defects there is a reverse current from the space-charge region which is composed of two parts, namely, the conduction current and the displacement current [11]. For a constant applied bias during warm up and for uniformly distributed defect centers, the current is

$$I(p^{+}n) = \frac{qA}{2W} [\dot{n}_{t}(W - W_{b})^{2} + \dot{n}_{t}^{*}(2WW_{b} - W_{b}^{2}) - e_{p}p_{t}^{*}2WW_{b} - e_{p}p_{t}^{2}W(W - W_{b})]$$

(1)

where  $n_t = e_p p_t - e_n t$ ,  $n_t^* = e_p p_t - e_n t$ ,  $p_t^* = N_t - n_t$ ,  $p_t = N_t - n_t$ , q is the electronic charge, W is the space charge width, and A is the junction area. The sum of the applied and built-in junction voltages is related to the width of the space-charge region and the charge densities by the relation

$$V_{T}(p^{+}n) = \frac{q}{2\varepsilon_{s}} [(N_{d} - n_{t}^{*}) W_{b}^{2} + (N_{d} - n_{t})(W^{2} - W_{b}^{2})], \qquad (2)$$

p<sup>+</sup>- SILICON n - SILICON WITH ACCEPTOR DEFECTS

Figure 3. Schematic representation of the distribution of charge throughout the spacecharge region of a  $p^+n$  junction during the discharge of electrons from uniformly distributed acceptor defects. where  $\varepsilon_{s}$  is the dielectric constant of silicon. These equations are applicable to both isothermal and dynathermal measurements [8].

Two limiting cases lead to simplified expressions for the current. First consider that all defects in the space-charge region are charged; that is,  $W_{b} = 0$ . In this case a reduced form of eq (1) is

$$\frac{I_{1}(p^{+}n)}{I_{A}W_{o}N_{t}} = -\frac{e_{n}n_{t} + e_{p}p_{t}}{2N_{t}} \left(1 - \frac{n_{t}}{N_{t}}\frac{N_{t}}{N_{d}}\right)^{-1/2}$$

(3)

where  $W_o = (2\epsilon_s V_T/qN_d)^{1/2}$  and the reduced current is in inverse seconds. Plots of reduced current as a function of temperature for several values of the ratio  $N_d/N_t$ , shown

in figure 4, demonstrate that the temperature of the current peak is only weakly dependent on this ratio. The small shift which occurs for small values of the ratio is related to the contraction of the spacecharge region as the defect centers discharge. When  $N_d >> N_t$ , the motion of the

edge of the space-charge region during discharge is not significant and the current response is insensitive to the exact value of the ratio  $N_d/N_t$ . Plots of reduced current for various heating rates, shown in

figure 5, demonstrate that the temperature of the current peak shifts toward higher temperatures for faster heating rates. The heating rate is the most significant parameter to affect the temperature of the current peak.

The second case, which occurs for  $N_d >> N_t$ , facilitates study of the effect of charging the defects only in a portion of the spacecharge region. In this case, one finds from eq (2) that  $W = W_o$ , a constant, consistent with the lack of motion of the edge of the space-charge region during discharge of the defects, and that  $g = (W_o - W_b)/W_o$ . With these substitutions in eq (1), the reduced current becomes

$$\frac{I_2(p^+n)}{qAW_0N_t} = \frac{-1}{2N_t} \left[ e_n n_t^* (1 - g^2) + e_p p_t^* (1 - g)^2 + e_n n_t g^2 + e_p p_t (2g - g^2) \right].$$

(4)

Plots of this reduced current are shown in

#### CRYSTAL DEFECTS AND CONTAMINANTS

Figure 4. Calculated reduced thermally stimulated current,  $I_1(p^+n)/qAW N_t$ , from gold acceptor defects in a silicon  $p^+n$  junction as a function of temperature for  $\beta = 10 \text{ K/s}$ ,  $W_t = 0$ , and several values of the ratio  $N_d/N_t$ . [See eq (3).]

Figure 5. Calculated reduced thermally stimulated current,  $I_1(p^+n)/qAW N_t$ , from gold acceptor defects in a silicon  $p^+n$  junction as a function of temperature for  $W_t = 0$ ,  $N_d/N_t = 100$ , and several values of  $\beta^b$ . [See eqt (3).]

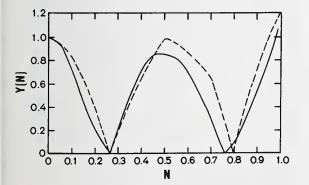

Figure 6. Calculated reduced thermally stimulated current,  $I_2(p^+n)/qAWN$ , from gold acceptor defects in a silicon  $p^+n$  junction as a function of temperature for  $\beta = 10 \text{ K/s}$ ,  $N_d/N_t = 100$ , and several values of g.

Figure 7. Emission temperature of the phase I current response of gold acceptor defects in *n*-type silicon as a function of heating rate for various conditions. [Calculated: A:  $N_d/N_t = 5$ , g = 1; B:  $N_d/N_t = 100$ , g =1; C:  $^dN_d/N_t = 100$ , g = 0.8. Experimental: O:  $p^+n^d$  junction (Device 2107.1,  $N_d/N_t = 45$ g = 0.803);  $\Box$ : *n*-MOS capacitor (Device 2107.7,  $N_d/N_t = 25$ , g = 0.833).]

figure 6 for various values of g. The significance of this figure lies in the possibility of confusion when identifying defects according to the shape of the current response. One must be aware that this shape is intrinsically tied to the value of g. It should be noted that it is not possible in practice to achieve g = 1 ( $W_b = 0$ ) for this

requires that junctions be heavily forward biased. This in turn results in significant injection of minority carriers and attendant alteration of the initial values of  $n_t$  and  $*_{t}n_{t}$ .

The results presented in figures 4, 5, and 6 are summarized in figure 7 in which the emission temperature, the temperature at which the peak of the current occurs during warm up, is plotted against heating rate for several conditions. Experimental values are

also shown for both a gold doped  $p^{+}n$  junction (NBS Tech. Note 806, p. 15) and an *n*-MOS capacitor (NBS Spec. Publ. 400-1, p. 17). This model for the current response of

a  $p^{\dagger}n$  junction is also applicable to the phase I response of an *n*-MOS capacitor (NBS Spec. Publ. 400-1, pp. 16-19) provided that  $g \neq 0$ . A thorough discussion of the *n*-MOS capacitor current response will be presented at a later date.

(W. E. Phillips and M. G. Buehler)

#### 4.2. Energy Level Model for Gold in Silicon

The Hall effect measurement phase of a continuing effort to obtain parameters for an energy level model for gold in silicon [12] was concluded with the determination of activation energies of the gold donor and gold acceptor from measurements of the Hall coefficient as a function of temperature on initially phosphorus-doped specimens diffused with sufficient gold to convert the conductivity type from n to p. Depending on the amount of gold added, either the gold donor level or gold acceptor level will dominate [13]. If the gold density greatly exceeds the phosphorus density, gold-coupled shallow acceptors are introduced (NBS Tech. Note 788, pp. 18-24) and the gold donor level dominates. The gold acceptor level dominates when the gold density exceeds the phosphorus density by a smaller amount so that there is weak p-type conduction. Consequently the specimens for which the deep acceptor level can be observed are nearly intrinsic and the activation energy cannot be accurately determined from the slope of

a plot of  $R_H^{T^{3/2}}$  against 1/T. Instead it is necessary to use a two carrier analysis to fit the Hall effect data as a function of temperature and arrive at an activation energy based on the fit of the calculated curves to the experimental data.

The gold donor was studied on wafer 80N1250-8 which was processed from a 1.1 mm thick wafer with an initial room temperature resistivity of 75  $\Omega$ ·cm. Gold was evaporated on both sides of the silicon wafer and diffused at 1250°C for 8 h; then both wafer faces were lapped to a depth of 125 µm to remove excess surface gold before ultrasonically cutting a six-contact bridge-type specimen [14] for Hall effect and resistivity measurements. After diffusion, the room temperature resistivity was  $1.7 \times 10^3 \, \Omega \cdot cm$ and the conductivity type had changed from nto p. A gold density of 1.05  $\times$  10<sup>17</sup> cm<sup>-3</sup> was determined by neutron activation analysis on a specimen from the same wafer as the Hall bar.

The activation energy of the gold donor was computed from the data shown in figure 8 by means of a least squares analysis [15] for the slope. The data points included in the analysis are shown by circles; the points excluded because of their deviation from linearity are shown as squares. The calculated energy of  $0.3616 \pm .0002$  eV represents

Figure 8. Hall effect activation energy plot for the gold donor in initially *n*-type silicon converted to *p*-type by diffusion with gold. (Specimen 80N1250-8.)

the value at zero kelvin of the energy difference between the valence band edge and the gold donor level with the assumption that this difference is a linear function of temperature. The uncertainty in the energy is the square root of the estimated variance of the slope and does not take into account systematic errors which might be present. The energy difference obtained from this specimen of initially phosphorus-doped silicon is in excellent agreement with an average activation energy of 0.3617  $\pm$  0.0011 eV measured previously on four initially borondoped specimens diffused with gold (NBS Tech. Note 754, pp. 14-15).

In obtaining the above values, the Hall coefficient, R<sub>u</sub>, was multiplied by the threehalves power of the absolute temperature, T, to correct for the principal temperature dependence of the density of states. However the hole effective mass,  $m_h^*$ , is also temperature dependent and consequently this affects the values obtained for the activation energy. To account for the temperature dependence of  $m_h^{\star},$  the quantity  $R_{H}^{} T^{3/2}$  was multiplied by  $(m_h^*)^{3/2}$  using a polynomial equation for  $m_h^*$  which was derived previously (NBS Spec. Publ. 400-4, pp. 15-23). With this correction a value for the activation energy of 0.3555 ± .0002 eV was calculated for the set of points shown in figure 8. The values previously reported for borondoped silicon would also be reduced by the same amount when the temperature dependence of  $m_b^*$  is included in the analysis.

A second small correction is required to account for the temperature dependence of the scattering factor, which relates the Hall coefficient to the carrier density. If this factor is assumed to vary as  $T^{-0.21}$ , as reported for high purity silicon [16], the value of the activation energy is further reduced to 0.3511 ± 0.0002 eV.

The more precise energy level value for the gold donor from this work is in good agreement with both the early results of Collins *et al.* [13] and the more recent data of Brückner [17]. It is reasonable to conclude that the activation energy for this level is well known and a good value is available for use in a model.

The gold acceptor was studied on three 1.1-mm thick wafers with properties listed

in table 1. Except for the time and temper ature of the gold diffusion, the procedure followed in preparing these specimens was the same as that described above. The results of the Hall measurements on these specimens are plotted in figure 9.

Theoretical curves of  $R_{\rm H}T^{3/2}$  as a function

of reciprocal temperature were generated fo three values of the gold acceptor level for each of the three specimens using the charge-balance equation and a model for the energy levels in gold-doped silicon as discussed previously (NBS Tech. Note 788, pp. 18-24) but changes were made in the values of some of the parameters. For the temperature dependence of the energy band gap,  $E_c - E_v$ , the electron effective mass, m, and the hole effective mass, m, the poly-

nomial fits published earlier (NBS Spec. Publ. 400-4, pp. 15-23) were used. The lat tice and impurity mobilities, calculated as given in Tech. Note 788, were combined by the sine and cosine integral method [18] to obtain carrier mobility for use in the expression for the Hall coefficient in the mixed conduction case [19]. The scattering factor for electrons was taken as 1.2 [20] while the factor for holes was taken to be 0.87 [21], the temperature dependence of these quantities was neglected. Based on experimental results as reported above, the energy of the gold donor with respect to th valence band was taken as 0.355 eV.

Three values of the energy of the gold acceptor were selected. Two values, 0.58 and 0.60 eV above the valence band edge, were chosen to correspond approximately with mea sured slopes of the linear regions of the plots of  $R_{\rm H}T^{3/2}$  against 1/T. The third

value, 0.535 eV below the conduction band edge, is based on measurements of the gold acceptor energy with respect to the conduction band (NBS Spec. Publ. 400-1, p. 19) corrected for the previously neglected temperature dependence of the electron effective mass. The value for the density, N<sub>d</sub>,

of each specimen was adjusted to obtain a calculated Hall coefficient which agreed with the experimental one at room temperature. Since heat treatments, such as those employed in the diffusion process, have bee observed to result in significant changes o resistivity of lightly doped silicon, differences between these values of N<sub>d</sub> and the

initial phosphorus density may be due to changes in net dopant density. Although th

#### Table 1 — Properties of Gold-Doped Silicon Specimens

e le

n forc or r

S I-

ine f

that

| 2200N950-144         | 400N950-144                                                     | 80N1050-72                                                                                                                                             |

|----------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2300                 | 380                                                             | 75                                                                                                                                                     |

| $2.0 \times 10^{12}$ | $1.2 \times 10^{13}$                                            | $6.3 \times 10^{13}$                                                                                                                                   |

| 144                  | 144                                                             | 72                                                                                                                                                     |

| 950                  | 950                                                             | 1050                                                                                                                                                   |

| $6.4 \times 10^{4}$  | $2.2 \times 10^{5}$                                             | $1.6 \times 10^{5}$                                                                                                                                    |

| $4.4 \times 10^{15}$ | $2.6 \times 10^{15}$                                            | $1.0 \times 10^{16}$                                                                                                                                   |

|                      | $2300 \\ 2.0 \times 10^{12} \\ 144 \\ 950 \\ 6.4 \times 10^{4}$ | $\begin{array}{cccc} 2300 & 380 \\ 2.0 \times 10^{12} & 1.2 \times 10^{13} \\ 144 & 144 \\ 950 & 950 \\ 6.4 \times 10^4 & 2.2 \times 10^5 \end{array}$ |

Figure 9. Experimental data and theoretical curves for determining the energy level of the gold acceptor in initially *n*-type silicon converted to *p*-type by diffusion with gold.

gold density could have been adjusted to match the calculated and measured Hall coefficients, it was found that the gold density changes needed to accomplish this were somewhat larger than the estimated uncertainty of the gold density determinations.

The fit of the calculated curve to the experimental data at higher and lower temperatures was examined for different values of the gold acceptor energy to determine which value gave the best fit. The data at the low temperature end, where the resistivity is very high, were not given much weight in selecting the best value for the gold acceptor energy. It is thought that surface conduction or other experimental problems caused the data points to deviate downward from the true bulk values. Data from measurements on different days on these and other high resistivity specimens often showed shifts where the magnitude of the change increased as the resistivity increased or as the temperature decreased. The points plotted for each specimen are the highest set of values obtained as they are considered to be most representative of the bulk values. In each case, it is evident that the experimental results fit the shape of the curve calculated with the acceptor level 0.535 eV below the conduction band edge better than they fit either of the

other two curves. Although it is clear that fixing the acceptor to the valence band edge does not give a satisfactory fit, it is possible that allowing the acceptor level to maintain its same relative position in the forbidden gap as the temperature changed might give as good or better fits.

Numerous values of the activation energy of the gold acceptor have been reported in the literature. Tasch and Sah [22] and Sah et al. [10] concluded from emission rate data as a function of temperature that the level is 0.59 eV above the valence band. Parillo and Johnson [23], also from emission rate measurements, concluded that the level is  $0.72 \pm 0.01$  eV above the valence band. Collins et al. [13] concluded from Hall and resistivity data that the level is  $0.62 \pm$ 0.02 eV above the valence band. Detailed agreement with the present work depends on the temperature variation of the acceptor level with respect to the band edges. To establish the temperature variation, an improved model for carrier mobility is required so that more accurate fits can be made to the data near the Hall inversion.

Further analysis of the Hall effect data is being deferred pending investigation of procedures for calculating electron and hole mobilities. (W. R. Thurber)

#### 5.1. X-Ray Photoelectron Spectroscopy

The angular dependence of x-ray photoelectron spectra (NBS Spec. Publ. 400-4, p. 42) was investigated to study its applicability to the determination of depth distributions of surface impurities and thicknesses of thin surface films. A wide spectral survey scan of air stabilized silicon (which has a protective oxide coating resulting from room temperature aging in air) revealed three significant elements: silicon, oxygen and carbon. The spectra associated with these elements are shown in figure 10.

The relative area of each peak as a function of electron emission angle,  $\theta$ , is shown in figure 11. The similar responses of the lower kinetic energy silicon peak, labeled SiO<sub>2</sub>, and the oxygen peak supports the association of the SiO<sub>2</sub> peak with an oxide of silicon. The smaller carbon peak, labeled C<sub>T</sub>, displays the same behavior and may be

due to carbon bonded to oxygen in the silicon oxide layer. The essentially flat angular dependence of these peaks also suggests that the oxide layer is thicker than the electron escape depth. The higher energy carbon peak,  $C_{TT}$ , has maximum intensity for

electron emission parallel to the surface. This behavior may be expected of a thin superficial carbon layer. In contrast, the higher energy silicon peak, which is associated with elemental silicon is largest for electron emission perpendicular to the surface. This is typical of a substance covered by a material which attenuates electron emission from below.

These conclusions can be confirmed from an examination of the relative peak magnitudes. The ratios of the relative areas of the two carbon peaks and the two silicon peaks are drawn in figure 12 as functions of the electron emission angle. This figure emphasizes the usefulness of angular studies for determining the relative depths of the surface constituents. In this case, one notes that the elemental silicon is covered by its oxide and that carbon appears in two forms with  $C_{\tau\tau}$  exterior to  $C_{\tau}$ .

Earlier, ultralow-pressure oxidation in the spectrometer vacuum chamber of a silicon

surface cleaned by Ar<sup>+</sup> bombardment resulted in the introduction of a carbon film, presumably as silicon carbide, on the specimen. This experiment was repeated using a silicon specimen having an exceptionally low carbon content. The specimen was fixed at a given angle and heated by an adjacent tantalum strip through which current was passed. The current in the tantalum heater was varied from 0 to 22 A; at 35 A the silicon glows dull red, corresponding to a temperature of 750°C.

As recorded in figure 13, the area of the total carbon peak was observed to drop 60 percent over the heating range, while the oxygen and silicon peaks together increased by this same amount. The  $C_{TT}/C_{T}$  ratio was

Figure 11. Relative areas of x-ray photoelectron spectral peaks as a function of electron emission angle. ( $\bullet$ : oxygen;  $\bullet$ : total silicon;  $\diamond$ : total carbon;  $\Box$ : Si; O: SiO<sub>2</sub>;  $\diamond$ : C<sub>1</sub>. The inset depicts the geometrical arrangement and the electron emission angle,  $\theta$ .)

Figure 12. Ratios of the relative areas of the x-ray photoelectron peaks due to carbon and silicon as a function of electron emission angle. (•:  $C_{II}/C_{I}$ ; O:  $\underline{Si0}_2/Si.$ )

Figure 13. Relative areas of x-ray photoelectron spectral peaks of cleaned silicon surface heated in an ultralow pressure of oxygen as a function of heater current and ratio of relative areas of the peaks due to carbon. ( $\bullet$ : total carbon; O: oxygen;  $\diamond$ : total silicon;  $\Box$ : Si;  $\triangle$ : SiO<sub>2</sub>;  $\bullet$ :  $C_{II}/C_{\tau}$ .) also observed to rise. A mass spectrometer monitored the vacuum chamber gases during heating. At low temperatures the primary gas constituent was hydrogen, but as the temperature was raised the carbon monoxide content began to increase. At the highest temperatures, the mass spectrum became extremely complex.

The drop in the total carbon photoelectron signal is interpreted as a loss of this element from the specimen surface. The near constancy of the elemental silicon to the SiO<sub>2</sub> signal ratio indicates that practically no additional oxide was formed or removed from the specimen surface. The oxygen intensity variation is more puzzling. The kinetic energies and, correspondingly, the mean free paths for the oxygen electrons are less than for the silicon electrons. Therefore, the removal of a surface contamination layer should have a more pronounced effect upon the oxygen photoelectron emission. If all the oxygen were associated with the SiO2, then the oxygen peak should increase to a greater degree than the silicon peak. Since this was not the case, some of the oxygen may have been removed with the carbon, which suggests that not all the oxygen is associated with the silicon dioxide.

The C/O ratio of the monitored off-gassed material was in the order of 3:1. This ratio is rather low for typical diffusion pump oils, which probably suggests that some of the off-gassed oxygen was present as adsorbed water. At the highest heating currents used, a plateau appears in the silicon

NBS Surface Processes and Catalysis Section, Physical Chemistry Division. and oxygen photoemission intensities. Whether all the excess  $(non-SiO_2)$  oxygen was removed is not known, but it does seem clear that at least some fraction of the oxygen-containing adlayer has been removed.

In view of the above off-gassing data, one might wonder whether the angular distribution of photoelectrons from non-SiO<sub>2</sub> oxygen and SiO<sub>2</sub> silicon should actually track one another as in figure 11. The explanation may lie with the orientation of the adsorbed molecules. The oxygen end of the molecule is certain to be more polar than the hydrogen fraction and probably rests against the SiO<sub>2</sub> layer. These two oxygen signals would then contribute to a single oxygen signal, similar to that in figure 10b, which would track the SiO<sub>2</sub> angular variation.

> (N. Erickson\*, J. T. Yates, Jr.\*, T. E. Madey\*, and A. G. Lieberman)

#### 5.2. Comparative Study of Surface Analysis Techniques

A series of measurements has been initiated to compare various electron, ion and photon beam technologies for the determination of the depth profiles of impurities in silicon and silicon dioxide. In these preliminary measurements, specimens of boron and zinc implanted silicon and of aluminum and sodium implanted silicon dioxide are being used to provide, in most cases, a reasonably well known density of impurity at a reasonably well defined location. The specimens were selected from materials contributed by various semiconductor processing houses. The properties of the specimens are summarized in table 2. For each specimen the implantation angle (measured between the incident beam and the normal to the specimen surface),

Table 2 — Specimens for the Comparative Study of Surface Analysis Techniques

| Implanted Ion                    | В                    | Zn                   | Al                   | Na                     |

|----------------------------------|----------------------|----------------------|----------------------|------------------------|

| Host                             | Si                   | Si                   | 85 nm $SiO_2$ on Si  | 300 nm $SiO_2$ on $Si$ |

| Implantation Angle, deg          | 0                    | 0                    | 80                   | 0                      |

| Implantation Energy, keV         | 150                  | 30                   | 40                   | 50                     |

| Total Dose, cm <sup>-2</sup>     | $2.8 \times 10^{15}$ | $5 \times 10^{16}$   | $1.7 \times 10^{13}$ | $1 \times 10^{14}$     |

| Peak Density, cm <sup>-3</sup>   | $1 \times 10^{20}$   | $3.5 \times 10^{22}$ | $3.1 \times 10^{19}$ |                        |

| Projected Range, nm              | 570.6                | 22.6                 | 7.8                  |                        |

| Projected Standard Deviation, nm | 113.0                | 5.7                  | 2.3                  |                        |

the implantation energy, and the total dose were reported by the laboratory which supplied the implants; the peak density was calculated from the work of Mayer *et al.* [24]; and the projected range and standard deviation were based on calculations of Johnson and Gibbons [25].

Samples of these specimens are being subjected to secondary ion mass analysis (SIMS) [26], low and high energy ion scattering spectrometry (ISS [27] and RBS<sup>\*</sup> [28], respectively), Auger electron spectroscopy (AES) [29], x-ray photoemission spectroscopy (XPS or ESCA<sup>T</sup>) [30] and other techniques in laboratories associated with instrument manufacture, semiconductor analysis, or semiconductor device production. The specimens are expected to exercise the capabilities of the various measurement techniques and to provide illustrations of their different realms of applicability. Some characteristics of the results can be anticipated on the basis of the physical processes involved.

For detecting boron in a silicon matrix, it is expected that SIMS will demonstrate certain advantages over other techniques. The sensitivity of SIMS to small quantities of material and the virtual impossibility that a molecular ion having almost the boron mass may form during sputtering together imply that the density profile of boron in the boron implanted silicon specimen should be easily measured, even with a low resolution SIMS instrument. On the other hand, the low atomic mass of boron relative to silicon makes boron a difficult element to detect by an ion scattering technique at any energy. In addition, due to the low atomic number of boron, the cross-sections for x-ray photoemission and Auger electron emission are both very small, even though the Auger process is considerably more probable than the occurance of x-ray photoemission.