National Institute of Standards and Technology

Technology Administration

U.S. Department of Commerce

NISTIR 7181 January 2005 ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

## Semiconductor Electronics Division

**P**ROGRAMS, **A**CTIVITIES, AND **A**CCOMPLISHMENTS

## THE ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

One of NIST's seven Measurement and Standards Laboratories, EEEL conducts research, provides measurement services, and helps set standards in support of: the fundamental electronic technologies of semiconductors, magnetics, and superconductors; information and communications technologies, such as fiber optics, photonics, microwaves, electronic displays, and electronics manufacturing supply chain collaboration; forensics and security measurement instrumentation; fundamental and practical physical standards and measurement services for electrical quantities; maintaining the quality and integrity of electrical power systems; and the development of nanoscale and microelectromechanical devices. EEEL provides support to law enforcement, corrections, and criminal justice agencies, including homeland security.

EEEL consists of four programmatic divisions and two matrixmanaged offices:

Semiconductor Electronics Division

**Optoelectronics Division**

Quantum Electrical Metrology Division

**Electromagnetics** Division

Office of Microelectronics Programs

Office of Law Enforcement Standards

This document describes the technical programs of the Semiconductor Electronics Division. Similar documents describing the other Divisions and Offices are available. Contact NIST/ EEEL, 100 Bureau Drive, MS 8100, Gaithersburg, MD 20899-8100, Telephone: (301) 975-2220, On the Web: www.eeel.nist.gov

Cover caption: (clockwise from lower left) an IBM 200 mm EDRAM Wafer (photo by Tom Way, courtesy of International Business Machines Corporation, unauthorized use not permitted); a CMOS microhotplate-based conductance-type gas sensor; an HRTEM cross section of a structure, showing four of the six reference features, optimized for calibration to the structure's silicon lattice; and fluorescence images of a microfluidic device.

ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

# SEMICONDUCTOR Electronics Division

## **P**ROGRAMS, **A**CTIVITIES, AND **A**CCOMPLISHMENTS

NISTIR 7181

January 2005

U.S. DEPARTMENT OF COMMERCE Donald L. Evans, Secretary

**Technology Administration** Phillip J. Bond, Under Secretary for Technology

National Institute of Standards and Technology Hratch G. Semerjian, Acting Director

Any mention of commercial products is for information only; it does not imply recommendation or endorsement by the National Institute of Standards and Technology nor does it imply that the products mentioned are necessarily the best available for the purpose.

## CONTENTS

| Welcome                                                                                            | iv   |

|----------------------------------------------------------------------------------------------------|------|

| Mission                                                                                            | vi   |

| Vision                                                                                             | vi   |

| Values                                                                                             | vi   |

| Goals                                                                                              | vi   |

| Semiconductors: Backbone of the Electronic/Digital Revolution                                      | vii  |

| Semiconductor Electronics Division Organization                                                    | ix   |

| Electrical Test Structure Metrology                                                                | 1    |

| Metrology for System-on-a-Chip (SoC)                                                               | 6    |

| Power Semiconductor Device and Thermal Metrology                                                   | 9    |

| MicroElectroMechanical Systems                                                                     | . 13 |

| Nanoelectronic Device Metrology                                                                    | . 19 |

| Electronic Materials Characterization                                                              | . 24 |

| Advanced MOS Device Reliability and Characterization                                               | . 29 |

| Infrastructure for Integrated Electronics Design & Manufacturing                                   | . 32 |

| Knowledge Facilitation                                                                             | . 35 |

| Major Facilities / Laboratories                                                                    | . 37 |

| Microfabrication Process Facility                                                                  | . 38 |

| NIST Advanced Measurement Laboratory Nanofabrication Facility                                      | . 41 |

| National Research Council (NRC) Post-Doctoral Opportunities                                        | . 42 |

| Division Highlights                                                                                | . 46 |

| Uncertainties of CD Reference Features Significantly Reduced                                       | . 46 |

| SED Researcher Develops Novel 3D XML Browser/Editor                                                | . 47 |

| SED Writes First MEMS Standards                                                                    | . 48 |

| New Microfluidic DNA Analysis System for Forensics Applications Demonstrated                       | . 49 |

| Patterning PDMS Surfaces with Microfluidic Networks Provides<br>Foundation for Bioelectronics      | . 50 |

| SED Leadership Produces Unique Standard on Time-Dependent Breakdown of Ultra-Thin Gate Dielectrics | . 51 |

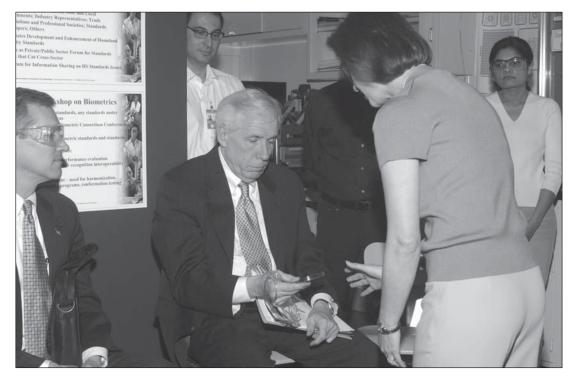

| Congressman Wolf Visits MEMS Laboratory                                                            | . 52 |

| SED Leads Major Semiconductor Metrology Conference Series                                          | . 53 |

| NIST's Gaithersburg, Maryland, Campus and Surrounding Area                                         | . 54 |

|                                                                                                    |      |

David G. Seiler, Division Chief

"Industry views SED's contributions as unique and essential to efficiently providing measurement techniques and standards."

> NRC Panel Report, An Assessment of the National Institute of Standards and Technology Measurement and Standards Laboratories: Fiscal Year 2003

## WELCOME

The Semiconductor Electronics Division (SED) provides leadership in developing the semiconductor measurement infrastructure essential to improving U.S. economic competitiveness. It provides necessary measurements, physical standards, and supporting data and technology; associated generic technology; and fundamental research results to industry, government, and academia. The primary mission of the Division is to provide the measurement infrastructure to U.S. industry for mainstream silicon CMOS (complementary metal-oxide semiconductor) technology. The Division's programs also respond to industry measurement needs related to MicroElectroMechanical Systems (MEMS), power electronics, and various sub-areas of nanotechnology including nanoelectronics, nanocharacterization, nanobiotechnology, and plastic electronics.

The Division has extensive interactions with individual companies, industry organizations, and professional societies; these activities enable the development of a research agenda responsive to the needs of industry. Active participation in industry roadmapping, such as the Semiconductor Industry Association's International Technology Roadmap for Semiconductors, and standards activities, such as committee work for the American Society for Testing and Materials, is practiced by the Division to prioritize and establish programs with the highest potential impact. The Division widely disseminates the results of its research, especially in the areas of standardized test methods and Standard Reference Materials (SRMs), through a variety of channels: publications, software, conferences and workshops, and participation in standards organizations and consortia. The Division also actively seeks industrial, academic, and non-profit research partners to work with collaboratively on projects of mutual benefit.

The Division, with a staff of about 80 including full-time and part-time employees as well as guest researchers, post-doctoral associates, and contractors, is based in Gaithersburg, Maryland. The Division is one of four divisions within the Electronics and Electrical Engineering Laboratory at NIST. The Division's technical activities are organized into three groups: the Enabling Devices and ICs Group, the CMOS and Novel Devices Group, and the Electronic Information Group. The Division assists industry by providing tools such as SRMs, test chips, standard reference data, and software that support the needed measurement infrastructure. Division personnel visit industrial sites, host a variety of visitors, and make available tutorial material on an as-needed basis. We also are active in conference and workshop activities that directly benefit the industry.

A broad array of activities that serve the semiconductor industry is currently underway in the Division. The staff of the SED addresses projects ranging from materials qualification to test structures for integrated circuits. Some of these projects are supported by the NIST National Semiconductor Metrology Program (NSMP), which is managed by the Electronics and Electrical Engineering Laboratory's Office of Microelectronics Programs. For more information on the NSMP, please visit their Web site at www.eeel.nist.gov/omp.

The Division, in cooperation with the National Research Council (NRC), offers competitive awards for post-doctoral research for U.S. citizens in a variety of technical fields related to the semiconductor electronics industry. For additional details, including field descriptions and qualification guidelines, please see page 42.

The technical programs, their goals, technical strategies, activities, and accomplishments described here for each Division project clearly demonstrate the impact of the SED's leadership and effective service as it continues to respond to the needs of industry and to contribute to the scientific and engineering communities. Please take an opportunity to visit our Division website at www.eeel.nist.gov/812/. In addition to providing further details on our Division and up-to-date project information, our website has interactive tutorials on the Hall effect (www.eeel.nist.gov/812/hall.html) and MEMS standard test structures based on e-standards (www.eeel.nist.gov/812/test-structures/). Please also be sure visit the Systems Integration for Manufacturing Applications website (www.nist.gov/sima) on product data exchange standards.

Thank you for your interest in our Division and its technical programs! I welcome your comments and suggestions. Feel free to e-mail me at david.seiler@nist.gov.

David & Seiler

David G. Seiler Division Chief

Semiconductor Electronics Division Staff

For additional information, contact:

Division/Office Telephone: 301-975-2054 Division/Office Facsimile: 301-975-6021 On the Web: www.eeel.nist.gov/812/ "The nature of the vision's purpose is not only to achieve a meaningful strategic or company goal, but also to build a dedicated

community ... "

Jay A. Conger, The Brave New World of Leadership Training, IEEE Eng. Mgmt. Review (1996)

## Mission

The Semiconductor Electronics Division provides technical leadership to industry, government, and academia in research and development of the semiconductor measurement and software infrastructure needs essential to the silicon microelectronics industry, advanced semiconductor materials technologies, and advanced electronic devices based upon molecular or quantum structures.

### VISION

The Semiconductor Electronics Division strives to be recognized as a dynamic, world-class resource for semiconductor measurements, data, models, software, and standards focused on enhancing U.S. technological competitiveness in the world market.

## VALUES

The Semiconductor Electronics Division values its commitment to identify and meet crucial measurement technology needs. The Division values its collaboration with all segments of the semiconductor community. It strives for integrity, excellence, objectivity, responsiveness, and creativity, while maximizing and utilizing the potential of its employees.

## GOALS

The Division will:

- Aggressively pursue and achieve select metrology needs as identified in the International Technology Roadmap for Semiconductors for mainstream silicon.

- Develop new and improved process-monitoring tools, methodologies, and data for the more efficient manufacture of silicon and compound-semiconductor devices.

- Support novel research that has high potential for providing breakthroughs in materials, process, devices, and measurement technologies for the semiconductor industry.

## SEMICONDUCTORS: BACKBONE OF THE ELECTRONIC/DIGITAL REVOLUTION

For the past 20 years, the personal computer reigned supreme as the driver of semiconductor industry growth. But new leadership is emerging. The communications revolution, perhaps the defining social and economic transition of our time, is fueled by the ever smaller, ever cheaper, ever faster invention of the chip industry. The explosive demands of the wireless, broadband Internet and optical networking industries have crowned the communications chip as the dominant end market for semiconductors.

- Information technology (IT) continues to be the primary driver of the U.S. economy, and U.S. semiconductor companies are leading the charge. American chipmakers now supply nearly half of the world's chips.

- U.S. chipmakers add more value to the national economy than any other industry.

- For 50 years, the semiconductor industry has provided the bricks and mortar that built the modern world. The exciting expansion in semiconductor applications means our job has only just begun and that our industry's greatest growth lies ahead.

- Personal communications devices will become so functional as to be indispensable, cars will be safer and more fuel-efficient, the quality of education will improve, chips implanted in our bodies will tell our doctor we're sick before we register symptoms. Eventually silicon and biology will converge, and the biocomputer will seem no more novel than today's laptop. As *Forbes ASAP* Editor Michael Malone has noted, "the microprocessor is the defining invention of the electronic age, the inventor of inventions."

- adapted from the Semiconductor Industry Association (SIA) 2001 Annual Report, pp. 2–5.

Semiconductors, transistors, and their applications represent one of the greatest scientific and technological breakthroughs of the twentieth century. Consider their far reaching influence on our society in general and our daily lives. Can you imagine life without them? Semiconductors are pervasive in the microelectronic components used in computers, entertainment equipment, automotive electronics, medical instrumentation, telecommunications, space technology, television, radio, cell phones, and many other information technologies. Every hospital, school, factory, car, airplane, office, bank, and household contains transistors, microprocessors, and other semiconductor devices.

These breakthroughs are possible because of the miniaturization of the transistor dimensions, which allows the construction of compact systems with tremendous computing power and memory. Miniaturization, in turn, is possible because of the perfection of fabrication techniques that allow the *integration* of circuits and thus the production of chips containing millions of elements per square centimeter. The foundation stone of this complex technology is silicon. Meeting the demands for these large-scale, complex, integrated circuits (ICs) continues to require technological advances in materials, processing, circuit design, characterization, testing, and standards.

The semiconductor electronics industry is outstripping the measurement capability needed for maintaining and improving U.S. international competitiveness. Important factors affected include product performance, price, quality, compatibility, and time to market. The Semiconductor Electronics Division provides the measurement capability needed to support the efforts of U.S. industry to improve its competitiveness. In order to support this effort, the Division also engages in technology development and fundamental research, making the findings available to industry.

The Division focuses the largest part of its resources on the development and delivery of measurement capability for two principal reasons: measurement capability has a very high impact on U.S. industry because it helps manufacturers address many of the challenges they face in realizing competitive products in the marketplace, and NIST is the official lead U.S. Government agency for measurements.

The Division focuses on developing measurement capability that is beyond the reach of the broad range of individual companies. Companies seek NIST's help for several reasons:

"This year the semiconductor industry will manufacture about 60 million transistors for every man, woman and child on earth. By 2008, chipmakers will be producing 1 billion transistors or more per year. Transistors improve our lives in countless ways-they make cars safer and more fuel-efficient, they enable personal communication devices, they promote medical breakthroughs and they improve the quality of education."

> Building Blocks for Innovation, SIA Annual Report 2002, p. 17

"Another success occurred in the development of standards for measuring the shrinking line widths that characterize semiconductor products. Because industry alone cannot develop these new standards of measurement, the National Institute of Standards and Technology (NIST) is overseeing the process."

SIA Annual Report 2004, p. 30.

- The companies need NIST's special technical capability for measurement development.

- The companies need NIST's acknowledged impartiality for diagnosing a measurement problem affecting the industry broadly or for achieving adoption of a solution across the industry.

- The companies cannot develop the measurement capability needed by the industry broadly because they cannot individually capture the returns of the cost of development.

- Industry's quality standards require that key measurements be traceable to the national measurement reference standards that NIST maintains. This is a requirement of growing importance in export markets.

The Division continues to interact and collaborate with a wide variety of companies, consortia [such as International Semiconductor Manufacturing Technology (ISMT), Semiconductor Equipment and Materials International (SEMI), and the Semiconductor Research Corporation (SRC)], academia, and other government labs to accomplish its mission. Specific details are given in the project descriptions that follow. Work in the Division results in extensive outputs or deliverables that cover knowledge and improvements in physical understanding, test methods and measurements, Standard Reference Materials (SRMs), Standard Reference Data (SRD) sets, standards, test structures and test chips, software, measurement accuracy and traceability, publications and reports, patents and Cooperative Research and Development Agreements (CRADAs), round robins, data and models, talks and short courses, company visits, conferences and workshops, consortia participation, and various activities and leadership roles on committees and working groups.

Division staff serve the semiconductor community in leadership roles on standards committees such as American Society for Testing and Materials (ASTM) and Electronic Industries Alliance (EIA) / Joint Electron Device Engineering Council (JEDEC), societies such as IEEE, ECS, and APS, and numerous semiconductor conferences/workshops. Many test methods and standards have been developed and written over the years by NIST staff for ASTM and EIA/JEDEC, including ones for resistivity, oxygen in silicon, thin dielectrics, electromigration, and device characterization. Staff serve on various Technical Working Groups to help put together the International Technology Roadmap for Semiconductors (ITRS). These groups are Process Integration, Devices, and Structures; Assembly and Packaging; Lithography; Interconnect; Front End Processes; and RF and Analog Mixed Signal. The ITRS provides targets for equipment, material, and software suppliers; provides targets for researchers; and serves as a common reference for the semiconductor industry.

The Division also has impacted the semiconductor community by producing a number of SRMs. To date, over 2,800 SRMs have been sold and distributed for resistivity, oxygen in silicon, and optical thickness by ellipsometry. Hundreds of companies throughout the world have purchased these SRMs to maintain and improve their measurement capabilities.

For the future, the Division has identified nanotechnology and its various sub-areas, including nanoelectronics, nanocharacterization, nanobiotechnology, and plastic electronics, as emerging areas of research to address.

"The semiconductor industry is rapidly reaching a point in its evolution where its ability to build smaller nodes will encounter serious difficulties in the form of quantum effects and atomic level statistical fluctuations ... nanotechnology will both help keep CMOS scaling on track *and* enable new materials/technology platforms that satisfy market needs better than CMOS ... as current lithography methods reach their limit, the tools used in the development, manufacture, and testing of CMOS will increasingly be based on nanotechnology."

- from L. Gasman, "Why Nanotechnology Is So Important for the Semiconductor Industry," NanoMarkets White Paper, p. 2.

## SEMICONDUCTOR ELECTRONICS DIVISION ORGANIZATION

#### **DIVISION OFFICE (812.00)**

| 2054 | SEILER, David G., Chief       |

|------|-------------------------------|

| 2054 | GUARIGLIA, Lori A., Secretary |

| 4514 | COOK, Sharon W., AO           |

## ENABLING DEVICES AND ICs GROUP (812.05)

2068 BLACKBURN, David L. (GL)2052 WILKES, Jane, Secretary

#### ELECTRICAL TEST STRUCTURE METROLOGY

2072 CRESSWELL, Michael W. (PL)

5026 ALLEN, Richard A.

8193 MURABITO, Christine E.

2234 SCHAFFT, Harry A. (CNR)

2182 YARIMBIYIK, Emre (GR)

#### METROLOGY FOR SYSTEM-ON-A-CHIP

2071 HEFNER, Allen R., Jr. (PL)

5420 AFRIDI, Muhammad Y. (CNR)

2069 BERNING, David W.

2236 ELLENWOOD, Colleen E.

5484 GEIST, Jon (CNR)

6757 SALCEDO, Javier (GR)

6757 VARMA, Ankush (GR)

#### Power Device and Thermal Metrology

2071 HEFNER, Allen R., Jr. (PL)

8777 AKUFFO, Adwoa (CNR)

2081 DUONG, Tam (CNR)

2236 ELLENWOOD, Colleen E.

8776 HERNANDEZ, Madelaine (CNR)

#### MICROELECTROMECHANICAL SYSTEMS

2070 GAITAN, Michael (PL) 5484 GEIST, Jon (CNR) 4796 HONG, Jennifer (CNR) 4739 HUANG, John (S) 4710 JAHN, Andreas (GR) 4110 MacARTHUR, Daniel (S) 2049 MARSHALL, Janet C. 2052 McGRAY, Craig (PD) 6367 MIJARES, Geraldine I. 2045 MORGAN, Nicole (PD) 2492 NABLO, Brian (PD) 6347 POLK, Brian 5466 **REYES-HERNANDEZ**, Darwin 2305 SHAH, Jayna (GR) 3095 SUNDARESAN, Siddarth (GR)

- 2079 BENNETT, Herbert S., NIST Fellow

- 2097 HARMAN, George G., Scientist Emeritus

- 50 SECULA Entit M Editor

- 2050 SECULA, Erik M., Editor

## Wire Bonding to Cu/Low-K Semiconductor Devices (FA)

2097 HARMAN, George G. (FL)

#### CMOS AND NOVEL DEVICES GROUP (812.06)

- 4723 VOGEL, Eric M. (GL)

- 2053 St. CLAIR, Melissa, Secretary

#### NANOELECTRONIC DEVICE METROLOGY

| 2082 | RICHTER, Curt A. (PL)      |

|------|----------------------------|

| 2078 | EDELSTEIN, Monica D.       |

| 2233 | HACKER, Christina          |

| 2087 | KIRILLOV, Oleg             |

| 8755 | KOO, Sang-Mo (GR)          |

| 3241 | LI, Qiliang (CNR)          |

| 5291 | RAMACHANDRAN, Ganesh (CNR) |

| 2247 | SUEHLE, John S.            |

|      |                            |

- 4723 VOGEL, Eric M.

- 3377 WANG, Wenyong

#### **ELECTRONIC MATERIALS CHARACTERIZATION**

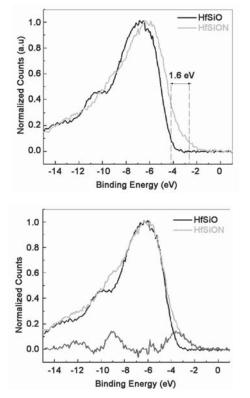

2089 KOPANSKI, Joseph J. (PL) 5974 AMIRTHARAJ, Paul (GR) 2084 CHANDLER-HOROWITZ, Deane 2060 EHRSTEIN, James R. 2088 JELIAZKOV, Stoyan (CNR) 3241 LITTLER, Chris (GR) 2044 NGUYEN, Nhan V. 2048 PARK, Seong Eun (GR) 2067 THURBER, W. Robert (GR)

#### Advanced MOS Device Reliability and Characterization

- 2247 SUEHLE, John S. (PL)

- 2078 EDELSTEIN, Monica D.

- 8687 HEH, Da-Wei (GR)

- 8755 KOO, Sang-Mo (GR)

- 4723 VOGEL, Eric M.2111 ZHU, Baozhong (GR

- ZHU, Baozhong (GR)

#### THEORETICAL SOLID-STATE PHYSICS FOR SEMICONDUCTORS (FA)

2079 BENNETT, Herbert S. (FL)

#### Legend:

AO = Administrative Officer CNR = Contractor FA = Focus Area FL = Focus Area Leader FM = Facility Manager GL = Group Leader GR = Guest Researcher PD = PostDoctoral Appointment PL = Project Leader S = Student

Telephone numbers are: (301) 975-XXXX (replace XXXX with the four-digit extension as indicated)

## NIST AML NANOFABRICATION FACILITY & SED MICROFABRICATION FACILITY

- 2699 HAJDAJ, Russell (FM)

- BUCK, Laurence M.

- 5623 OWEN, James C.

- 2095 KESWANI, Vinay (CNR)

- 2096 ROPPOLO, Richard

## ELECTRONIC INFORMATION GROUP (812.07)

3644 BRADY, Kevin G. (GL)2053 St. CLAIR, Melissa, Secretary

#### INFRASTRUCTURE FOR INTEGRATED ELECTRONICS DESIGN AND MANUFACTURING

- 4284 MESSINA, John (PL)8778 ARONOFF, Matthew

- 8778 ARONOFF, Matthew4951 BABOUD, Julien (GR)

- 5108 BERTON, Dominique (GR)

- 3644 BRADY, Kevin G.

- 4229 DEVAULX, Frederic (GR)

- 2432 GRIESSER, Art

- 8581 KHALILI, Neda (S)

- 3263 KOSTICK, Jennifer A.

- 5319 LI, Ya-Shian

- 3246 MOORE, David (GR)

- 3956 SIMMON, Eric

- 5319 SMITH, Nathan (S)

#### KNOWLEDGE FACILITATION

- 3263 KOSTICK, Jennifer A. (PL)

- 4479 MEYER, Mariana (S)

- 8747 NEWTON, Meridel (S)

#### Legend:

AO = Administrative Officer CNR = Contractor FA = Focus Area FL = Focus Area Leader FM = Facility Manager GL = Group Leader GR = Guest Researcher PD = PostDoctoral Appointment PL = Project Leader S = Student

Telephone numbers are: (301) 975-XXXX (replace XXXX with the four-digit extension as indicated)

## **ELECTRICAL TEST STRUCTURE METROLOGY**

#### GOALS

Develop test-structure based metrology utilizing electrical and other techniques: characterize the efficacy of interconnect materials, with emphasis on ultra-high-density copper interconnects; apply MEMS-based silicon-patterning techniques to the fabrication of test structures for critical dimension (CD) and overlay extraction by optical, electrical, or other methods; and contribute to standards organizations supporting the extension of metrology standards to copper interconnect.

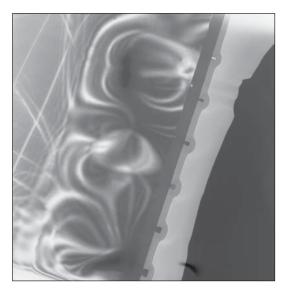

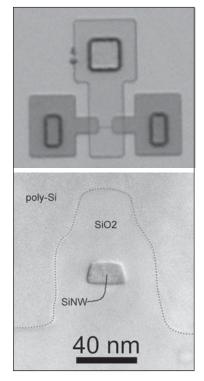

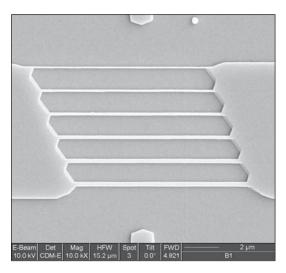

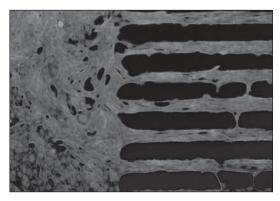

HRTEM cross section of a CD test structure, comprised of six reference features optimized for calibration to the structure's silicon lattice.

#### **CUSTOMER NEEDS**

In order to meet new clock-frequency demands, research by the semiconductor industry has focused on lower-resistance interconnect materials. The primary material replacing aluminum as an interconnect material is copper because of its nominally low resistance properties and its improved reliability characteristics. For example, Intel's most-recently announced fabrication process will feature transistors having 35 nm gate length, which will be the smallest and highest-performing complementary metal oxide semiconductor (CMOS) transistors in high-volume production. The process integrates eight copper interconnect layers that increase the signal speed inside the chip and reduce chip power consumption. Intel will continue to use copper interconnects for several more technology nodes. However, there is concern that the projected benefits of copper may not map into interconnect features with dimensions projected by the International Technology Roadmap for Semiconductors (ITRS) because relatively little research has been reported on the limiting physics of electron transport in ultra-narrow metal conductors.

Interconnect fabrication processes involve a sequence of up to several tens of lithographic operations, each requiring close alignment of the patterned resist to features that have been etched after the previous such operation. Successful manufacturing typically requires alignment accuracies in the low several nanometers range. The demand for accurate alignment is increasingly challenging not only for the lithographic tool manufacturers and users, but also for the metrologists contributing to the process-control infrastructure. For example, the ITRS, which specifies the overlay requirements for each technology node (DRAM halfpitch), specifies 3.3 nm for the 2005 / 90 nm node decreasing to 1.6 nm for the 2010 / 45 nm node. Thus the metrology challenge to which this project proposes to contribute is the verification of metrology tool performance. Overlay quality is the closeness to zero of the overlay vector, which traditionally has been measured by optical metrology tools. At earlier lithography nodes, these tools have performed adequately. However, at smaller lithography nodes, corrections called shifts have increased in size relative to the measured overlay. These shifts are extracted from the wafer-tool interaction and applied to local measurements of the overlay vector. As design rules have further decreased to the sub-tenth micrometer region, a new challenge has arisen from the fact that the metrology is fundamentally optical in nature. In general, the local value of the measured optical overlay, even when corrected for shifts, does not adequately match the local value of the interconnect system's performance. The problem is that electrical overlay is the functionally relevant quantity from the viewpoint of circuit performance. We plan to use a test structure patented by project staff that provides the relationship between the optically-extracted overlay and the electrical overlay thereby enabling established overlay metrology tooling to be applied to the latest generations of scaled interconnect systems.

The emerging metrology known as opticaldiffraction process (ODP) control scatterometry translates broadband light, diffracted from an onwafer grating patterned into the resist or film, into Technical Contact: Michael W. Cresswell

**Staff-Years (FY 2004):** 3.5 professionals 1.5 guest researchers accurate profiles of the grating's features from which key parameters, such as CD, can be extracted. Whereas currently favored metrology tools such as CD scanning electron microscopes require a vacuum wafer environment, optical scatterometry does not and is fast and noninvasive. The possibilities of ODP extend to characterizing the sidewall angle and height of critical features. Until physical standards are available, the full promise of ODP control scatterometry may not be met.

The ITRS has warned that the photomask industry is beginning to trail the requirements of the semiconductor manufacturers, especially with regard to CD metrology. Co-development of an adequate photomask CD-metrology infrastructure is essential to support the technical and manufacturing needs of optical lithography below 100 nm. At the present time, there is no established technique that meets the stated requirements. Optical transmission microscopy has been the primary metrology method used by photomask makers and has the advantage of traceability, but this technique is not readily available to photomask users. Whereas International SEMATECH (ISMT) is developing an atomic force microscopy (AFM) implementation through the use of carbon nanotubes as robust measurement tips, this approach could prove costly and may be fundamentally too slow for full-mask inspection. In addition, AFM is inherently slow and requires contacting the surface of the photomask, which can be a cause of contamination. Scanning electron microscopy (SEM), although increasingly used for CD measurements on photomasks, is limited by charging of the quartz substrate. On the other hand, electrical metrology has no known lower CD limits and could be contamination free except for the fact that it is a contact metrology with inherent particulate hazards. Interestingly, no references to scatterometry for mask CD-control have been reported, and it seems that this is one application where ODP metrology could offer unique benefits.

#### **TECHNICAL STRATEGY**

Challenges associated with advanced interconnect include the understanding of charge transport in very narrow features. The charge transport is affected by the interaction of the charge carriers with grain boundaries and sidewalls. When the size of either the grains or lines is significantly larger than the mean free path of the electrons, the conductivity of the wires is similar to that of bulk. However, when these dimensions are less than or equal to the mean free path, the conductivity is expected to increase significantly. There are two "features" of conventional copper interconnect systems that complicate any experiments. The first feature is the barrier layer that is needed to keep the copper from diffusing into the surrounding insulator and silicon layers. This barrier layer is usually comprised of a metal, such as tantalum, which is a poor conductor. The second feature is that the planarization in the damascene patterning process can lead to dishing or erosion, which leads to the sheet resistance being a very non-linear function of dimension. Decoupling the contributions to a measured sheet resistance of these two effects is difficult, if not impossible.

In this project, we are taking several approaches to address these issues: The first approach is to develop a model from which the sheet resistance can be calculated for an arbitrary set of dimensions, grain sizes, and scattering coefficients. The results from this model will be compared with measurements of patterned and unpatterned copper films at a range of temperatures. To simplify analysis of the material, we will initially measure copper films with no barrier layer and later extend the measurements to films with barrier layers.

A new challenge in overlay metrology is emerging as a consequence of scaling. The problem is that a planar definition of overlay does not provide for functionally relevant electrical overlay which has three-dimensional qualities. On the other hand, an electrically readable overlay test-structure has been proposed by us earlier. It requires a two-level metal interconnect process and will be the first time that the concept, for which NIST holds several patents, will have been reduced to practice. A key element of the test structure is the combination of a standard overlay frame-in-frame target, appended to an electrically testable component. The composite test structure has multiple elements, each having staggered built-in overlays. The latter's function is to enable the identification, by electrical testing, of the as-replicated cell that has zero electrical overlay, which can then be used as a calibration artifact for normal optical, SEM, or AFM metrology tools by providing corrections to such systems that are based on functionally relevant behavior of the fabricated patterns. In other words, the test structure addresses the problem that overlay extraction by optical means is challenged by the complex interaction of errors known as wafer-induced shift and tool-induced shift. It separates these errors and allows for their correction. It is fabricated on production wafers

just as are other test structures that are inspected by fabrication-line metrology tools. However, after fabrication and optical and electrical testing, it serves as a means of calibrating the optical tools that are used to monitor overlay on that particular fabrication line. Its fundamental attribute is that it enables the user to identify the critical relationship between the readings of his/her conventional optical metrology tools during inspection of product wafers and the "functionally relevant" overlay properties of the interconnect system under fabrication.

The project will incorporate a "Mask ECD" (Electrical Critical Dimension) task that would build on our previous experience working with a major U.S. mask supplier to the semiconductor industry. In that work, we devised a direct means of comparing measurements of features made on the mask with the replicated features transferred from the mask to the wafer. We plan to take this work to the implementation stage with an industry partner. In addition, we will explore the feasibility of extracting CDs from electrical test data made on an alternating aperture phase-shift mask. Other workers in test-structure metrology also have claimed that such electrical measurements have the potential to be both faster and more repeatable than optical or CD-SEM methods and provide the motivation for continued study of this approach. Two exciting extensions of mask metrology using neither SEM nor optical tools are being considered. One extension is non-contact ECD, which would draw heavily on knowledge and experience of staff in EEEL's Boulder, Colorado, site and may result in a collaborative activity exploring the development of a microwave sensor specifically for the mask-CD metrology application. The second extension to our mask CD metrology approach is scatterometry. The application of scatterometry to mask-CD metrology would provide a powerful tool for mask CD-control.

There also is a need for standards, especially related to interconnects. In this project, we will continue to participate in JEDEC and SEMI standards committees with special emphasis on those relating to interconnect reliability and process control.

**DELIVERABLE:** Draft and submit manuscript on surface-dominated conduction-electron scattering in copper films and patterned features. Develop process for patterning recesses in silicon wafers to accommodate patterned chips for copper-seeding, electro-deposition, and CMP planarization. Complete L-EDIT CAD for mask to facilitate comparison of CDs extracted electrically by ODP scatterometry from the same features. **DELIVERABLE:** Develop process for seed-layer deposition on SCCDRM chips. Make initial electrical measurements on a selection of SCCDRM features. Prepare draft standard on ECD extraction for review by SEMI.

**DELIVERABLE:** Complete CMP processing of first copper-interconnect test wafers and initiate fabrication of overlay test-structure wafers. Make ECD and scatterometry-CD (probably in collaboration with a scatterometry CD tool manufacturer) measurements on scatterometry test-structures. Prepare draft of paper on modulating current through SCCDRM features by electrical or other means.

**DELIVERABLE:** Report on initial electrical measurements on first copper-interconnect test wafers as the latter become available from fabrication. Make ODP measurements on electrical scatterometer test structures. Complete fabrication of first lot of electrical-overlay test structures.

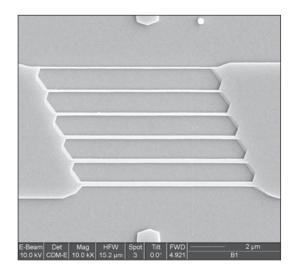

SEM image of the new test structure. (Lengths of the lines shown are approximately 10  $\mu$ m, and the widths range from about 45 nm to 210 nm.)

#### ACCOMPLISHMENTS

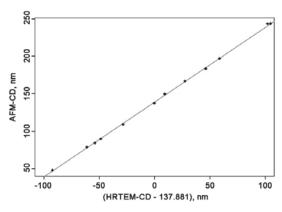

Delivered to ISMT, in collaboration with NIST's Manufacturing Engineering Laboratory (MEL) and Information Technology Laboratory (ITL), ISMT, and VLSI Standards, 10 chips containing NIST calibrated CD reference features. These chips, which have been distributed to ISMTs 10 member companies, including Intel, IBM, TI, AMD, and Freescale/Motorola, were delivered with sub-100 nm CDs and combined uncertainties less than 5 nm. The improvement in uncertainty resulted from the implementation of a new type of HRTEM-target test structure, the extensive use of SEM inspection to identify targets with superior CD uniformity, and the use of advanced AFM to serve as the transfer metrology. Commercialization of these reference features is being considered by VLSI Standards.

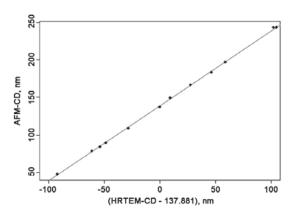

*Example of AFM transfer calibration from a single HRTEM target.*

Introduced a new HRTEM test structure target. This target contains six features with a distribution of drawn linewidths, positioned in such a way as to allow for HRTEM measurement of all six lines from a single sample preparation process, the most time-consuming and costly part of HRTEM. HRTEM provides the essential absolute primary measurement of CD, since it is traceable to the known spacing of the lattice planes of monocrystalline silicon. This new target is also optimized for AFM imaging which, for these chips, provided the transfer calibration since HRTEM imaging destroys the chips.

Developed, in collaboration with NIST's MEL and ITL, a measurement and data analysis procedure to minimize the expanded uncertainty associated with the CD reference features delivered to ISMT. The expanded uncertainty is derived statistically from the calibration function, which enables tracing the AFM measurements to the silicon lattice-plane spacing using HRTEM imaging. The previous generation of reference materials, which was delivered in 2001 and used electrical CD as the transfer calibration, had uncertainties of approximately 14 nm. The second generation units distributed to the ISMT member companies have CDs as low as 45 nm and uncertainties, based on statistical analyses performed by personnel of NIST's Statistical Engineering Division, of between 1.5 nm and 3 nm. This decrease in uncertainty is of major importance to the end-user of these reference features.

Besides the advances represented by the novel design of the described test structure, and the role played by NIST in leading the development of world-class three-dimensional AFM metrology at ISMT facilities in Austin, two other innovations were implemented to help this project-team's members achieve the remarkable reduction in CD uncertainty. The first was the installation and maintenance of a database to archive and rank several thousand SEM images of candidate features according to nanoscale CD uniformity. The second was the introduction of ultrasonically agitated patterning etches which are believed to have made at least some contribution to the feature uniformity, which in turn is essential for a lowuncertainty product. The third was devising a scheme for reliably extracting the lattice-plane counts from ultra-high-magnification electrontransmission phase-contrast images of reference features' cross sections. Finally, the contributions in statistical analysis made by our partner in ITL played a critical role in enabling us to conclude this phase of the project with such spectacular results.

Distributed to the ISMT member companies, as well as archiving at ISMT, a Technology-Transfer Document containing all essential details of the final phase of the SCCDRM program; its November 2004 delivery served as the completion of the SCCDRM program.

Participated in completion of the JEDEC JESD33B standards for measuring and using the temperature coefficient of resistance to measure the temperature of aluminum and copper interconnect lines. Participating in the revision of the JEDEC JESD87 and JEDEC JEP139 standards. Each is being revised to make them applicable to copper as well as aluminum lines.

### FY OUTPUTS

#### Collaborations

International SEMATECH, Development of SEM imaging and AFM CD-profile extraction

NIST ITL, Traceability statistics and procedures

NIST MEL, AFM CD-profile extraction

VLSI Standards, Substrate implant and anneal specifications, photo lithography and hard-mask engineering solutions

Accurel Systems, Design of HRTEM targets and formulation of appropriate imaging procedures

University of Edinburgh, United Kingdom, Advanced copper interconnect

#### STANDARDS COMMITTEE PARTICIPATION

Electrical Test Structures Task Force, Co-chair (Richard A. Allen)

SEMI International Standards Micro-lithography Committee, member (Richard A. Allen)

#### **RECENT PUBLICATIONS**

N. Guillaume, W. K. Kahn, R. A. Allen, M. W. Cresswell, M. E. Zaghloul, "Application of Conformal Mapping Approximation Techniques: Parallel Conductors of Finite Dimensions," IEEE Transactions on Microwave Theory and Techniques, Vol. 53, No. 3, pp. 812-821 (01-JUNE-2004)

N. Guillaume, R. A. Allen, M. W. Cresswell, M. Lahti, L. W. Linholm, M. E. Zaghloul, "Non-contact Electrical CD Metrology Sensor for Chrome Photomasks Featuring a Low Temperature Co-fired Ceramic Technology," IEEE Trans. on Semiconductor Manufacturing, Vol. 17, No. 1, pp. 25-34 (01-MAY-2004)

R. A. Allen, M. W. Cresswell, L. W. Linholm, "Junction-Isolated Electrical Test Structures for Critical Dimension Calibration Standards," IEEE Trans. Semiconductor Manufacturing, Vol. 17, No. 2, pp. 79-83 (01-MAY-2004)

R. A. Allen, R. I. Patel, M. W. Cresswell, C. E. Murabito, B. Park, M. D. Edelstein, L. W. Linholm, "Recent Developments in Producing Test-structures for Use as Critical Dimension Reference Materials," ICMTS IEEE International Conference on Microelectronic Test Structures, March 22-25, 2004, Awaji, Japan, pp. 35-40 (01-MARCH-2004)

R. A. Allen, M. W. Cresswell, C. E. Murabito, R. Dixson, E.H. Bogardus, "Critical Dimension Calibration Standards for ULSI Metrology," Characterization and Metrology for ULSI Technology: 2003, International Conference on Characterization and Metrology for ULSI Technology, March 24-28, 2003, Austin, Texas, pp. 421-428 (30-SEPT.-2003)

R. A. Allen, B. A. am Ende, M. W. Cresswell, C. E. Murabito, T. J. Headley, W. F. Guthrie, L. W. Linholm, C. H. Ellenwood, E.H. Bogardus, "Test Structures for Referencing Electrical Linewidth Measurements to Silicon Lattice Parameters Using HRTEM," IEEE Transactions on Semiconductor Manufacturing, Vol. 16, No. 2, pp. 239-248 (01-MAY-2003)

R. A. Allen, M. W. Cresswell, L. W. Linholm, "Junction-Isolated Electrical Test Structures for Critical Dimension Calibration Standards," 2003 ICMTS IEEE International Conference on Microelectronic Test Structures, March 17-20, 2003, Monterey, California, pp. 3-7 (31-MARCH-2003)

J. von Hagen, H. A. Schafft, "Temperature Determination Methods on Copper Material for Highly Accelerated Electromigration Tests (*e.g.*, SWEAT)," 2002 IEEE International Integrated Reliability Workshop Final Report, 2002 Integrated Reliability Workshop, Oct. 21-24, 2002, Lake Tahoe, California, pp. 45-49 (01-FEB.-2003) H. A. Schafft, J. R. Lloyd, "Electromigration Discussion Group Summary," 2002 IEEE International Integrated Reliability Workshop Report, 2002 IEEE International Integrated Reliability Workshop, Oct. 21-24, 2002, Lake Tahoe, California, pp. 204-206 (01-FEB.-2003)

H. A. Schafft, L. M. Head, J. Gill, T. D. Sullivan, "Early Reliability Assessment Using Deep Censoring," Microelectronics Reliability, Vol. 2003, No. 43, 16 pp. (01-JAN.-2003)

N. Guillaume, M. Lahti, M. W. Cresswell, R. A. Allen, L. W. Linholm, M. E. Zaghloul, "Non-contact Electrical Critical Dimensions Metrology Sensor for Chrome Photomasks," Proc. Intl. Soc. for Optical Engineering (SPIE), 21st Annual BACUS Symposium on Photomask Technology, Oct. 02-05, 2001, Monterey, California, Vol. 4562, pp. 822-829 (01-OCT.-2002)

#### Technical Contact: Allen R. Hefner, Jr.

Staff-Years (FY 2004): .75 professional 1.75 guest researchers

#### GOALS

The goal of the project is to develop solutions to key metrology issues confronting the semiconductor System-on-a-Chip (SoC) industry. These include development of measurement methods and standards for characterizing embedded-sensor (ES) virtual components (ES-VCs), a critical class of building blocks from which SoCs are developed. The goal of this project is to promote and support the development of hardware and software standards for specifying ES-VCs compatible with the SoC integration methodology used for digital IC design.

METROLOGY FOR SYSTEM-ON-A-CHIP (SoC)

This NIST effort will enable ES-VCs to be included in SoC computer-aided design (CAD) libraries and enable integration of ES-VCs with the existing digital VCs used ubiquitously by industry to design large ICs. The methods and standards developed as a result of this work will be essential for the realization of integrated, smart, low-cost, homeland security and environmental sensor systems.

One focus is on delivering standards to facilitate the incorporation of multi-technology (MT) VCs, including MEMS-based VCs, into SoCs. The project activities include: multi-technology hardware description language (HDL) model development, VC interface standards, synthesis and scaling standards for ES-VCs compatible with digital methodologies, and testing standards and verification standards. The NIST MEMS-based integrated gas-sensing VC will be used as a test bed to demonstrate the viability of these standards. In addition, the demonstration of general purpose gas-sensing VC methodologies will be used to facilitate the adoption of these MT-VCs into new homeland security and industrial applications.

#### **CUSTOMER NEEDS**

The driving force in today's semiconductor industry is the need to maintain a rate of performance improvement of 2x every two years in high-performance components. Historically, these improvements have relied exclusively on advances made by semiconductor miniaturization technology. The 2003 International Technology Roadmap for Semiconductors (ITRS) suggested that, "innovations in circuit design and architecture will be needed to design chips with both the desired performance and power dissipation." Achievement of this advancement in circuit and system design techniques is increasingly becoming dependent on integrating multiple technologies into a single chip referred to as System-on-a-Chip (SoC). The design challenges for SoC devices will be overcome with the use of platform-based design approaches that emphasize design reuse (*e.g.*, the development of ES-VCs that can be used as cost-effective building blocks for SoC devices).

The direct customers for this infrastructure building will be the makers of system design software, companies manufacturing ES-SoCs, and systems designers.

An October 20, 2003, article entitled "SoC Creation Requires Rules" written by Thomas L. Anderson, EE Times, states "While EDA vendors may provide detailed instructions and methodology guides for their specific tools, there has not been much industry activity in establishing more general rules, guidelines and best practices."

#### TECHNICAL STRATEGY

1. To develop ES-VCs for SoC design methodology successfully, the first step in this multi-step process is to develop the ability to produce the ES-VC devices via a standard CMOS compatible process. To demonstrate this capability we have chosen a MEMS microhotplate-based ES-VC, including operational amplifiers, decoders, and an analog-to-digital converter (ADC) to process the data.

**DELIVERABLE:** Develop post processing technology that will enable the microhotplate to scale to standard submicron mixed signal IC foundry processes.

2. The second step in making the ES-VC is to make it compatible with the digital SoC design methodology. This approach will require the ES-VC to have digital interface circuitry and to have Design-for-Test (DFT) and Built-In-Self-Test (BIST) functionality features. To facilitate this approach we will develop methodologies and standards for adding digital shells to ES-VCs and demonstrate them on the gas sensor VC described above.

**DELIVERABLE:** Develop methodologies for designing digital interface shells, develop DFT and BIST functionality for ES-VCs, and demonstrate their viability via the NIST microhotplate gas sensor technology.

3. The predominant design approach used by industry for SoC devices is top-down design. This

requires that high-level HDL models exist for the VCs that are candidates for use in any particular system of interest. Compared to those for digital VCs, the methodology and standards for developing high-level models for ES-VCs are at best poorly developed. To address this need, high-level models are being developed for ES-VCs using Analog and Digital HDLs, and methodologies are being developed to validate the models.

**DELIVERABLE:** Develop methodologies and standards for developing high-level models for ES-VCs and demonstrate their viability via the NIST micro hotplate gas sensor technology.

4. After the high-level simulation of the system in the top-down design process is successfully completed, the next step is to synthesize the individual VCs. Compared to those for digital VCs, the methodology and standards for ES-VC synthesis are at best poorly developed. To address the need for synthesizing ES-VCs, we are developing standards and metrologies for a non-digital synthesis like process that is compatible with digital synthesis. This process is based upon libraries of existing designs and the device design equations.

**DELIVERABLE:** Develop Gas Sensor SoC system architecture utilizing the ES-VC and synthesize system design demonstrating viability of ES-SoC methodology.

5. The testability of ES-VCs represents another significant challenge since standards and methodologies for non-digital circuits do not exist. The most promising approach to address testability is to use BIST techniques. To facilitate this approach, we will develop methodologies and standards for adding BIST to ES-VCs and interface them via the digital shell.

**DELIVERABLE:** Develop test bed for evaluation of gas sensor VC built-in self test function demonstrating DFT requirements for ES-SoC design methodology.

#### ACCOMPLISHMENTS

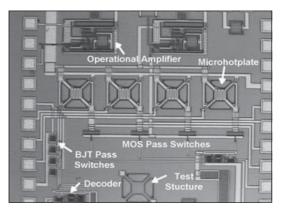

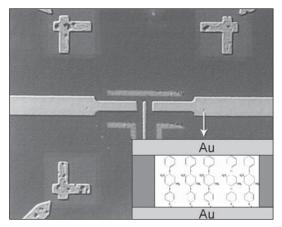

• A monolithic micro-gas-sensor system was designed and fabricated in a standard CMOS process. The gas-sensor system incorporated an array of four microhotplate-based gas-sensing structures. The system utilized a thin film of tin oxide (SnO<sub>2</sub>) as a sensing material. The interface circuitry on the chip has digital decoders to select each element of the sensing array and an operational amplifier to monitor the change in conductance of the film. The chip is post-processed to create microhotplates using bulk micro-machining techniques. Detection of gas concentrations in the 100 parts-per-billion range was achieved. This represents a factor of 100 improvement in sensitivity compared to existing MEMS-based microhotplate gas sensors.

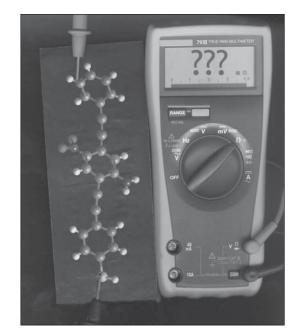

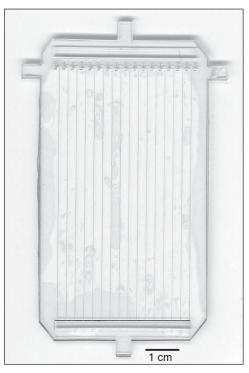

Micrograph of gas-sensor system to be used as demonstration vehicle.

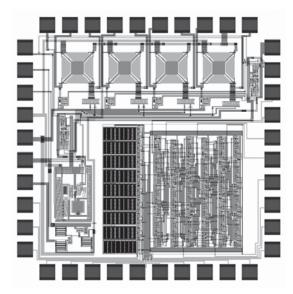

• A monolithic CMOS four element gas sensor VC was designed and submitted for fabrication. The design includes both analog and digital integrated circuits. The digital part of the circuit has an 8-bit analog-to-digital converter (ADC). The objective of the design is to make it compatible with the SoC design methodology.

Layout of the four element gas sensor VC with analogto-digital control.

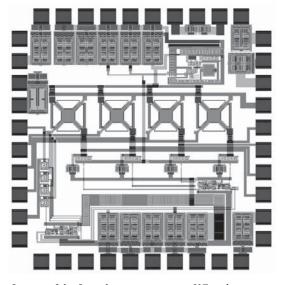

• The four element gas sensor VC was electrically characterized. The performance of the 8-bit ADC superceded the gas sensor VC design requirements. • An initial design of a four element gas sensor VC with electrostatic discharge (ESD) protection was implemented in 1.5 micron standard CMOS technology.

Layout of the four element gas sensor VC with electrostatic discharge (ESD) protection circuitry.

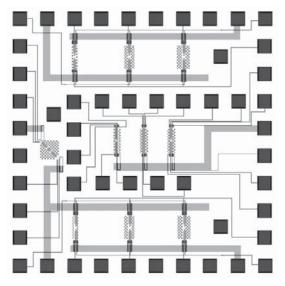

• New microhotplate test structures were designed and fabricated to improve thermal efficiency and their feasibility to be fabricated in the CMOS sub-micron technology.

New microhotplate test structures layout.

### FY OUTPUTS

#### COLLABORATIONS

University of Maryland, Metrology for multi-technology System-on-a-Chip (SoC)

#### **RECENT PUBLICATIONS**

M. Y. Afridi, A. R. Hefner Jr., D. W. Berning, C. H. Ellenwood, A. Varma, B. Jacob, S. Semancik, "MEMSbased Embedded Sensor Virtual Components for SoC," Solid State Electronics, Vol. 48, pp. 1777-1781 (24-JUN-2004)

M. Y. Afridi, A. R. Hefner Jr., D. W. Berning, C. H. Ellenwood, A. Varma, B. Jacob, S. Semancik, "MEMS-based Embedded Sensor Virtual Components for SoC," 2003 International Semiconductor Device Research Symposium, pp. 500-501 (25-NOV-2003)

M. Y. Afridi, J. S. Suehle, M. E. Zaghloul, D. W. Berning, A. R. Hefner Jr., R. E. Cavicchi, S. Semancik, C. B. Montgomery, C. J. Taylor, "A Monolithic CMOS Microhotplate-based Gas Sensor System," IEEE Sensors Journal, Vol. 2, No. 6, pp. 644-655 (01-DEC-2002)

## Power Semiconductor Device and Thermal Metrology

#### GOALS

The goals of the project are to (1) develop electrical and thermal measurement methods and equipment in support of the development and application of advanced power semiconductor devices and (2) develop advanced thermal measurements for characterizing integrated circuits (ICs) and devices.

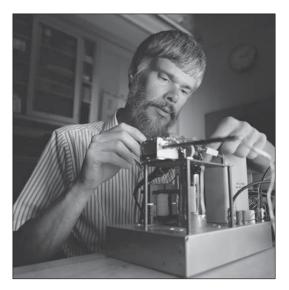

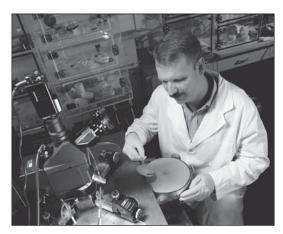

David Berning measuring silicon carbide diodes using NIST-developed, specialized equipment. Copyright Robert Rathe

#### **CUSTOMER NEEDS**

There are significant technical requirements for more efficient, higher voltage power semiconductor devices. The application needs range from more efficient power supplies for computers and consumer appliances, to electric automobile power converters, to more efficient long distance high voltage power transmission. Rapid technical advances are occurring in the development of new power semiconductor materials and designs to address these needs. With the introduction of these new materials and designs comes new requirements for characterizing the performance and reliability of the fabricated devices.

The most exciting, and potentially revolutionary, development in this area is the rapid progress in the development of wide band-gap semiconductor materials for power semiconductor devices. Wide band-gap semiconductors such as silicon-carbide (SiC) have long been envisioned as the material of choice for next-generation power devices. Recent advances in single crystal SiC and fabrication technology have ushered in a new era of wide band-gap power semiconductor devices. This has led to the introduction of SiC power Schottky diode products in the 400 V to 1200 V range and led to the development of High-Voltage, High-Frequency (HV-HF) power devices with 10 kV, 15 kHz power switching capability.

Several industry and government programs are currently underway to accelerate the development and application insertion of SiC power semiconductor devices. The goal of the DARPA Wide-Band-gap Semiconductor Technology High Power Electronics Program (WBST-HPE) is to develop half-bridge modules with 15 kV, 110 A, 20 kHz capability in the next few years. The emergence of HV-HF devices with such capability is expected to revolutionize utility and military power distribution and conversion by extending the use of Pulse Width Modulation (PWM) technology, with its superior efficiency and control capability, to high voltage applications.

The Electric Power Research Institute (EPRI) also identified the benefits of HV-HF semiconductor technology, which include advanced distribution automation using solid-state distribution transformers with significant new functional capabilities and power quality enhancements. In addition, HV-HF power devices are an enabling technology for alternative energy sources and storage systems. The emergence of HV-HF power devices presents unique challenges in metrology and specification of device electrical and thermal requirements.

While overcoming thermal limitations has always been at the forefront of power semiconductor technology, this has only come to the fore recently in CMOS-based microelectronic circuits. The major issues include: (1) power levels in CPUs have reached the same levels as in power devices; (2) power density nonuniformities are leading to hot spots in microprocessors as well as power ICs; (3) new materials with different thermal properties are being introduced; (4) many new and future technologies (*e.g.*, SOI, 3-D integration) tend to isolate power dissipating elements thermally; and (5) shrinking dimensions and increasing frequency of ICs are causing significant power dissipation in Technical Contact: Allen R. Hefner, Jr.

Staff-Years (FY 2004): 2.25 professionals 3.25 guest researchers

"In 2004, Dr. Calvin Carter of Cree Inc. received the US National Medal of Technology from President George W. Bush for: 'his exceptional contributions to the development of Silicon Carbide wafers, leading to new industries in wide band-gap semiconductors and enabling other new industries in ... more efficient/compact power supplies, and higher efficiency power distribution/transmission systems.""

"[The Project] ... continues to lead industry needs by providing state-of-the-art capability for the measurement of unique power device characteristics at critical operating conditions."

> NRC Panel Report, An Assessment of the National Institute of Standards and Technology Measurement and Standards Laboratories. Fiscal Year 2003

the interconnects. In order to address these issues, reliable methods for measuring the temperature distribution in ICs and power devices are required.

#### **TECHNICAL STRATEGY**

The strategy is to support the measurement infrastructure of the semiconductor industry by developing and evaluating measurement methods and techniques where suitable ones do not exist for characterizing critical electrical and thermal properties of devices and ICs. This includes electrical, thermal, and safe operating limit characterization, establishing performance metrics, and developing methods for extracting device model parameters to aid in application insertion. NIST is taking a lead role in developing the device metrology and performance metrics necessary for both the DAR-PA and EPRI efforts and the new industries envisioned by these programs. NIST is also pioneering electrical and thermal measurement methods for HV-HF devices and advanced thermal metrology for high density ICs.

#### PERFORMANCE, RELIABILITY, AND APPLICATION CHARACTERIZATION FOR DARPA-WBST-HPE DEVICES AND MODULE PACKAGES

A major driving force spearheading the development of HV-HF power devices is the ongoing DARPA WBST-HPE program focused on developing the technology deemed necessary to enable Solid State Power Substations (SSPS) for future Navy warships. Current distribution approaches being considered for the next generation of aircraft carriers and destroyers employ a 13.8 kVAC power distribution that is stepped down to 450 V AC by using large (6 ton and 10 m<sup>3</sup>) 2.7 MVA transformers. Substantial benefits in power quality enhancement, advanced functionality, size, and weight are anticipated by replacing this transformer with an all solid state design. NIST played a key role in WBST-HPE Phase 1 and has been selected to be the exclusive device and package evaluation and metrology lab for the \$50 M Phase 2-3 program for 2005 through 2008.

#### METROLOGY FOR MAPPING SIC POWER BIPOLAR DEVICE DEGRADATION

Although significant progress has been made in improving the quality of the SiC starting material and the fabricated devices, a major concern for bipolar structures is an observed degradation in the electrical characteristics over time. The degradation occurs from latent defects such as Basel Plane Dislocations that result in the formation and growth of stacking faults activated by excess carrier recombination. The defects cause severe current nonuniformities to occur, resulting in on-state voltage, switching, and thermal performance degradation.

**DELIVERABLE:** Develop automated stress and degradation monitoring systems to assess degradation of SiC devices after 10,000 hours of operation.

**DELIVERABLE:** Utilize NIST one-of-a-kind high speed thermal image measurements to characterize SiC power diode conduction uniformity performance before and after stress conditions and correlate results with light emission stacking fault measurements (with NRL).

#### METROLOGY FOR NONDESTRUCTIVE Switching Failure

Power devices undergo their greatest electro-thermal stress under switching conditions. There are a number of known catastrophic failure mechanisms that occur as a device is switched off with an inductive load. NIST has developed a nondestructive system to test for the failure limits under inductive switching, has done extensive research on Si device failure limits, and will extend that work to include SiC power devices.

**DELIVERABLE:** Perform unclamped inductive switching measurements for SiC MOSFETs and IGBTs produced by DARPA WBG program.

#### CIRCUIT SIMULATOR MODELS FOR SIC Power Switching Devices

Parameter extraction is a critical component in developing and using device models in circuit and system simulations and in establishing performance benchmarks for new device technologies. For new devices, not only must new models be developed, but methods must be modified and new ones developed for extracting the parameters for the models.

**DELIVERABLE:** Utilize NIST IMPACT model parameter extraction tools to characterize SiC power MOSFETs and IGBTs introduced by the DARPA WBST-HPE program.

#### DEVELOP THERMAL METROLOGY FOR Power Semiconductor Package and Cooling System

The cooling systems for power electronic devices and modules are often quite sophisticated and complex. In evaluating the efficiency and effectiveness of cooling systems, it is critical to be able to measure the temperature of a packaged chip accurately during actual operation. This means that temperature measurement methods are needed that use a chip electrical parameter as the thermometer. Also, validated electro-thermal device models are needed to speed the system design. New HV-HS semiconductor devices present new packaging challenges and technologies that must be evaluated for high temperature performance, die attack voiding, and thermal cycling capability.

**DELIVERABLE:** Perform thermal cycling and thermal shock experiments on DARPA WBST-HPE program devices. Use unique NIST high current IGBT TSP system and high speed thermal imaging system to identify die attach and DBC integrity before and after thermal stress.

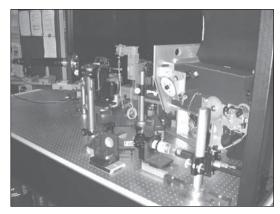

#### HIGH-SPEED THERMAL IMAGE MICROSCOPY FOR ON-CHIP TEMPERATURE

A limitation of commercially available infrared (IR) thermal imaging systems is their inability to make high speed transient measurements. NIST has modified a commercial IR system to be able to make such high speed temperature maps of a device surface with a better than 1  $\mu$ s time resolution and a spatial resolution of about 15  $\mu$ m to 20  $\mu$ m. Current work involves enhancing the performance and applicability of this unique test method and exploring the potential for addressing critical metrology issues in advanced digital integrated circuits and power devices.

**DELIVERABLE:** Develop procedure for coating chips with thin high emissivity paint and characterize the performance for high speed IR thermal metrology.

**DELIVERABLE:** Apply high speed thermal imaging system to characterize the performance of advanced digital integrated circuits including dynamic thermal performance enhancement (with UMD).

#### ACCOMPLISHMENTS

• Extended capabilities of IMPACT parameter extraction software. The capabilities of the parameter extraction software, IMPACT, were extended to include MOSFETS (in addition to IGBTs) and three polytypes of SiC material (in addition to Si). This was done in collaboration with the University of Puerto Rico, Mayaguez, and two SURF (Summer Undergraduate Research Fellow) students.

• *High voltage curve tracer and reverse recovery systems.* The development of a 25 kV variable pulse width curve tracer for both 2 and 3 terminal devices was completed. Safety protection and an interlock system have been tested and qualified. A high voltage reverse recovery test system with 3 kV, 15 A capability was also developed. These systems are critical components

in the SiC power semiconductor device metrology tasks.

• Chip temperature measurements for power multichip modules. Developed test system and procedures for thermal characterization of Integrated Power Electronic Module (IPEM) and developed electro-thermal model and validation for IPEM. Applied this new measurement and modeling method to commercial high power IGBT half bridge module, commercial six pack IGBT module, and prototype NSF Center for Power Electronic Systems IPEM.

• *High speed transient infrared thermal imaging system.* The high-speed transient imaging capability has been extended to include a burst method. This feature has been found to be very useful in measuring current uniformity of SiC power devices before and after degradation without degrading the device during the measurement.

• Played a major role in planning and evaluating progress of DARPA Wide Bandgap Power Device program. Developed the metrology, measured device deliverables to government from DARPA contractors, and used NIST data to provide assessment of program to DARPA director.

• Initiated new program with EPRI to develop solid state power distribution transformers using ultra high voltage semiconductor devices. The goal is to replace all existing power distribution transforms with Intelligent Universal Transformers that provide better control of the power grid, provide power factor correction at point of use, improve power quality, and enable plug-and-play insertion of alternate energy sources. NIST aided in mapping existing power semiconductor technologies for this application and in establishing an EPRI road map for development of ultra-high-voltage semiconductor devices.

• Played a major role in initiating and planning a new DARPA/Navy SiC shipboard power distribution program. The program involves insertion of power distribution technologies enabled by ultra-high-voltage semiconductor devices into next generation more electric Navel carrier, destroyer, and submarine platforms.

• Completed development of SiC power MOSFET model and completed development of IMPACT extraction tools for SiC power device model parameter extraction. Performed parameter extraction for SiC MOSFETs produced by DARPA WBG program and validated simulations.

#### FY OUTPUTS

#### COLLABORATIONS

Avanti Inc., Parameter extraction for IGBT library component models

Avanti Inc./University of Arkansas, SiC power device modeling

Avanti Inc./UPRM, Characterization and modeling of electronic packages for thermal model library component models

NIST Division 812, Electronic Materials Characterization Project/Advanced MOS Device Reliability and Characterization Project, Benchmarks for quantummechanical device simulation

NIST/CREE, Development of SiC MOSFET electrothermal model

Participants for DARPA contract (including NRL, ARL, Virginia Tech, CREE, University of Arkansas, Rockwell, etc.), Wide bandgap power device program

Rockwell Science Center/NIST, Development of SiC transistor models

University of Maryland, Metrology for multi-technology System-on-a-Chip (SoC)

Virginia Polytechnic Institute and State University, SiC power device utilization

#### **EXTERNAL RECOGNITION**

Allen R. Hefner, elected IEEE Fellow "for contributions to the theory and modeling of power semiconductor devices"

#### **RECENT PUBLICATIONS**

R. Singh, A. R. Hefner Jr., "Reliability of SiC MOS Devices," Journal of Solid-state Electronics, Vol. 48, No. 10-11, pp. 1717-1720 (24-JUNE-2004)

T. R. McNutt, A. R. Hefner Jr., A. Mantooth, J. Duliere, D. W. Berning, R. Singh, "Silicon Carbide PiN and Merged PiN Schottky Power Diode Models Implemented in the Saber Circuit Simulator," IEEE Trans. Power Electronics, Vol. 19, No. 3, pp. 573-581 (01-MAY-2004)

D. W. Berning, J. V. Reichl, A. R. Hefner Jr., M. Hernandez, C. H. Ellenwood, J. Lai, "High Speed IGBT Module Transient Thermal Response Measurements for Model Validation," Proc., IEEE Industry Applications Society (IAS) Annual Meeting, Oct. 12-16, 2003, Salt Lake City, Utah, pp. 1826-1832 (12-OCT.-2003)

X. Huang, P. Elton, J. Lai, A. R. Hefner Jr., D. W. Berning, S. Chen, T. Nehl, "EMI Characterization with Parasitic Modeling for a Permanent Magnet Motor Drive," Proc., IEEE Industry Applications Society (IAS) Annual Meeting, Oct. 12-16, 2003, Salt Lake City, Utah, pp. 416-423 (12-OCT.-2003)

T. R. McNutt, A. R. Hefner Jr., A. Mantooth, D. W. Berning, S. Ryu, "Silicon Carbide Power MOSFET Model and Parameter Extraction Sequence," Proc., Power Electronics Specialist Conference, Power Electronics Specialist Conference, Acapulco, Mexico, 10 p. (11-JUNE-2003)

R. Singh, K. G. Irvine, D. C. Capell, J. T. Richmond, D. W. Berning, A. R. Hefner Jr., J. W. Palmour, "Large Area, Ultra-high Voltage 4H-SiC PiN Rectifiers," IEEE Trans. Electron Devices, Vol. 49, No. 12, pp. 2308-2316 (01-DEC.-2002)

R. Singh, D. C. Capell, A. R. Hefner Jr., J. Lai, J. W. Palmour, "High-Power 4H-SiC JBS Rectifiers," IEEE Trans. Electron Dev., Vol. 49, No. 11, pp. 2054-2063 (01-NOV.-2002)

J. J. Rodriguez, J. V. Reichl, Z. R. Parrilla, A. R. Hefner Jr., D. W. Berning, M. Velez-Reyes, J. Lai, "Thermal Component Models for Electro-Thermal Analysis of Multichip Power Modules," Proc., 2002 IEEE Industry Application Society, IEEE Industrial Applications Society Meeting, Oct. 13-18, 2002, Pittsburgh, Pennsylvania, pp. 234-241 (24-OCT.-2002)

## MICROELECTROMECHANICAL SYSTEMS

#### GOALS

The MicroElectroMechanical Systems (MEMS) Project works to apply micro and nanofabrication technologies (MNT) to advance the state of the art of single molecule measurements, single cell measurements, and DNA separations for forensic applications. In addition, we support domestic and international MEMS standardization by working with standards groups to develop and provide the MEMS industry with test structures, test methods, measurement standards, and standard manufacturing practices.

#### **CUSTOMER NEEDS**

MEMS technology continues to mature, resulting in growing opportunities for U.S. industry, which in turn results in an increasing need for measurement standards and also for new opportunities for research. Our project aligns its new efforts with NIST's core mission and with NIST's strategic focus areas in biosystems and health, and nanotechnology. As a result, the MEMS Project has developed four main focus areas: single molecule measurements, bioelectronics, DNA separations for forensic applications, and MEMS standardization.

#### SINGLE MOLECULE MANIPULATION AND MEASUREMENT

The biotechnology and healthcare industries require measurements of large sample arrays as part of their combinatorial approach to disease recognition and drug development. For example, manufacturers of technologies such as DNA and protein arrays are striving to make larger arrays that can more efficiently support larger combinatorial measurements. As the size of the sensors is decreased, the sample size (and hence the number of molecules in the sample) also decreases. Since biological molecules are expected to have variation in their behavior, a question arises concerning whether the statistical variation of biological molecules will affect the accuracy of those measurements; e.g., is there a minimum sample size that is required to yield a result that is comparable to traditional ensemble measurements. The ability to measure the structure and function of single biomolecules will yield the statistical behavior of their large populations.

#### **BIOELECTRONICS**

Our vision of bioelectronics is interfacing integrated circuit technologies to biological systems. Experiments in cell biology have been virtually unchanged for many decades, involving manual handling of cell culture flasks, changing the cell media (feeding the cells), exposing the cell culture to a compound of interest, and observing cell response and viability using a microscope. For this reason, cell biology experiments are typically very time consuming and labor intensive. Recently, the trend has been to conduct studies that involve large arrays of small cell cultures by automating these steps as much as possible using robotic instrumentation, but the experiments are still essentially the same. A true paradigm shift is to utilize microand nanofabrication technologies to perform these experiments on single cells or small cell clusters in continuous flow microfluidic systems with integrated microsensors and MEMS.

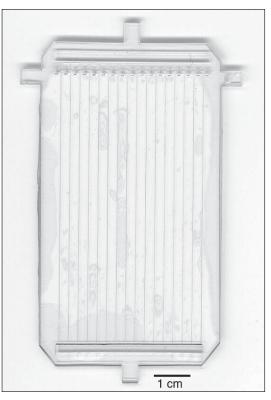

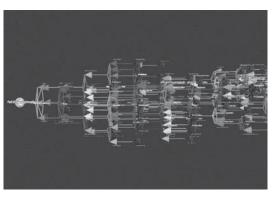

Prototype 16 channel device for DNA fingerprinting.

**Technical Contact:** Michael Gaitan

Staff-Years (FY 2004): 4.5 professionals 1.0 post doc 4.75 guest researchers

#### **DNA SEPARATIONS FOR FORENSIC APPLICATIONS**

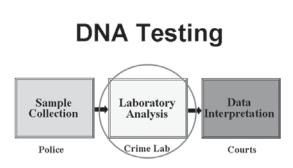

The Department of Justice recognizes an urgent need to improve the efficiency, speed, and accuracy of DNA testing in order to alleviate a growing backlog of forensic DNA testing for criminal cases. Results of DNA testing have become a critical component of criminal investigations and are often used as evidence in court proceedings. NIST has played a key role in the validation and standardization of forensic DNA testing protocols over the past decade that has facilitated a growing acceptance of this type of analysis for criminal investigations.

Microfluidic technology is a promising alternative to current capillary-based techniques due to its great potential to miniaturize, simplify, integrate, automate, and multiplex the analysis with higher throughput and speed. This technology has already shown that it is the next revolution in DNA technology, with analysis often complete in ten percent of the time required for more traditional capillary technology. Although DNA analysis systems based on microfluidics technology have been recently commercialized, these systems do not meet the specific needs of the forensic community due to poor separation resolution of the relatively long fragments (on the order of 100 bps to 400 bps) as well as incompatibility with the standard test procedures.

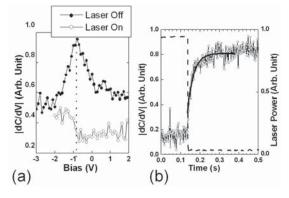

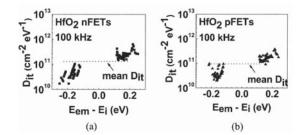

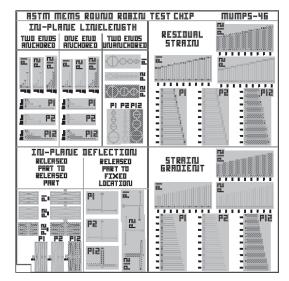

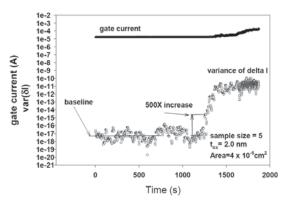

#### MEASUREMENTS AND STANDARDS FOR MEMS