A11105 696904

NBS PUBLICATIONS

U.S. DEPARTMENT OF COMMERCE

NBSIR 87-3568

National Bureau of Standards

# Institute for Computer Sciences and Technology

CMRF

COMPUTER MEASUREMENT RESEARCH FACILITY FOR HIGH PERFORMANCE PARALLEL COMPUTATION

# On the Measurement of Fault-Tolerant Parallel Processors

John W. Roberts Alan Mink Robert J. Carpenter

Advanced Systems Division

May 1987

Sponsored by the Defense Advanced Research Projects Agency under ARPA order number 5520, July 23, 1985, and July 28, 1986.

-QC 100 .U56 #87-3568 1987 C.2

• ~

Research Information Center National Bureau of Standards Gaithersburg, Maryland 20899

# ON THE MEASUREMENT OF FAULT-TOLERANT PARALLEL PROCESSORS

NBSC OC100 - USG W. 87-3568 1987 C. 2

John W. Roberts Alan Mink Robert J. Carpenter

Advanced Systems Division Institute for Computer Sciences and Technology National Bureau of Standards Gaithersburg, MD 20899

Preparation of this report was sponsored by the Strategic Computing Initiative Defense Advanced Research Projects Agency 1400 Wilson Boulevard Arlington, Virginia 22209 ARPA Order No. 5520, July 23, 1985, as amended July 28, 1986.

The work reported here was performed at the National Bureau of Standards (NBS), an agency of the U.S. Government, and is not subject to U.S. copyright. The identification of commercial products in this paper is for clarification of specific concepts. In no case does such identification imply recommendation or endorsement by NBS, nor does it imply that the product is necessarily the best suited for the purpose.

U.S. Department of Commerce, Malcolm Baldrige, Secretary

National Bureau of Standards, Ernest Ambler, Director

May 1987

-----

.

s.

### TABLE OF CONTENTS

## Page

| 1. | Backgro | ound                                                                                                                                                                            | 1      |

|----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|    | 1.1     | The need for fault-tolerant processing                                                                                                                                          | 1      |

|    | 1.2     | Approaches to achieve fault tolerance                                                                                                                                           | 2      |

|    |         | <ul> <li>1.2.1 The assumptions of this report</li> <li>1.2.2 Loosely-coupled fault-tolerant architectures</li> <li>1.2.3 Tightly-coupled fault-tolerant architectures</li></ul> | 3<br>4 |

|    | 1.3     | Stages of Fault-tolerant Operations                                                                                                                                             | 5      |

|    | 1.4     | I/O in Fault-tolerant Systems                                                                                                                                                   | 5      |

| 2. | Fault D | etection Measurement Techniques                                                                                                                                                 | 6      |

|    | 2.1     | Detection of errors                                                                                                                                                             | 7      |

|    |         | <ul> <li>2.1.1 Errors in the storage and transmission of data</li> <li>2.1.2 Errors in the transformation of data</li> <li>2.1.3 Detection of only major failures</li> </ul>    | 7      |

|    | 2.2     | Induced Faults for Testing                                                                                                                                                      | 8      |

|    | 2.3     | Simulation vs. Emulation of Faults                                                                                                                                              | 8      |

|    | 2.4     | Direct Observation of Faults and Fault Detection                                                                                                                                | 9      |

|    | 2.5     | Indirect Methods of Observation                                                                                                                                                 | 9      |

|    | 2.6     | Observation of Software Fault Detection Techniques                                                                                                                              | 11     |

| 3. | Measure | ement of Fault Detection                                                                                                                                                        | 12     |

|    | 3.1     | Explanation of measurement entries                                                                                                                                              | 12     |

|    |         | 3.1.1 Sample measurement entry                                                                                                                                                  | 12     |

|    | 3.2     | Detection of transmission errors                                                                                                                                                | 14     |

|    |         | <ul><li>3.2.1 Inter-module communication errors</li><li>3.2.2 Address errors</li></ul>                                                                                          |        |

|    | 3.3     | Detection of data storage errors                                                                                                                                                | 16     |

|    |         | <ul> <li>3.3.1 Faults in processor registers, transient</li></ul>                                                                                                                               | 17<br>18 |

|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|    | 3.4     | Faults in data transformation elements                                                                                                                                                          | 20       |

|    |         | <ul> <li>3.4.1 Detection of faults within operating processors</li></ul>                                                                                                                        | 23       |

|    | 3.5     | Faults in computers in loosely-coupled systems                                                                                                                                                  | 27       |

|    |         | 3.5.1 Detection of faults at the component-computer level                                                                                                                                       | 27       |

|    | 3.6     | Faults in I/O systems                                                                                                                                                                           | 28       |

| 4. | Fault R | ecovery Techniques                                                                                                                                                                              | 29       |

|    | 4.1     | Views of Fault Recovery                                                                                                                                                                         | 29       |

|    | 4.2     | Fault Recovery Methods                                                                                                                                                                          | 30       |

|    |         | <ul> <li>4.2.1 Recovery in loosely coupled systems</li> <li>4.2.2 Recovery in tightly-coupled systems</li> <li>4.2.3 Isolating faulty devices</li> <li>4.2.4 I/O recovery techniques</li> </ul> | 33<br>33 |

|    | 4.3     | Evaluation of Fault Recovery                                                                                                                                                                    | 34       |

| 5. | Measure | ement of Fault Recovery                                                                                                                                                                         | 36       |

|    | 5.1     | Systems Using Software Recovery                                                                                                                                                                 | 37       |

|    |         | <ul> <li>5.1.1 Overhead in normal operation</li></ul>                                                                                                                                           | 38<br>38 |

|    |         | 5.1.4 Faults in processor registers                                                                                                                                                             |          |

|    |         | 5.1.6 Faults in cache memory                                                                                                                                                                    |          |

|    |         | 5.1.7 Faults within processors                                                                                                                                                                  |          |

|    |         | 5.1.8 Faults within coprocessors and controllers                                                                                                                                                | 41       |

|    |         | 5.1.9 Faults at the (processor) board level                                                                                                                                                     |          |

|    |         | 5.1.10 Computer faults in loosely-coupled systems                                                                                                                                               | 42       |

|    | 5.2     | Hardware Recovery from Faults                                                                                                                                                                   | 42       |

| 6. | Summa   | ry                                                                                                                                                                                              | 43       |

| 7. | Referen | ces                                                                                                                                                                                             | 44       |

#### ON THE MEASUREMENT OF FAULT-TOLERANT PARALLEL PROCESSORS

#### John W. Roberts Alan Mink Robert J. Carpenter

A number of measurement techniques can be used to determine how well computers detect and recover from faults. In addition to qualitative measures, quantitative measures can be obtained relating to fraction of faults detected and corrected, recovery time, and degradation of performance during and after recovery.

Key words: Computers; Fault detection effectiveness; Fault recovery effectiveness; Fault tolerant; Performance measurement.

#### 1. Background

Fault tolerance in a computer system is the ability to detect erroneous states in computations or in hardware, and to deal with these errors so that "correct" operation can continue. While limited capability for error detection and correction is commonplace, a much smaller set of computer systems detects and correctly handles errors with a high degree of assurance. This smaller set, known as fault-tolerant systems, applies various techniques to meet the specialized needs of a wide range of users.

#### **1.1** The need for fault-tolerant processing

The principal need for fault tolerance arises in the areas of the solution of large problems, control systems demanding high reliability, and applications demanding availability.

Large Scale applications are those which use enormous amounts of computation (e.g., weather forecasting and three-dimensional fluid flows), and thus require long run times. A fault-tolerant system which is good at both detecting and recovering from errors is virtually a necessity for the solution of large-scale problems that have long running times, with some assurance that the results are correct. As an example, consider a system which has a normal error rate of one per billion operations. If an attempt is made to run a program requiring one hundred billion operations on this machine, the results are almost sure to be incorrect. Comparison of the results from multiple runs can show errors, but can not be used to determine which are the correct results unless the program is run many times. In this case, it is important not only that the system be very good at detecting errors, but also that it be able to continue operation after the detection of errors, without having to restart programs from the beginning.

**High-reliability** applications are those for which it is important that the system remain functional as long as possible in the presence of hardware failures. These applications include manufacturing process controllers, and aircraft and spacecraft control systems. For some of the functions of these systems, such as the processing of incoming sensor information, a loss of small amounts of incoming data may not be harmful as long as overall operation is able to continue. For these uses, mean time between system failures (MTBF) and mean time to next failure (MTTF) are the parameters of greatest importance.

High-availability systems, such as telephone switching centers, strive to compensate for hardware failures in order to minimize the fraction of the time that the system is unavailable because it is awaiting repairs or engaged in the fault recovery process. The parameters of interest are mean time between failures and mean recovery/repair time. Reduced-level performance may be available during recovery, and if so should be characterized. Such systems feature redundancy of many or all components, and may allow on-line repair or replacement of failed components.

The original design of any particular fault-tolerant system determines to what degree it incorporates error detection and recovery facilities. Since fault tolerance always exacts a cost in price or performance, a potential user should search for a system that conforms adequately to the needs of the intended tasks. If applications that do not require fault tolerance are also targeted for such an architecture, estimates should be made of the penalties (cost, performance, etc.) that may be incurred. Development of measurement techniques to determine the performance of fault-tolerant systems will aid users in this search, and also help manufacturers to categorize their machines in a uniform manner.

#### **1.2** Approaches to achieve fault tolerance

Current approaches to fault-tolerant computing are based on redundancy. Redundancy allows detection of malfunctions (physical errors), but usually cannot detect design errors, which are replicated in each redundant component. Malfunctions are assumed to occur in some random manner not affecting all copies. Redundancy is not a viable approach to detection of software faults, since software logic faults will exist in each of the duplicate units. Most software reliability efforts are directed toward fault avoidance, concentrating on aspects of design and implementation (e.g., design reviews, design specifications, testing, etc.). Detection and correction of software errors at execution time doesn't enter this fault avoidance model because machine operation (at software design time) is assumed correct.

One approach to fault tolerance which *does* address design errors, and therefore includes software errors, is based on diversity [AVIZ84]. For diversity in software, independent organizations implement similar but distinct versions of the software from the same specification. Both versions then execute simultaneously while their outputs are compared. A software fault (in specification, design or implementation) is indicated if the outputs differ. This approach does not guarantee that both versions will not produce identical erroneous results. At present, a major problem in fault-tolerant systems centers about the decision algorithm which is responsible for the selection of the correct output (if any). In the space shuttle [ZORP85], redundancy is used to detect malfunctions in the four primary processing units, while diversity is used in the fifth, secondary processing unit (which has the same hardware design, but a different software design), as a software consistency check on the primaries.

**1.2.1 The assumptions of this report.** Henceforth in this paper, *fault-tolerant computing* is understood to refer to the detection and correction of hardware faults (physical failures), rather than faults caused by mistakes in logical or software design. Our baseline model of fault-free operation is a program (either correct or incorrect) and computer hardware operating correctly to execute that program.

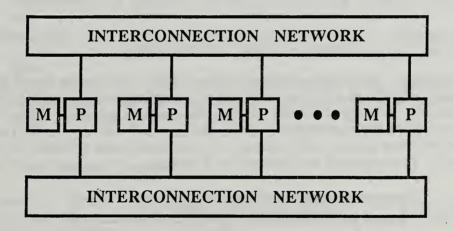

1.2.2 Loosely-coupled fault-tolerant architectures. Loosely-coupled fault-tolerant architectures are generally made by coupling a number of fairly conventional complete computers into a system. Alternate communication paths must be provided between all members of the systems, and the individual computer designs must be enhanced to include some means to detect erroneous operation and localize its effects. Communications between members of the system are handled by *messages*, with a protocol to detect any errors in the exchange of messages. The responsibility for managing the recovery from faults in the computers is assigned to the software system. Figure 1 illustrates such a system.

Figure 1 - Loosely-coupled system.

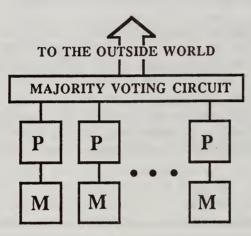

1.2.3 Tightly-coupled fault-tolerant architectures. Tightly-coupled systems require specially-designed computing subunits. Shared memory is used, and the hardware must be designed to avoid erroneous transfers to memory. These systems frequently use multiply redundant processors operating in a lock-step mode, with some sort of voting or selection technique to assure real-time selection of the correct data. Dual *mirrored* memory units are used with special schemes to assure that the correct data has been transferred. A mirrored memory system uses two (or more) copies of each memory location for redundancy. Data must be correctly altered in one instance of the memory before the same change can be allowed in the other (*mirror*) instance(s). Error-checking is again used when altering the second instance. Figure 2 illustrates such a system.

Figure 2 - Tightly-coupled system.

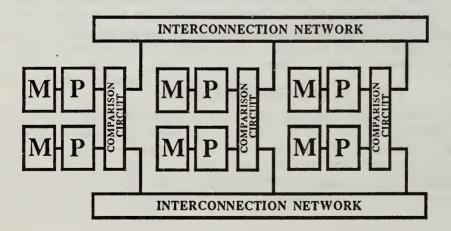

1.2.4 Mixed systems. Some manufacturers choose tight coupling to detect faults, but omit the greater redundancy required for hardware correction of the faults. These systems use recovery techniques similar to loosely-coupled systems. They therefore represent a mixture of the architectures shown in Figures 1 and 2. (Doubly) redundant units are used to detect faults. Additional sets of components are included to allow migration of tasks. This approach is illustrated in Figure 3.

Figure 3 - Mixed-architecture system

#### **1.3 Stages of Fault-tolerant Operations**

For the purposes of this report, we have divided fault-tolerant operations into two stages: detection and recovery. Other taxonomies, such as [SIEW84], have chosen a finer division:

- confinement the system attempts to localize the effects of faults so that recovery will be possible.

- detection the faulty operation is detected.

- masking operations are performed redundantly, to detect and mask erroneous results.

- retry errors are detected and operations retried until an error-free result is obtained.

- diagnosis the specific fault involved is diagnosed to allow reconfiguration or repair.

- reconfiguration required (automatic) reconfiguration is used to eliminate the faulty portion of the hardware.

- recovery the state of the machine is backed up to that most recently recorded before the error, and the intervening operations are repeated. This may require the correction of erroneous intermediate results.

- restart the system completely restarts the program from the beginning. This is a drastic recovery technique suitable for batch or transaction systems.

- repair since fault-tolerant machines can only tolerate a limited number of simultaneously defective parts, any defective parts are repaired or replaced automatically or by service personnel before the tolerance limit is exceeded.

- reintegration once a part in a high-availability system is repaired or replaced, it must be reintegrated into the system without disturbing the jobs in progress.

- reporting after a fault is detected, a report is made to the user both to help in evaluation of the fault handling of the system and to alert the user to losses of redundancy in the system.

#### **1.4 I/O in Fault-tolerant Systems**

The protection of I/O (input/output) operations poses several unique problems in the design of fault-tolerant systems. These difficulties are due largely to the differences between I/O and other types of data transfers.

The responsibilities of a fault-tolerant I/O system are related to what the designer considers the nature and extent of such a system to be. Communications with other devices and the interface with the users would normally be considered part of I/O. If the fault-tolerant system is made up of a group of loosely-coupled computers, however, communications between the computers within the system would probably not be considered I/O. Similarly, some would consider disk and tape access as I/O, while others would not. One possible working definition is that an interaction between two integrated, self-sufficient entities would be classified as I/O, while interactions within such an entity would not. This definition fits well with the concepts of fault tolerance, since a fault-tolerant system maintains control over a specific area in a community of computational devices, within which it is responsible for detection and correction of faults. The fault-tolerant system is expected to interact with other systems in a correct manner, but it is not responsible for the actions of the other systems. Using this definition, one may be able to visualize a machine designed as a hierarchy of fault-tolerant systems within fault-tolerant systems, with the protected, internal communications at one level regarded as I/O interactions at a lower level.

In general, I/O operations are regarded as the transfer of information in the form of messages in accordance with a specific protocol, which may be implemented chiefly in hardware, but which is usually controlled by a fairly complex software structure. If there is to be any assurance of reliable operation, some handshaking mechanism, which uses attention and acknowledgement signals sent in both directions, must be employed. The capabilities of the handshaking algorithm may vary greatly. A minimal algorithm might simply indicate readiness to receive transfers, with little or no checking of the correctness of the data. A more complex algorithm might check for errors and require retransmissions as needed, but not allow later revisions of transfers or provide highly-reliable acknowledgements. Advanced algorithms might provide for the same degree of controllability as is found for intrasystem transfers, at which point the device with which communications are established could be considered part of the fault-tolerant domain.

Many potential problems with I/O transfers are associated with timing and synchronization. Depending on the transfer protocol and the output device, it may not be possible to reverse the effects of an erroneous output. An input which is lost because of an error or because the receiving device is busy recovering from a fault when the signal comes in may be lost permanently. In contention among several devices for a resource, an accurate record of the current owner may be lost, resulting in overwrite errors or blocking of access to the resource. Damage to software reference tables may cause errors in connections. Consistency, which refers to the maintenance of correct records of resource conditions from the viewpoint of all interested parties, is likely to be compromised by such failures. In order to have reliable I/O operations, a fault-tolerant system must have carefully chosen hardware and software structures that take these problems into account. A sophisticated handshaking algorithm is necessary to insure that data transfers can take place without causing errors in either communicating device.

Other than the unique problems associated with timing and controllability, fault tolerance in I/O transfers bears many similarities to fault tolerance in other operations of the system. Much of what is described for fault detection and recovery for internal operations therefore applies to I/O as well. Issues specific to I/O are also mentioned elsewhere, though a complete description of the issues in I/O fault tolerance is beyond the scope of this paper.

#### 2. Fault Detection Measurement Techniques

The first step in determining the capabilities of a fault-tolerant computing system is to evaluate its fault detection processes. The measurement equipment should be able to determine when faults are detected, and whether or not all significant faults are detected. In order to fully evaluate the detection process, the measurement equipment must independently detect the occurrence of all faults and also observe the detection of faults by the system. Many of the details of the measurement techniques are dependent on the architecture of the system under test.

#### 2.1 Detection of errors

A fundamental problem in the design of fault-tolerant systems is to allow them to detect errors while the system is performing useful work. Different error detection techniques are required for the storage and transmission of data, and for the transformation of data.

2.1.1 Errors in the storage and transmission of data. Since information is not intentionally changed, detection of errors in storage and transmission of data is usually handled by information redundancy. This usually takes the form of error codes which come in a large range of complexity, from simple parity and checksums to Hamming codes, AN codes and polynomial codes (e.g., CRC). These codes can be used to allow all errors of up to n bits to be detected, and all errors of up to k bits to be corrected, where n > k and  $k \ge 0$ . These techniques have been successfully applied to storage devices (e.g., parity for detection or one-bit error correction in primary memories and magnetic tape units) and data transmission mechanisms (e.g., checksums and CRC appended to data packets). While many systems use redundant information for (forward) error correction, some system use the cheaper but slower approach of *retransmission* for correction of data transmission errors.

2.1.2 Errors in the transformation of data. Detection of errors in the portions of a computer system which intentionally transform data is more difficult. This activity is usually associated with the processing units. Since the data is being transformed, addition of redundant information in the form of error detection codes is not generally applicable. The transformation of the error code information does not produce the correct new code to accompany the transformed data. A new error code must be computed from the transformed data, after it is transformed (correctly or incorrectly). Error detection for transformations is usually handled by redundancy (replication) of data transformation devices. With the assumption that errors are caused by random and independent events, multiple components are highly unlikely to be affected in exactly the same manner at the same time. Errors are detected by comparison, which requires only two units (more can be used), whose outputs are compared. An error is detected when there is a difference between the outputs of the the units. If only two units are used, the correct output (if any) is not known and further action must be taken to resolve the problem. If three or more units are compared, majority voting may be used to determine the correct output, as discussed more fully below.

**2.1.3 Detection of only major failures.** If the fault detection is needed only to identify units which have been incapacitated by a catastrophic hard failure (rather than faults which produce erroneous results but allow the unit to continue operation), a simplified detection approach can be taken, based on timeouts [SERL84, ZORP85]. A common technique is for each operating unit (or program) to periodically inform another unit that it is still active. This other unit may be a backup unit or a dedicated monitoring device. If an excessive interval elapses without receipt of this notification, it is assumed that the unit (or program) has failed and a backup strategy is invoked.

#### 2.2 Induced Faults for Testing

In addition to being difficult to implement in a fairly general manner, techniques that make use of only naturally-occurring faults are unsatisfactory as methods for evaluation of the fault detection capabilities of a system. The main drawback lies in the low probability of encountering an adequate number of natural faults of a specific type during the course of the measurement process. Fault-detection tests would therefore take an unreasonably long time to complete if measurement depended on natural faults. This can be avoided if the measurement system, under user supervision, is somehow able to induce, inject, or emulate a comprehensive selection of faults in the system under test. The frequency of occurrence of normally-rare faults can be made high enough to allow the collection of reasonable data on detection and recovery. Knowing when a fault is present is vital to permit the measurement equipment to determine whether the fault is detected by the system being tested.

A drawback of the induced fault method compared to the use of naturally-occurring faults is that there may be little correlation between the distribution and characteristics of the induced faults and naturally occurring ones. This problem can be minimized if an effort is made using theory and experiment to characterize natural faults, and to emulate them with induced faults. Induced faults may also be used to force situations that are considered extremely unlikely but extremely troublesome, to determine whether detection and recovery can take place in these circumstances.

A further difficulty with induced faults is the need to get access to a desired location in the system under test and emulate the desired fault. The techniques available are highly dependent on the architecture of the system tested, and it may not be possible to induce a particular fault. Most of the fault injection techniques used to date involve permanently or temporarily forcing one or a set of signal lines to a fixed logic level, forcing switches open or closed, disabling logic elements or check bit generators, and creating unpredictable faults by putting signal spikes on power supply lines, etc. Faults induced using these methods may bear little resemblance in their characteristics to naturally-occurring faults.

#### **2.3 Simulation vs. Emulation of Faults**

It is not always necessary to induce a real fault. If a false "fault-detected" signal can be introduced into the system, many of the fault isolation and recovery mechanisms can be observed. Such signals may be injected, using hardware drivers, in the control circuitry somewhere above the lowest level of system hardware. It may also be possible to induce these signals using software techniques. High-level error reporting should then occur as expected. Systems which recover by switching out suspected components and later testing them for readmission can be thereby be observed in operation. For the most realistic models of recovery from normal faults, however, it is best to use real faults, whether natural or induced. Real faults must also be used to investigate fault detection and correction at the lowest hardware levels of the machine.

When a fault has been introduced, it is necessary to measure its exact extent and the time of its detection. One must observe the faults and notifications of faults as they appear.

#### 2.4 Direct Observation of Faults and Fault Detection

Observation of the detection of faults is simplest if the system under test provides notification to the outside world whenever a fault has been detected. Many systems, however, are not set up to report faults from which the system recovers without loss of performance (i.e. error correction in memories). Even if notification is available, the type and chronology of the fault may not be reported completely enough for certain measurements, for example collection of statistics on address transformation errors. For many measurements, more direct methods of observation of fault detection are desirable.

A more difficult technique for observing fault detection is to locate internal "fault detected" signals within the system being measured. If the architecture of the particular machine under test permits, probes can be connected to the lines on which these signals are found, and the positive indications recorded. This has the advantage of allowing one to learn of fault detections that would otherwise never be reported outside of the system, and to be more selective in the types of faults reported. One major disadvantage is that intrusive examination of a system is highly dependent on its architecture; thus certain observations may prove to be difficult or impossible. In addition, the desired signal may not exist as such. For instance, a fault-tolerant memory controller may algorithmically correct a single-bit read error without any indication that a fault was detected.

Some types of induced signals, particularly noise on power supplies, create unpredictable faults. An inherent weakness of the above methods is that they rely on fault detection in the system under test itself to identify the types of faults detected. This detection facility may not be perfect, and is itself the subject of many important measurements. The most direct way around this problem is to independently look for faults within the system under test by probing address and data lines, looking at control signals, etc. With compact design and large-scale integration, this approach ranges from difficult to impossible in the general case, but there are some some machines for which it is practical. Increased concern over the importance of testing and measurement could prompt designers of future systems to add features to facilitate direct observation of internal system operation.

#### 2.5 Indirect Methods of Observation

Often it is desirable to observe machine performance for a particular type of fault detection, but no direct method is practical, because of the difficulty of gaining access to the internal components of the system under test. Fortunately, one may still be able to obtain useful results using indirect methods that provide only partial information on the internal functions of the system. These methods include diagnostics along with knowledge of hardware failures, and mathematical modeling.

Diagnostics in this case are user-specified test programs run as jobs on the system being tested, for which the correct results are already known, and designed specifically to isolate permanent hardware failures that result in faults. They may attempt to approximate the programming environment that would be encountered in normal use, or may make heavy use of a specific system component being tested. A given diagnostic program may be used, for instance, to test the arithmetic unit of a processor or the integrity of a local memory. If fault detection and correction are functioning as specified, the only faults thus located may be those which are not detected or reported to the user by the system being tested. In many systems, however, it may be possible for the user to disable fault detection or recovery, thus allowing diagnostic programs to identify nearly all transient and permanent hardware faults of a given type. With this knowledge, the user may be able to run more common programs and obtain reasonable measures for fault detection and correction parameters.

A major difficulty with the use of diagnostics both by system being tested and by the measurement equipment is the response of the diagnostics to transient failures. While permanent failures can remain stable long enough to be detected and often located by the diagnostic programs, this is often not the case for transient failures. A transient failure may appear and cause an error, then disappear before it can be located by the recovery diagnostics. It may appear or disappear during or after the running of a diagnostic program, rendering its conclusions invalid. Since permanent failures do remain to be detected, however, there are many situations in which it is reasonable for the system or the measurement equipment to use diagnostic programs for the detection of hardware failures, as long as the difficulties that can be caused by transient failures are taken into account.

Where it is not possible to obtain complete information on a needed parameter, the application of mathematical models to the information at hand may make it possible to produce a reasonable reconstruction of the data. For instance, suppose the measurement equipment can detect faults of hypothetical type A but not of type B. Mathematical analysis, taking into consideration the architecture of the system under test, suggests that there should be a correlation between faults of types A and B. Tests may be run in order to seek supporting evidence for the correctness of this model. One may then observe the rate, grouping, etc. of faults of type A, and produce a reasonable estimate of the characteristics of faults of type B. It is important to keep in mind that there may be significant factors not taken into account by the model, and that this limits the accuracy or validity of the conclusions that may be drawn. A specific example is an address bus for which faults can be detected only in the upper bits of the address. Since all the address bit signals go through many identical processes, it may be reasonable to assume that the bit error rate on the lower bits is not greatly different from the rate observed on the upper bits. It is necessary to take into account, however, the facts that permanent hardware failures are not necessarily evenly distributed and that there are certain operations that the upper and lower address bits do not have in common, such as cache control and memory management, which can reduce the error correlation among the address signals.

If something is known about the timing of execution in the system under normal conditions, it may be possible to put this information to use in the analysis of corrected but unreported faults. While some fault-tolerant systems are designed with tightlycoupled hardware control with the objective of avoiding any delays from faultcorrection procedures, many other hardware-based systems and all software-based fault-tolerant systems will experience delays as recovery from a fault takes place, and often exhibit a reduced level of performance during recovery. If the time to complete a task with no errors present is well characterized, and if a good estimate for the recovery time is available, then it may be possible from consistently increased execution time to deduce that a number of errors are being detected and corrected. The practicality of this technique depends on the consistency of the normal speed of execution, the length of time required for recovery, and the knowledge that other factors are *not* interfering with execution. This approach seems precarious at best, but it may be possible to apply it to a wider range of systems than other approaches. In certain systems, access to *HALT* or *WAIT* signals that are associated with detection of an error can make the correctness of interpretation of the measurements more certain.

The observations that can be made and the alternative mechanisms that may be available are highly dependent on the architecture of the specific machine under test. Signals that are buried inside the integrated circuits of one system may be available to the outside world in another. Some machines allow the user to control or inhibit the operation of certain internal functions in order to facilitate testing. Such capability can be extremely useful in testing the various features of a fault-tolerant system independently of one another.

#### 2.6 Observation of Software Fault Detection Techniques

A number of fault-tolerant systems make use of software techniques to detect faults. With this method, different tradeoffs are chosen than with hardware detection systems. Hardware design time and hardware investment may be considerably reduced, but software design is likely to be more complicated, and the time spent running fault detection and recovery routines may cause execution to be slower than for systems which use hardware fault detection. In addition, certain types of faults involving shortterm events or the correct execution of routines may be more difficult for the system to detect. Different methods must also be employed to observe the performance of the fault detection mechanisms.

As previously described, the techniques employed for software fault detection include the interchange of signals indicating continued correct operation, periodic synchronization and comparison of intermediate results and/or processor state, and comparison of multiple copies of global variables. In many systems hardware for the detection of faults is also under the control of supervisory processes, such as schedulers which assign multiple copies of tasks to different processors. To varying degrees, these software functions can be controlled by the user. The user may therefore have the opportunity to override the normal operations of the fault detection software in order to better observe the performance of its individual parts.

Since the fault detection process in these systems proceeds at the speed of program execution, observation may proceed at a similar pace. Reporting of faults may very well be one of the functions of the software, or the user may be able to include real-time notification or logging of faults with only a slight penalty to the rate of execution of the fault-tolerant software. If hardware-level observation of software-detected faults is desirable and practical, it is useful to note that fault detection is a major event from the viewpoint of the processor, with signals on address, data, and control lines, which in many systems can be monitored by measurement equipment.

As in the case of hardware fault-detection systems, it is necessary for the measurement hardware to be made aware of faults as they occur, in some way that is independent of system fault detection, in order to be able to evaluate the fault detection mechanism itself. Techniques that rely on hardware fault reporting will not work for software-based systems, because the signals of interest do not exist. To obtain a reasonable estimate of the fault rate, it may be necessary to use the indirect methods previously described, or, preferably, to carefully control the induced faults.

For systems with software-based fault detection, there are several software-oriented options available for induction of faults. It may be possible to make a change in the value of a reference variable that will be interpreted as a fault. Forcing suspension or termination of one of a set of redundant tasks would have a similar effect. It may also be possible in such systems to insert error notices at a higher level in the control structure of the software, to test the upper levels of the fault detection and recovery mechanisms.

#### 3. Measurement of Fault Detection

An abstract model of a computing system might consider all activities of a computer system to consist of logical manipulation of data, storage of data, transfer of data within the computing system, and input/output. Fault detection can therefore be considered as it relates to each of these activities. The problems associated with fault tolerance for I/O operations as compared to internal operations are mentioned here and throughout the paper.

#### 3.1 Explanation of measurement entries

This section of the paper is essentially a list of many of the faults to which a fault-tolerant system may be subject, and a description of ways in which the detection of these faults by the system under test might be evaluated. The faults that will be of principal interest to a given user depend on the architecture of the system, the applications that are anticipated, and the user's interpretation of fault tolerance. The techniques to be employed are similarly a function of these factors. Other fault types and evaluation techniques may be added as needed. An attempt has been made to keep the fault categories fairly general, so they can be applied in a wide range of situations.

#### **3.1.1 Sample measurement entry.**

**Description of fault:** This is a collection of general background information concerning a particular type of fault. Among the descriptions that may be included are the precise the nature of the fault, possible causes of the fault, ways in which the fault can effect system operation, and methods that may be used by the fault-tolerant system to detect this type of fault.

Architectures affected: This is a brief summary or description of the system architectures that are susceptible to this type of fault. In many cases a given architecture will be inherently immune to certain faults, and no further consideration is needed for these faults. The range of architectures considered to be affected by a given fault depends on whether the description of the fault is broadly or strictly interpreted, so the user must decide in advance how to define the set of faults, in order to accurately apply these techniques. Test method: This is a collection of techniques relating to analysis by the measurement equipment of the ability of the system under test to detect faults of this type. In order to perform this function, the measurement equipment must encounter faults, determine that faults of the appropriate type have occurred, derive the needed information concerning the faults, and determine whether the system under test has correctly detected and identified the faults. (Some of the identification activity may be considered part of the recovery process rather than the identification process.) To make sure that errors are encountered, many of the entries include guidelines on possible ways to induce faults. Many fault-injection techniques are not completely controllable, and will produce a range of faults, not just the specific type desired. In any event, it is often necessary for the measurement equipment to directly observe the faults as they appear, in order to determine whether all such faults are detected by the system under test. Where permanent hardware failures are involved, one approach is to run diagnostics to locate the failures, so it is known that a fault will occur whenever a certain operation is attempted. Techniques are given that allow the measurement equipment to determine whether the system under test has detected a fault. If notification is not automatically provided to the outside world, intrusive techniques may be employed.

The principle measurement to be taken for most of these parameters is the incidence of fault detections by the system under test, compared to the incidence of faults as determined by the measurement equipment. This may be presented as a ratio, giving the percentage of faults of this type which the system under test detects or fails to detect (or falsely detects.) It may be more useful, though more complicated, to produce a log describing each detection or failed detection, so that analysis can lead to discovery of specific correctable problems.

There may be some interest in measuring the interval between the appearance of the fault and detection. A useful measurement would be difficult for several reasons. First, the instant at which a fault "occurs" may be subject to considerable debate. Second, the interval to detection will depend mostly on the detection technique employed. For instance, lockstep hardware systems will detect the fault almost immediately if at all. Checkpointing systems may not detect the fault until the next "full" comparison, which may take place over a wide range of intervals from the appearance of the fault. The time to detection may depend only slightly on the type of the fault. Interval measurements are therefore useful mainly as a way of evaluating response characteristics of various detection techniques, and not as a way to characterize performance relative to specific faults.

Special apparatus: This section lists certain types of equipment, including passive probes and various active devices, that may be useful for observation of faults and of fault detection within the system under test.

Limitations of test: There are many situations in which a particular measurement technique may not provide completely satisfactory results. There may be a small known error in the results, or certain types of faults that can not be reliably detected by the measurement equipment. It is important to know the limitations of the tests in order to avoid drawing erroneous conclusions from the results.

#### 3.2 Detection of transmission errors

In the broadest sense, transmission refers to all operations which cause a transfer of data from one location to another with no permanent transformation of the data. This includes all in-system communications, transfers between registers, etc. Since errors in the lowest-level transmissions may not be distinguishable from other circuit errors, there is a tendency to look mainly at higher-level communications in this category.

#### 3.2.1 Inter-module communication errors.

Description of fault: This term refers to errors in the communications links among resource modules and processors in a fault-tolerant system. Such links can be between redundant components jointly performing a fault-tolerant task, or between groups of components performing different parts of a job. If the fault is of a type that prevents normal communications procedures, it should be detected quickly by hardware or software checking. Address errors can often be detected by the handshaking procedure, though certain types of address errors are very difficult to handle, as described in the next entry. Data transmission errors have been widely studied, and may be detected by several means, including the transmission of redundant information.

Architectures affected: The modularity and the communications approach chosen in the design of a particular system determines the types of intermodule communications errors to which it is prone. Systems with separate processor and memory modules will have to deal with memory addressing errors. Module addressing errors can become more of a problem in common-bus systems than in other systems. Links between redundant modules performing identical tasks must allow the modules to compare results effectively without introducing new errors.

Test method: Intermodule errors may be easier to observe than internal communications errors, because there is a better chance that the signal lines will be available for the attachment of probes. In a shared bus or ring system, the signal lines can be checked at several points, to determine whether any errors have been introduced. It may also be possible to induce errors by forcing lines high or low, breaking connections, inverting signals, etc. Direct notification of errors by the system under test is the simplest means of observing fault detections, though these signals may be hard to access.

**Special apparatus:** Probes to observe communication paths and error signal lines (if available) will be needed. To induce errors by driving the signal lines, appropriate drivers will be required. Care must be taken to insure that the system line drivers are not damaged. Signal modification devices may have to be inserted *in series* with signal lines.

Limitations of test: Evaluation of the detection of all possible types of faults is not practical, even using induced faults. Care must be taken in the selection of a suitable subset of faults to be evaluated. The architecture of the system tested may limit the range and accuracy of the tests that may be performed.

#### 3.2.2 Address errors.

**Description of fault:** Because of the heavy emphasis that is traditionally placed on errors in storage and transmission of data, there is a tendency in designing a computer system to use extensive error detection and correction for the data, but to use less protection for the address lines and circuitry. This is unfortunate, since address errors can cause a system failure at least as easily as can data errors. Because of the intricate processes of address generation, translation, transmission, and recognition (many of which *transform* the address information), it is much more difficult to fully protect the address handling process than the data process. However, where there is sufficient motive for reliability, it should be possible, though expensive, to create a reasonable degree of protection from address errors.

Address errors may be caused by incorrect address generation in the processor, incorrect translation in the memory management circuitry, errors in transmission, and incorrect interpretation of the addresses in the addressed devices. This class of faults includes incorrect handling of addresses in cache memory.

The main types of addressing errors are: addressing the wrong resource, addressing nonexistent resources, addressing the wrong page, and address errors within a page. Among the in-page errors are: compensating errors, multiple addresses mapped to one location, and one address mapped to multiple locations (unstable address bits). These errors can be caused by faults in the processor or addressing logic, or in the address signal lines.

Faults in resource selection could possibly be detected by fault-tolerant resource/memory management devices, by general-purpose address monitors, or by standard use of handshaking procedures in address and data transfers. Page faults, where a "page" represents a set of addresses logically viewed as a group for purposes of address or memory management, could be detected by memory management devices. Monitors looking at "sequential address" and other flag signals from the processors could detect the specific types of faults to which these signals are related, but since a considerable fraction of the addresses sent out would not be thus protected, such an approach might be considered only marginally helpful in making a system highly fault-tolerant.

Compensating errors are those which cause parts of the system to perform outside of specifications, but which produce no error in results. A common example would be crossed address lines running to a homogeneous random access memory. Though data would be written to and read from the wrong addresses, the results would be correct as seen from outside the memory. Such errors, while not directly causing system failures, can complicate fault detection by producing readings inconsistent with system results and dependent on where the readings are taken.

Failures in which several addresses map to one location cause faults when a value is overwritten by a write to another address. Similar faults appear on reading. Such failures can probably be detected by diagnostics. Faults caused by unstable address lines can damage the contents of several locations, and make the fetching of needed data unreliable.

For highly fault-tolerant designs, methods similar to those used to protect data can be adapted to protect addresses. Two or more processors working in parallel can compare output addresses to detect/correct address errors caused by the processors, as described in the section on processor errors. Address check bits can detect errors in transmission. Redundant address detectors can be used at the intended locations to provide faulttolerant address decoding. Redundancy would therefore be employed in receivers rather than transmitters, so there would have to be changes in the response algorithm. Such an approach might not be considered worthwhile unless it were part of a complete system of fully redundant resources, with the redundant parts of each resource comparing actions several times in the process of serving the processor.

Architectures affected: Essentially all computer systems use addressing for low-level internal data manipulation. Many systems also use explicit addressing in higher level communications.

Test method: Other than by notification, addressing errors are most likely to be found by incorrect system output, as when user diagnostics are run. Comparison of address lines at source and destination can locate physical failures in the conductors. Induced errors may be used only if the address lines are available for external manipulation without damaging the system under test. Detection can be observed by fault signals or by perceived operation of the recovery system.

Special apparatus: Probes to observe address and fault signal lines may be used. It may be practical to design an address manager emulator and connect it to the processor and address lines, to evaluate the address management of the system. Error signal drivers may be used if possible.

Limitations of test: Many address signals will not be available for outside observation, especially in systems with VLSI components. It may be necessary in some cases to obtain approximate readings using indirect measurement techniques.

#### **3.3 Detection of data storage errors**

Storage of data in the interactive parts of the system involves registers as well as local and shared memories. Since different techniques for storage, retrieval, and fault detection are used for each, the different types of data storage are considered separately.

#### 3.3.1 Faults in processor registers, transient.

**Description of fault:** With the wide range of architectures used in fault-tolerant systems, the term "processor register" can be used to apply to the data, address, and flag registers closely associated with the processing circuitry, as in a microprocessor, or it can be used in reference to flip-flops, state machine registers, and generally all of the temporary storage used by the support circuitry in and around each processing element.

The fault-tolerant system can detect register faults (without necessarily identifying them) by use of hardware redundancy. Repeated tests can determine whether or not a given fault is transient.

If the transient fault is in a register of a conventional microprocessor, evaluation will be very difficult. Incorrect results may be the only sign of such faults, and testing and diagnostics will probably be unable to identify the register as the source of the fault. If, however, the fault is in a register with built-in fault detection or a register that is directly accessible by the system designer, there is a good chance that such faults can be isolated and specifically dealt with.

Architectures affected: In the general sense, all digital computing systems function as state machines, and require temporary storage for the "machine state". All architectures are therefore susceptible to register faults. Even with a narrowed interpretation of "processor register", the vast majority of machines use registers that fit within the definition.

Test method: For registers not directly accessible to the measurement equipment, evaluation is probably not practical. For registers that are accessible, direct observation will work, but will be awkward for looking at many registers simultaneously. Induced errors can be used to make the pattern of faults more predictable. The error-detected signals in the system under test will provide an indication that the error has been detected.

Special apparatus: Probes into system, error signal drivers.

Limitations of test: It is not practical to individually evaluate many of the registers of interest.

3.3.2 Faults in processor registers, permanent.

**Description of fault:** The registers of interest are the same as for the transient fault parameter, and similar techniques are used, for the most part. Register faults within a microprocessor are extremely difficult to observe directly. Observation is more practical for registers accessible from the outside. The presumed stability of the hardware failure, however, allows an additional set of techniques for detection and identification. The fault may be detected by physically redundant execution of a task. Temporal redundancy is ineffective as a detection technique in the system under test because the same error can appear each time, so redundancy of hardware is a necessity. Once a fault has been detected, diagnostics should be able to detect consistently erroneous performance of a given processor register, and thus determine the location of the fault.

Architectures affected: As is the case for transient register faults, essentially all machine architectures are affected.

Test method: The techniques used for transient register faults are also applied for permanent faults. Induced errors must remain stable for the duration of the test. Usersupplied diagnostics may be used to verify that the faults are present.

Special apparatus: Same as for transient register faults, possibly with different drivers to induce errors.

Limitations of test: Most of the same limitations apply as for transient register faults. The indirect observation of faults internal to microprocessors, etc. is somewhat less difficult.

#### 3.3.3 Errors in main memory and redundant copies.

**Description of fault:** Since memory elements make up a large percentage of the total logic element count in most systems, there is a good chance that many of the faults that occur in such systems will be in memory. For this reason, most systems have methods to detect and deal with faults in memory. While faults in logic elements, once detected, may be corrected by means of checkpointing or other methods, the permanent loss of the contents of a memory location can result in system failure. It is therefore vital not only to detect memory faults, but to recover from them.

Two major approaches to fault-tolerant memory design are the use of error detecting codes with storage of multiple copies of all data, and the use of error correcting codes. A combination of these methods may also be used. Error detecting codes and error correcting codes add a number of "check bits" to a group of data bits. There may also be a transformation of the data bits, but the net effect is that a certain number of bits are added to each item of data. These additional bits represent a function of the numeric value of the data bits. For error-detecting systems, the device which reads the data repeats the checking calculation, and compares the result to the stored check bits. For some of the currently used algorithms, this approach will fail to detect at worst about one in 2\*\*N of all possible combinations of errors, where N is the number of check bits. Some methods also guarantee to detect all errors of up to a certain number of bits. Reliability of detection increases with the number of check bits but the overhead associated with handling the additional information also increases. A tradeoff between reliability and overhead must therefore be chosen. With larger blocks of data, this tradeoff is less severe, but memory systems generally restrict the size of the protected blocks to that of the largest blocks transferred to and from memory in a single transfer, both to simplify writing and to maintain a reasonable memory bandwidth. In most current fault-tolerant systems such transfers are of 64 bits or less. If errors are detected but not corrected, it is necessary to maintain multiple copies of each value stored, preferably in physically separate memory devices to reduce the risk that all copies will be damaged by a single fault. The alternate locations should also be protected by check bits.

Error correcting codes contain sufficient redundant information in the added bits to allow reconstruction of partially damaged data. The usual claim is that all errors of up to a certain number of bits can be corrected. As an additional service, the error handling circuitry may be able to detect and report a much larger set of errors than can be corrected. The overhead for a given degree of error correction is greater than for a corresponding degree of error detection, but one may be able to reduce the level of backup protection and still maintain the same level of reliability. Error correction schemes usually work best when bit errors are evenly distributed. Since this is not always the case, and since too many errors in one data block can prevent recovery, at least one redundant backup copy is still important for highly reliable systems.

Architectures affected: Most systems have large storage areas available to the processors, to which these considerations apply. Systems which use a single large shared memory are particularly susceptible to memory faults, since such faults can affect all the processors by preventing successful use of their memory space, or by garbling processor-to-processor communications handled through common memory.

Test method: Error detection systems, upon perceiving an error, will generally send out a hardware or software error notice, which may be readily available to outside devices, or which may be reachable by probes into the system. Error correcting systems sometimes send out error notices, but usually refrain from signaling when a correctable error has been detected. In fact, the error recovery mechanism may be implemented at a very low level in the hardware, and the higher levels of hardware may not be aware that a correctable error has occurred. Unreported error correction, in addition to making measurement more difficult, can leave a user uninformed in the event that the system has a large number of hidden permanent faults which effectively reduce system redundancy. Some sort of reporting is therefore desirable even for errors which are corrected.

Unless the system under test has specific hardware features that make it possible, inducing errors of only a few bits in a few memory locations may prove to be difficult. Blocking out entire memory locations can be accomplished by tampering with the address signals. Similarly, bit errors that are the same for all locations can be induced by driving the data lines. If the system features modular construction with removable, standard memory devices, it may be useful to temporarily replace one or more of the devices with units known to be defective, in order to observe the detection and recovery process.

Special apparatus: Probes into system, error signal drivers. Defective memory modules could be useful, as described above. If this test is sufficiently important, special hardware could be built that would recognize specific memory addresses and inject errors when these addresses are accessed. In a system with a simple addressing protocol, there is a good chance that such a device could be implemented using a single programmable array logic (PAL) device.

Limitations of test: It may be difficult to induce or observe the response to certain patterns of errors that are of importance in evaluating fault tolerance. Though memory is more likely to be accessible to the outside world than many other system components, some systems have memory that is not accessible because it is on-chip or because of space limitations.

#### 3.3.4 Errors in local cache.

Description of fault: In order to reduce average memory latency and the loading on shared resources, systems with a large global memory often have a local cache memory associated with each processor. Copies of values from main memory are temporarily stored in the cache for fast access, in accordance with the particular cache control algorithm used. When the appropriate type of access is attempted, the memory controller looks in the cache before starting an access of main memory. Because of the close relation between cache and the memory access controller, problems with the cache can seriously affect all memory accesses. A cache that always reports a "miss" will slow the processor considerably, and the controller will waste time trying to update the cache. A cache that falsely reports a "hit" or stores a value incorrectly will cause an incorrect value to be received by the processor. While caches often use parity checksums on the data contents, there may be a tendency to leave cache address handling without proper protection. It is therefore important that cache controllers in fault-tolerant systems be designed with the ability to detect faults in the address and control functions of caches. This protection is made more difficult when transformation of addresses is employed.

The cache controller must keep track of the main memory addresses of all the values

stored in cache, and handle updates to or from main memory. In a typical set associative caching scheme, part of the address of a value is correlated with its location in the cache. The remainder of the address bits are stored in a table in a dedicated fast random access memory. This memory has one entry for each block of locations in the cache. Along with each entry in this table may be a bit specifying whether or not the corresponding location holds a currently valid item from memory. The contents of this table can be protected by check bits. The cache control mechanism can also be made fault-tolerant. For most caching schemes, detection of cache faults is far more important than local recovery of cache data, since in the event of a fault the "entry valid" bit may be cleared, a cache miss indicated, the cache disabled, and a main memory access initiated, with loss only of performance, not complete failure.

The most obvious approach to fault detection in the cache controller is redundancy. It may be practical to place several copies with comparison circuitry in each controller. Diagnostics could help in the identification of permanent failures. Fault notification would be very useful in the recovery of the rest of the system.

Architectures affected: The systems affected by this parameter are those which use cache memory.

Test method: User diagnostic programs can be used to detect permanent failures, but transient faults are likely to be interpreted as memory faults. If the signal lines are available for probes, faults can be recorded directly, or additional devices can be connected in parallel with the cache controller and the outputs compared. (A large number of systems use the TMS 2150 set of integrated circuits to implement cache control.) It may be possible to induce faults by driving data and address lines, or signal lines such as the "entry valid" line. Some systems allow the cache to be disabled, partly to facilitate the testing of other parts of the memory system. Fault notification lines may often be found for simple cache faults such as parity errors. Notifications for more complex cache faults, rare in current systems, would be specific to the particular system being evaluated.

Special apparatus: Probes into system, error signal drivers, possibly duplicate hardware.

Limitations of test: Because certain failure modes merely slow down operation of the processor, rather than causing overt errors, complete characterization of faults and fault detection may not be practical.

#### **3.4 Faults in data transformation elements**

Data transformation brings about permanent changes in the data, with the possible incidence of consistent (permanent failures) or inconsistent (transient failures) errors in the output. Some form of redundant execution using different individual devices is necessary for reliable detection of errors.

#### 3.4.1 Detection of faults within operating processors.

**Description of fault:** This parameter refers to the central portion of a system processing element, which is directly responsible for managing data stored in registers, manipulating and sending out data, fetching data and instructions, and controlling the sequence of execution of the program. In many modern systems, these functions are implemented on a single integrated circuit, a notable exception being bit slice processors, which are implemented using a small set of specialized integrated circuits. Memory management and mathematical operations, if performed outside the central processor, are considered separately.

Most current systems use extremely complex processors, with built-in features such as pipelines and internal cache to enhance performance. A complex microprocessor can have up to several hundred thousand logic elements, with more expected in future processors. At the same time, the number of signals available for interface with outside circuitry is extremely limited, almost always less than 200. (Simpler processors generally have far fewer pins or numerous processors on one integrated circuit, so the problem is essentially the same.) With the tremendous premium on signal lines, mechanisms allowing the user to monitor the detailed inner operations of the processor are usually neglected. (Bit slice processors and processors built from small- and medium-scale components, having more of their "internal" signals available to outside circuitry, can usually be retrofitted with additional circuitry more easily than can other types of integrated circuit processors.)

Because of the relative isolation from surrounding circuitry, any checking for processor errors in any system without redundant processors is generally the responsibility of the processors themselves. Some processors make use of on-chip fault detection and recovery mechanisms, but the extreme complexity of a processor and its even more complex state space make it impractical to provide really satisfactory coverage for all possible faults. Faults which are detected and corrected generally do not result in any notification outside of the processor, while faults that are detected but not corrected usually cause the processor to send out a specific error signal (which indicates error type, but not necessarily exact location), and halt normal operation so software fault recovery efforts can begin. Without external control mechanisms, a fault that causes a processor to lock up or run wild is likely to cause a system failure.

A method frequently used to check the internal operations of a processor is to execute a job on two or more processors and compare the results. If the results do not agree, then fault recovery operations are started. This method is effective for fault detection because, barring design flaws, two processors are unlikely to develop exactly the same set of transient or permanent hardware failures. A complex result on which two or more processors agree is therefore much more likely to be correct than a result produced by a single processor. The risk of common errors due to errors in input is minimized if memory, buses, etc. are also redundant. The comparison mechanism must also be highly reliable, or comparisons will not be valid.

The techniques used for fault recovery in redundant-processor systems depend on the interval between comparisons. Lockstep machines, which compare results in hardware every machine cycle, can suppress each fault as it appears, as previously described. Systems which check results only at the end of the task must repeat the entire task whenever an error appears. Some systems use a timer or program instructions and software comparison algorithms to compare results periodically throughout execution

of the task. This is called barrier checkpointing, because a synchronization mechanism must be used to make sure that the processors have all reached the same point in the execution of the task, by blocking execution until the checking has been completed. A copy of the intermediate results and the processor state is stored in a safe place. In the event that an error is detected in a system with only two-way redundancy, execution is started on backup hardware at the most recently completed checkpoint. Comparisons of intermediate results may be made more often than checkpoint storage, with execution after fault detection always returning to the nearest true checkpoint. Checkpointing increases the complexity of the software, but is able to protect running tasks, usually with less hardware than a system having enough redundant hardware to suppress errors. Checkpoints must be used before operations where recovery from an error may be impractical, such as a write to global memory or disk, or an I/O access.