NATIONAL BUREAU OF STANDARDS LIBRARY

# NBS-IR-85-3156

Hierarchical Control System Emulation User's Manual

Cita M. Furlani, Editor

January 1985

U.S. DEPARTMENT OF COMMERCE National Bureau of Standards Factory Automation Systems Division Gaithersburg, MD 20899 •

.

# TABLE OF CONTENTS

|    | P                                                                                                                                                                                                                           | age                              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1. | INTRODUCTION                                                                                                                                                                                                                | 1                                |

|    | <pre>1.1 Problem Overview 1.2 Solution Overview 1.3 Praxis and Related Documentation</pre>                                                                                                                                  | 1<br>3<br>7                      |

| 2. | BACKGROUND                                                                                                                                                                                                                  | 9                                |

|    | <ul> <li>2.1 Modular Hierarchical Real-Time Control Systems</li> <li>2.2 State Machine Concepts</li> <li>2.3 Shared Memory Synchronization</li> <li>2.4 Simulation vs. Emulation Modules</li> </ul>                         | 9<br>12<br>16<br>19              |

| 3. | SOFTWARE OVERVIEW AND GENERAL USAGE                                                                                                                                                                                         | 22                               |

|    | <pre>3.1 Software Overview 3.2 Description of Software Usage</pre>                                                                                                                                                          | 22<br>25                         |

| 4. | OPERATING SEQUENCE<br>4.1 Entering State Machine Modules<br>4.2 Parsing State Machine Modules (PARSE, PRAXIS)<br>4.3 Building Processes (DICT, BUILD)<br>4.4 Running the HCSE<br>4.5 Log File Output and Summary Statistics | 27<br>27<br>47<br>50<br>55<br>61 |

| 5. | SAMPLE DIALOG                                                                                                                                                                                                               | 63                               |

| б. | ERROR MESSAGES AND DEBUGGING                                                                                                                                                                                                | 77                               |

.

• •

| /. | PERFORMANCE CAPABILITIES AND LIMITATIONS        | 80       |

|----|-------------------------------------------------|----------|

|    | 7.1 Limitations<br>7.2 Performance Capabilities | 8Ø<br>82 |

| 8. | APPENDICES                                      | 85       |

#### 8. APPENDICES

-

| 8.1 | Specific Hardware and Software Requirements | 85 |

|-----|---------------------------------------------|----|

| 8.2 | Creating State Machine Modules from State   | 86 |

|     | Machine Descriptions                        |    |

| 8.3 | Praxis Primer and Text I/O Documentation    | 92 |

•

----

•

-

## LIST OF FIGURES

|          |                                          | Page |

|----------|------------------------------------------|------|

| FIG. 1.  | TYPICAL MODEL STRUCTURE                  | 5    |

| FIG. 2.  | EMULATION SEQUENCE                       | 6    |

| FIG. 3.  | HIERARCHICAL CONTROL SYSTEM              | 10   |

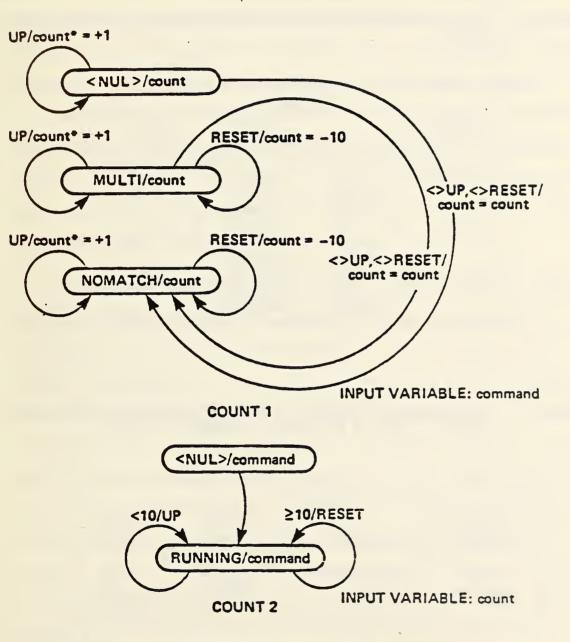

| FIG. 4.  | MODULES COUNT1 AND COUNT2                | 65   |

| FIG. 5.  | COUNT1.PRX                               | 66   |

| FIG. 6.  | DICTIONARY LISTING FOR COUNT1 AND COUNT2 | 68   |

| FIG. 7.  | UPDOWN.PRX                               | 69   |

| FIG. 8.  | LOG LISTING FOR PROCESS UPDOWN           | 72   |

| FIG. 9.  | SUMMARY LIST CORRESPONDING TO FIGURE 8   | 75   |

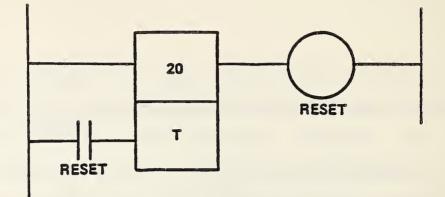

| FIG. 10. | STATE MACHINE DIAGRAM FOR EXAMPLE        | 87   |

| FIG. 11. | RELAY LADDER DIAGRAM FOR EXAMPLE         | 91   |

# ÷ : .

•

|       |     |                          |      |       |     |        |           | Page |

|-------|-----|--------------------------|------|-------|-----|--------|-----------|------|

| TABLE | 1.  | FSM MODULE               | FORM | ΥT    |     |        |           | 30   |

| TABLE | 2a. | ENUMERATED<br>FOR COUNT1 | NEXT | STATE | AND | OUTPUT | FUNCTIONS | 89   |

| TABLE | 2Ъ. | ENUMERATED<br>FOR COUNT2 | NEXT | STATE | AND | OUTPUT | FUNCTIONS | 68   |

...

:

.

# Acknowledgement

The major part of the work that is represented in this manual was done by Bolt Beranek and Newman, Inc. under Department of Commerce Contract NB81SBCA0826 entitled "Emulation/Simulation of an Automatic Manufacturing Test Facility". This manual in its original form was derived from the final report (dated October 1982) from that contract. The product has been further modified at the National Bureau of Standards. This manual documents the state of the Hierarchical Control Systems Emulator as of January 1985.

#### 1.0 INTRODUCTION

'n

#### 1.1 Problem Overview

The design of any feedback control system with even modest complexity requires simulation capability. The controlled plant and feedback law are simulated in order to assess the possible effects of discrepancies between the design model of the plant and the actual plant, and in order to verify the correctness of design approximations. In feedback systems, the effects of such discrepancies can be particularly serious and may be manifested instability in continuous-state systems, as classical or as errors (trap states) and/or loss of synchronization in Simulation averts the most discrete-state systems. serious errors of these types because the control system design can be corrected without physical damage to the actual plant. Most simulations today are digital rather than analog.

Increasingly, the implementation of control systems is also digital rather than analog, and this raises some new issues:

- 1. What capacity and speed of computer is required?

- 2. What is the impact of computing and communication delays on closed-loop system performance?

- 3. What structure of real-time software should be employed?

- 4. What is the impact of errors in programming logic, or of errors in the designer's conceptual model of the system's logical relationships?

- 5. What is the impact of discrete failures or of software failures?

In order to answer these questions, it is not sufficient to merely simulate the input-output relationships of the control structure and logical Rather, the internal system. implementation features of the control system (as well as the controlled system itself) need to be represented. Ideally, a one-for-one representation of the control system logic and timing is desired for this purpose. The term emulation has been applied to this sort of "one-for-one" simulation.

In contrast to methods for designing feedback control of continuous-state dynamic systems, analytic methods for the design of discrete-state feedback systems are at a very primitive stage. Since the available design methods are largely heuristic, even more emphasis must be placed on the iterative design process whereby an initial design is improved on the basis of simulation results. A rather general heuristic for the design of discrete control systems is the modular hierarchical approach proposed by \*\* Albus, Barbera and Nagel (1980). The Hierarchical Control System Emulator (HCSE) described herein provides emulation/simulation capabilities for a broad class of systems -- in particular, automated manufacturing systems -- which can be controlled by modular hierarchical control systems.

The term came into use in the context of verification of computer software, where one computer was made to emulate the operation of another which typically was in the design stage. The operating system software, which is designed this way, actually implements a discrete feedback control system.

\* \*

\*

See Section 2.1 for further details of this approach.

1.2 Solution Overview

The use of the Hierarchical Control System Emulation is described in Sections 3-5 of this manual, and the more eager user is referred directly to those sections. The operation of the emulation may be divided into three phases:

- 1. Data entry (making modules)

- 2. Running the HCSE

\*

---

3. Data logging and analysis

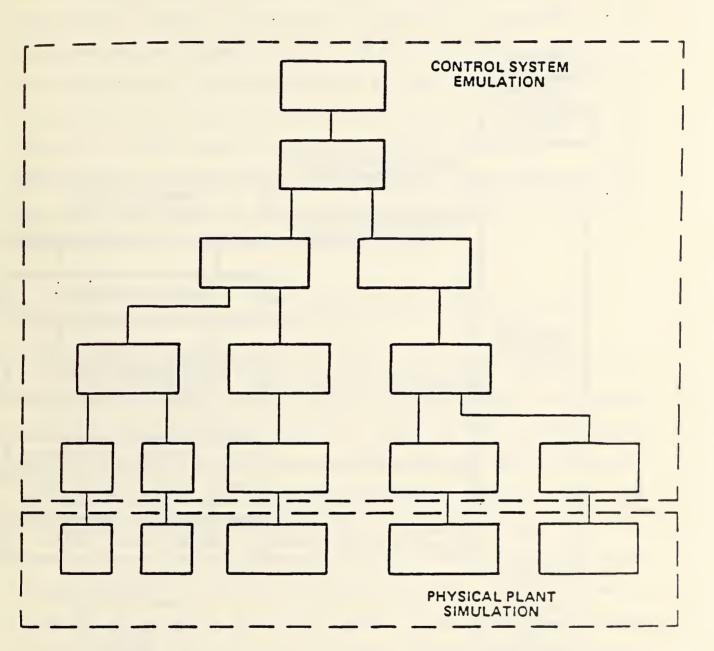

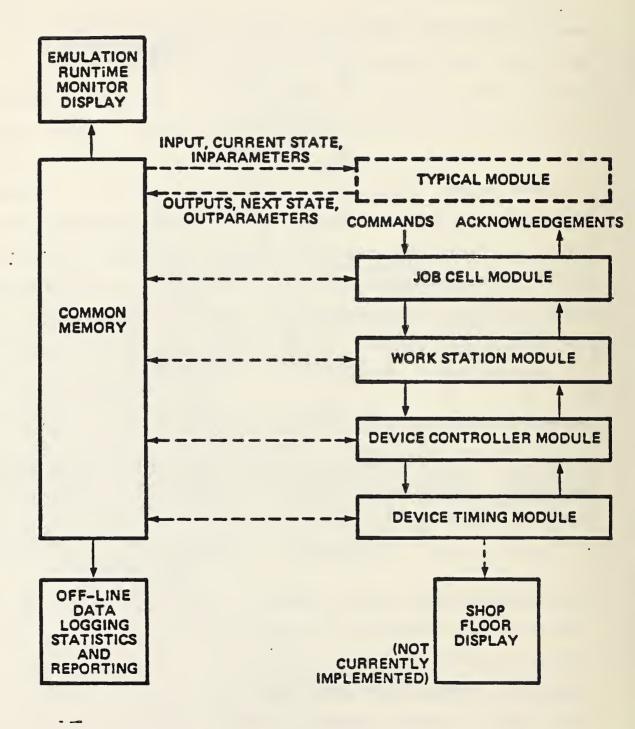

The user enters data for the emulation/simulation entirely by writing module descriptions. Each module has a common format based on a generalized state-machine description with named variables. Communication between modules, which is transparent to the user, is achieved totally through storage (by name) of common input and output variables in a shared (common) memory; access to the memory is time-slice synchronized. The pattern and sequencing of input/output transactions between modules may be specified by the user to define a hierarchical relationship of the control system modules. The module format is sufficiently general that modules may be used to simulate physical devices (subsystems of the controlled plant) as well as emulating control system components. Normally, these simulation modules are at the bottom of the hierarchy and communicate horizontally with each

..

The module format and shared memory implementation were dictated by requirements of the NBS Automated Manufacturing Research Facility.

other as well as vertically with the hierarchical control system (Figure 1).

5

In order to run the emulation, the modules may be combined into subsets which are translated into executable form and run as independent processes. These processes are synchronized through common memory. The run-time display runs as another process and allows the user to monitor the real-time progress of the The user may synchronize the actual rate of progress emulation. of the emulation through the run-time display to achieve single-cycle operation, wall-clock sychronization with variable time-scaling, or free-running (maximum-speed) emulation. The user selects the variables from common memory which are to be displayed, and may stop the emulation to record "snapshots" of common memory at any time.

Prior to running the emulation, the user may select certain variables for "logging" purposes. Upon completion of a run, these logging files may be processed to produce summary statistics concerning the values taken by each logged variable and the amount of time spent at each value.

The emulation meets a number of key requirements for hierarchical control system design and evaluation. Communication and computing delays can be emulated. The allocation of modules to different physical processors can be emulated. Different choices and allocations of module functions can be evaluated, and the effects of coding changes within modules can be assessed.

•

2

FIG. 1 TYPICAL MODEL STRUCTURE

۶.

FIG. 2. EMULATION STRUCTURE

5

Both continuous and discrete variables can be represented; in particular, both continuous physical processes and decision-making processes may be included in the evaluation. Foth discrete and continuous sources of error may be represented. Finally, the level of detail in the emulation is under the control of the user, so that critical operations may be represented with great accuracy, while only rough approximations of other subsystems are used. These and additional capabilities are discussed in more detail in Section 7.

# 1.3 Praxis And Related Documentation

The hierarchical control system emulation is written primarily in Praxis -- a modern, strongly-typed structured language developed by BBN. Inc. -- to run on a VAX 11/760 Digital Equipment Corporation processor with VNS operating system and DEC-supported terminal (or equivalent, such as the EBN Bitgraph). During development, certain portions of the emulation were written in Ratfor (Rational Fortran). This code has been translated into Fortran 77 and into Praxis. Extensive use is made of VNS operating system utilities. The references listed below provide appropriate background in these areas. The reader is assumed to possess elementary knowledge of the VNS operating system and the Praxis language. Section 8.3 contains a Praxis primer.

Certain commercial products are identified in this manual in order to adequately describe the HCSE. Such identification does not imply recommendation or endorsement by the National Bureau of Standards.

The purpose of this manual is to describe the operational aspects of the HCSE completely. Thus, it is a self-contained reference for the user. In addition, the HCSE Applications Guide describes in detail the substantial emulation example modeled after a portion of the NPS Automated Manufacturing Research \* Facility. The Programmer's Manual describes the emulation software itself and is intended for use by those who wish to maintain, augment, or modify the HCSE.

#### Reference List

.

\*

- 1. <u>VAX/VMS</u> Command language User's Guide, Digital Equipment Corportation, Naynard, MA., 1980.

- Praxis Language Reference Hanual, BBN Report 4582, January 1981 (see also directory [PRAXIS.DOC] for on-line documentation).

- 3. Johnson, T.L., Milligan, S.D. and Fortmann, T.E., "Hierarchical Control System Emulation User's Manual", BBN report No. 5096, Bolt Beranek and Newman, Inc., Cambridge, MA., July 1982.

- Johnson, T.L., Milligan, S.D. and Fortmann, T.E., "Hierarchical Control System Emulation Applications Guide", BBN report No. 5094, Bolt Beranek and Newman, Inc., Cambridge, MA., July 1982.

- 5. Milligan, S.D., Johnson, T.L., and Fortmann, T.E., "Hierarchical Control System Emulation Programmer's Manual", BBN Report No. 5095, Bolt Beranek and Newman, Inc., Cambridge, NA., July 1982.

The example does <u>not</u> reflect actual hardware or software of the AMRF, as these were not yet fully specified at the time the ECSE was developed.

#### 2.0 BACKGROUND

ĥ

The purpose of this section is to review the key concepts of hierarchy, modularity, state machine tables, shared memory, and synchronization which have dictated the central features of the emulation. The user will quickly discover that the actual emulation software imposes very few constraints due to these design requirements, so that almost any sort of control system and controlled plant can be represented with relative ease. Nevertheless, the use of the emulation is most convenient when it is consistent with the underlying design concepts. The specific implementation of the key concepts is described in Section 4.

#### 2.1 Modular Hierarchical Real-Time Control Systems

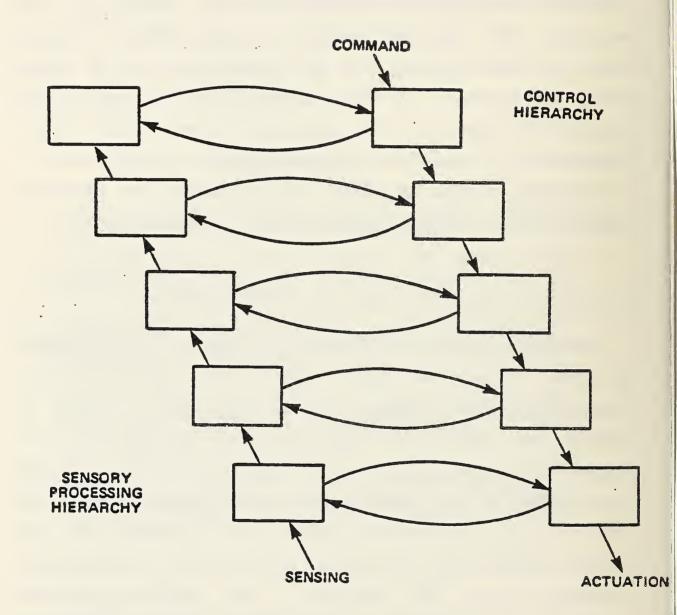

The general concepts of hierarchical control are described Barbera and Magel (1980). An illustration of a in Albus, hierarchical control structure is shown in Figure 3. When а command is entered at the top of the hierarchy, it is successively decoded (or interpreted) into more and more detailed instructions at the lower levels of the hierarchy, until the lowest levels of the hierarchy provide an interface with the physical process being controlled. This accounts for information propagation down the hierarchy. The sensory-interactive hierarchy also provides for the crucial upward flow of sensory

The diagram does not depict other data flows, such as data base interfaces.

FIG. 2. HIERARCHICAL CONTROL STRUCTURE

information about the physical process being controlled; this information is abstracted (digested) as it passes upward in the hierarchy. Each level of the hierarchy must reconcile its commands from above with the actual state of events below in order to send appropriate sub-commands or corrective actions to the level below it. Such a system is most efficient when errors are handled on the lowest level at which there is command information that is sufficient to formulate appropriate corrective action: "local" errors are corrected at lower levels, while "global" errors are corrected at higher levels. This explicit use of feedback at all levels of the hierarchy and the hierarchical decoding commands distinguish of the sensory-interactive hierarchical approach from the more traditional preplanning approach where errors typically cause emergency shutdowns which necessitate complete replanning or rescheduling. Feedback occurs at all levels of the sensory-interactive hierarchy.

The basic functions of a typical module can be summarized as follows:

- (1) Interpret command inputs from the level above.

- (2) React to acknowledgements and other sensory information passed up from the level below.

- (3) Generate subcommands for the level below.

- (4) Generate acknowledgements and pass digested sensory data to the level above.

As viewed from a given module, note that (1) and (2) appear as (3) and (4) appear as outputs. In addition, each inputs while least) for the module must provide (at appropriate time-sequencing of its operations; i.e., it must maintain responsiveness to its inputs without sacrificing continuity or fidelity of its output computations.

In order to comprehend the operation of such sensory-interactive modules and thus to facilitate design and testing of the whole hierarchical control system, it is desirable to impose a discipline on the internal structure of each module. A generalized finite state machine structure is both simple and sufficiently general for this purpose.

#### 2.2 State Machine Concepts

Each module is assumed to be represented by a generalized finite state machine. The module samples its inputs and produces new outputs at every cycle. This assures that input changes will not be unintentionally ignored; that the data to maintain responsiveness is available; and that the outputs are available on every cycle. The response latency thus depends on the (worst-case) cycle time of the machine. The operation of the machine is broken down as follows:

This is a classical problem in the design of any real-time system, and in particular, computer operating systems.

- 1. Sample current inputs

- 2. Compute next state

١,

----------

3. Compute next output

The formal definition of a finite-state-sequential machine requires that the set of possible input values be finite, that the set of states and output values be finite, and that the next-state and read-out functions be representable as boolean functions. Taken literally, these conditions are too restrictive for the class of applications we wish to consider. The generalized state machine concept that is employed in the HCSE retains the elements of the formal definition but broadens the interpretation in the following ways:

- Inputs and outputs may include real-valued variables and integers.

- Next-state and read-out functions are "effectively computable", i.e., they may be implemented by subroutines or procedure calls.

The term "threshold finite automation" has been applied to this generalized state machine. Note that the dimension of the state set is still finite (in the HCSE it is approximately A\*\*31 where A^50, so this restriction is not too significant in practice).

The implementation of state machines is somewhat simplified by adopting the convention that the next state and output remain unchanged unless one of a (usually small) set of conditions in

Arbib, M.A., and Bobrow, L.S., <u>Discrete Mathematics</u>, W.B. Saunders Co., Philadelphia, PA., 1974.

the current state and inputs occurs. When the current state is given, only a modest number of transition conditions (or "trigger conditions") need to be tested in order to determine the next This observation greatly reduces actual computing time; state. however, it is often the case in practice that although the trigger conditions involve only a small number of inputs variables, the actual computation of the next state and output function may also involve a larger set of other variables that never in themselves cause a state transition. In a strict sense, these variables must also be regarded as inputs; in the HCSE, the term "input" is intended for those input variables which appear in the trigger conditions, while "input parameters" are intended to apply to the non transition-causing inputs. Similarly, "outputs" of a module are seen as triggering state transitions in other modules, while "output parameters" provide non transition-causing variables to other modules. This distinction is purely a matter of style, and no internal distinction is made within each pair of terms in the HCSE.

5

In the general concept of a state machine, we are mostly concerned with deriving proper input and output values for a particular machine. However, a certain amount of internal processing must take place before output values can be derived from the inputs. The variable "internal" is intended to accomodate such internal processing by retaining the intermediate values which represent the internal state of a module. An "internal" variable is neither an input nor an output from the module in which it resides. Therefore, its value is totally transparent and inaccessible to the other modules in the emulation. Given this, "internal" variables should only be used whenever the value of a variable is not to be transported beyond the confines of the parent module, i.e., an internal counter. Remember that a module only goes through its state table when its inputs change. Thus, if an internal variable is all that has changed on a particular clock tick, the FSM will remain 'asleep'.

Another variable that accomodates internal processing is the "state" variable. However, a "state" variable is both output and input to the FSM that declares it. The "state" variable may be used to monitor the internal process of a module.

State machines can be specified in a variety of ways. and in general, there exist a large number of equivalent ways to implement the same module function. Usually, a module with a smaller state set and fewer input and output variables will be more efficient than one with more input, output, and state values (here, we are referring to the states of the machine, not "state" variables.) in the sense that fewer transition conditions need be However, in some cases the next-state and output tested. computations may be simplified when more input, output, or state values are used. For these reasons, it is inadvisable to become particularly attached to a specific module description. Three common methods of specifying state machines are through state transition diagrams, state tables, and ladder diagrams. Conversion of these formats into HCSE form is reviewed in Section

8.2.

#### 2.3 Shared Memory Synchronization

The shared memory contains the current values of a11 variables which are shared between modules. These include (by convention) the current state of each module, its input, state, and output variables, and input and output parameters. In order. for the common memory to serve as a communication exchange between modules, read-write and overwrite conflicts must be avoided. One way to do this is time-slice synchronization. A fixed time-step is chosen (usually based on the maximum bandwidth requirements of the system). Each time-step or "tick" is subdivided into a read and a write cycle. During the read cycle, each module that requests memory access is permitted to read all of its inputs, input parameters, and state variables and no module may write into common memory. During the write cycle, any module which is ready to write is permitted to write all of its state variables, outputs, and output parameters, but no module may read from common memory.

The emulation achieves this effect in a way that is general enough so that the user retains considerable control over its

Ĵ.

<sup>\*</sup>

This is the "macro-state" of the module; it is not the complete state in a rigorous sense because other local information (e.g., in the computational procedures) is retained between time-steps in order for the module to proceed, in the form of internal variables that are not shared.

real-time performance. All modules which are scheduled to read from memory on a given "tick" may read variables in any order upon request (the actual order being determined by the VAX/VMS operating system), but no module is permitted to write on any cycle until all modules have completed their read-requests. Then all modules which are scheduled to write will write their output variables to common memory. In order to prevent overwrites, no two modules should have the same variable as an output. The foregoing events take place asynchronously as fast as the VMS operating system will allow, and the worst-case time determines the maximum emulation speed since the emulation runs on a single \*

The occurrence of the next clock "tick" is determined by the interactive display module. In single-step mode, the next "tick" (i.e., beginning of the next "read" cycle) occurs when the user issues a keyboard command. In variable-rate real-time mode, the user specifies the ratio of clock time to emulation time, and the elapsed time on the system clock determines the next tick. In free-running mode, the next tick occurs immediately upon completion of the write cycle; the actual emulation speed may

The total number of independent processes, the maximum number of common memory variables for each process, and the time for the operating system to serve a single process determine the actual maximum speed. The VAX/VMS operating system updates a process status every 10 msec.

#### \*\*

\*

------

ĥ

If the specified time has already elapsed, the next tick occurs immediately.

depend on the loading of the system by other users in this case.

-

The user also has several means with which to control when each module is scheduled to read or write. To start with, each module is assigned a basic scheduling interval when it is built into a VNS process as described in Section 4.3. A low-level module might be scheduled every tick, while a high-level module might be scheduled every 50th tick. The scheduling intervals have a significant impact on the running speed of the emulation. Furthermore, pre-defined variables are provided within each module to represent the effects of computing and communications The compute-delay variable, which may be set depending delays. on which computation a module executes or simulates on a given step, has the effect of delaying the writing of the outputs to common memory by the number of ticks which it specifies and of delaying subsequent reading from common memory; the communications-delay variable has the effect of delaying the output of a module by a fixed amount without affecting its scheduled reading rate.

Delays significantly affect the way in which modules are designed, because it cannot be assumed that current outputs will be read immediately by other modules. The intended recipient must acknowledge having received the output, or further output changes may be made without being seen by the receiver due to scheduling delays. A related observation is that inputs must be removed after they are acknowledged, or they will be re-executed. Unless every module is scheduled at every time-step, these problems are not solved by common memory synchronization alone.

### 2.4 Simulation vs. Emulation Modules

Simulation modules, in contrast to emulation modules, represent the input/output relationships of segments of a controlled system, but not necessarily their internal structure. Usually, simulation modules represent non-digital (e.g., electromechanical, mechanical, chemical or thermal) parts of the controlled process, but they may also be used to represent digital subsystems or analog control system components. The HCSE module format is sufficiently general that simulation modules can be programmed in exactly the same way as emulation modules. However, the actual content of simulation modules will usually differ from that of emulation modules, and in order for emulation modules to be most effective, certain principles should be observed in composing the module.

Input and output variables of a simulation module should be chosen to correspond to signals which are readily identifiable and measurable in the actual physical control system under design. Typically, these can be classified as actuation or "control" signals, and sensory or "acknowledge" signals. The boundary between emulation and simulation may be drawn either between a central processor and device controller, or between the device controller and the physical process, depending on the desired level of detail. The most important principle for

selecting inputs and outputs is that parameters or variables from a simulation module should not be passed into an emulation module (and vice versa) unless there is to be a corresponding explicit control process in the actual physical measurement or In this way, errors in control system logic will implementation. be discovered much more readily. The conceptual model of plant employed by the control system designer may or may not behavior be consistent with the actual state equations governing parts of the plant, as incorporated in a simulation module, and the structure of the emulation/simulation should allow for this source of error if it is to be useful for control system design.

The input/output relations of a simulation module shoul d represent as closely as possible the input/output relation of the physical subsystem being simulated. Often, such systems mav be viewed as having a number of operating regimes (discrete states), where state transitions depend on the evolution of continuous variables (continuous state) within each regime. To simulate this situation, the (discrete) module states are placed in correspondence with the operating regimes. The module is scheduled to read and write at regular intervals. Each time the inputs are read, a variable-time-step integration procedure appropriate to the current state (i.e., regime) is called, and variables are integrated forward one time-step. continuous Finally, the conditions for switching between regimes are tested, discrete state is updated, and the appropriate outputs are the generated. Functions which return the current number of ticks,

the tick-spacing, and the system clock time are available to the user in order to properly synchronize the simulation. In the emulation/simulation of an event-driven control system, only the simulation modules will call these functions.

;

A simulation module may communicate global parameters to the other simulation modules (e.g., to determine when two independently-simulated physical objects come into contact) even though the variable is not sensed. Usually, the collection of all simulation modules constitutes a self-contained model of the environment, plant, or controlled system while the collection of all emulation modules constitutes a self-contained model of the feedback controller. Variables are passed between the distinct sets of simulation and emulation modules only if they correspond to explicit physical quantities which are measured or controlled. While all modules communicate information through опе shared memory, the shared memory in the HCSE should be effectively partitioned (in a well-designed application) into a part corresponding to the emulated control system common memory, a separate part for the shared simulation variables (representing interaction between subsystems of the controlled plant), and interaction variables which represent sensor measurements and actuator command values.

#### 3.0 SOFTWARE OVERVIEW AND GENERAL USAGE

Section 3.1 provides a user's overview of what software is contained in the emulation, while Section 3.2 describes in general terms how the software is used. The user should verify that the software described in this section is available on his VAX 11/780 VMS system before attempting to apply the operating sequence described in Section 4.

#### 3.1 Software Overview

This section describes the principal software components of the HCSE, from the user's perspective. A complete set of filenames and libraries is listed in Section 8.1 of this manual. Hore detailed documentation of these programs may be found in the Programmer's Manual.

It is convenient to assume that the operational software is organized as a main directory which will be termed the HCSE\_LIBRARY, along with three other libraries (of object files) termed the common memory library (CM\_LIBRARY), the Praxis library (PRAXIS\_LIBRARY) and the BP library (BP\_LIBRARY), which is a utilities library. These libraries are accessed by the VMS linker through a linker options file in producing executable process images prior to running the emulation. Mostly, the

BP library is a BBN-developed library supplied to NBS under a one-site license agreement. Need for this library may be eliminated in future versions of the HCSE.

executable files contained in the HCSE\_LIBRARY are discussed in this manual, although references will be made to a few library routines which the user may find helpful in composing emulation/simulation modules.

<u>Command files</u>: Command files in the HCSE\_LIBRARY include

#### FOREIGN.COM BEGIN.COM

'n

FOREIGN defines a set of VMS foreign commands which the user executes, as described in the next section, to compose, run, and evaluate an emulation. One of these foreign commands is the BEGIN command, which starts a named VMS process with privileges and options appropriate to the emulation; the BEGIN command invokes the BEGIN.COM file. The other foreign commands merely invoke executable process images which are described in the following paragraph.

Executable files: Executable files in the HCSE\_LIBRARY include

PARSER.EXE DICTION.EXE BUILDER.EXE DISPLAY.EXE FORCEX.EXE SMERGE.EXE SIMLIST.EXE SUMMARY.EXE

With the exception of DISPLAY, these images are executed (normally in the sequence shown) by the foreign commands PARSE,

DICT, BUILD, KILL, SMERGE, SIMLIST, and SUMMARY, respectively. DISPLAY is executed during the emulation using the foreign command DISPLAY. The Praxis compiler is invoked by the PRAXIS command, defined as a system global symbol. The list of directories searched by the Praxis compiler are defined as system logical names PRX\$SYNOPSIS\_0 through PRX\$SYNOPSIS\_4.

Object files: Object files obtained from the CM\_LIBRARY and the PRAXIS\_LIBRARY directories in the course of executing the foreign commands, command files, and the display program include

> VAXDEF.OBJ SHRMEM.OBJ SHAREOUT.OBJ RECREAD.OBJ

5

VAXDEF, SHRMEM, SHAREOUT, and RECREAD contain procedural \*

primitives which implement common memory, and VAXRUNTIM.SPS contains Praxis synopsis of VMS and Fortran library procedures used in the emulation.

The file VAXRUNTIM.SPS is located in a synopsis subdirectory off the same main directory which holds the PRAXIS\_LIBRARY.

#### 3.2 Description Of Software Usage

Prior to attempting to run an emulation, as described in Section 4, the user should personally confirm that the directories. libraries, and files described in the previous subsection (3.1) exist on the system. In addition, if the tick-spacing is to be adjusted, the Programmer's Manual should be consulted.

After these initial steps, the process of coding, running, and analysis is achieved by a sequence of straightforward steps:

- Source code for each module is entered by the user in finite-state machine (FSM) format using any available text editor.

- 2. The state machine code for each module is parsed to produce a corresponding Praxis module (PARSE command), which is then compiled (PRAXIS command) to produce an object module and a synopsis file.

- 3. Sets of Praxis object modules are linked together, with appropriate scheduling delays, to form concurrently executable VMS processes (BUILD command).\*

- 4. A data dictionary for the full set of modules is produced in order to verify consistency of type declarations and variable names among modules (DICT command). This is useful for initial debugging purposes.

- 5. Each emulated process produced in step 3 is started up (BEGIN command). Lastly, the DISPLAY process is run (DISP command) and the emulation begins.

- 6. The user interacts with the display process at the terminal to monitor and control the progress of the emulation.

\_\_\_\_\_

Separate VIS processes may be used to emulate execution on cifferent physical processors; logging and data analysis is on a per-process basis.

•

7. Upon completion, the user causes each process to exit gracefully (KILL command).

-

The user may list logging files (SIMLIST command), merge them (SMERGE command) and/or produce summary statistics (SUMMARY command).

A very simple example of this sequence is provided in Section 5. Of course, the above sequence of steps does not include the process of troubleshooting in cases where errors may arise; this is discussed in Section 6.

#### 4.0 OPERATING SEQUENCE

The purpose of this section is to describe in detail each step in the use of the hierarchical control system emulation as outlined in Section 3.2. The most demanding step. by far, is the formulation of state-machine code for each module of the emulation, which is necessarily the user's responsibility. The global issues of any particular application cannot be adequately addressd in this manual; for this purpose, the <u>HCSE Applications</u> <u>Guide provides an example of significant complexity</u>. This manual is restricted to specific issues that are generic to a broad class of applications, and only a very simple illustration is provided in Section 5 in order to clarify the format of user interactions at the terminal.

#### 4.1 Entering State Machine Modules

------

General state machine concepts were summarized in Section 2.2. In the HCSE, a state machine module is entered by the user. A source file of type FSM uses the specific format described below, using the VMS EDT (EDIT) facility or any other editor. The module format consists of an initial part with several individual subsections which are initialized by statements beginning with double-slashes (//). A second part follows.

Although the emulation must be run on a DEC-supported terminal, or equivalent, source files may be entered from any terminal for which a text editor is available.

consisting of a collection of procedures written in Praxis which implement the detailed (or micro-state) calculations of the next-state and read-out maps. In parsing this source code, the initial section is translated into Praxis code. The parser also adds a suitable module template which provides read/write operations, and carries through the Praxis procedures from the second part of the source file unchanged. Among the advantages of this approach are that the source file has a simple standard format, that type-checking between modules can be preserved, and that the user is not obliged to repeat any tedious formatting details that are common to all modules of the emulation.

FSM Source File Format: The general format of an FSM module shown in Table 1. The first part consists of lines which is define types and declare input, output, state, and internal variable names in terms of these types, followed by a sequence of condition-action lines that implement rows of the state table. (The procedure for converting state-machine descriptions into state tables is summarizd in Section 8.2). Each line has a similiar structure

//identifier-token (space) declaration-token (space)

type-token (space) | comment-text

where any one of the tokens may be blank (empty). The identifier-token may be:

(empty)

1

section already initialized by a previous identifer-token or the line is blank

```

TABLE 1. FSM MODULE FORMAT

//name MODULENAME

//input INPUTVARIABLE TYPE

. . .

//inparameter INPUTPARAMETER TYPE

. . .

//internal INTERNALVARIABLE TYPE

Declaration Section

. . .

//outparameter OUTPUTPARAMETER TYPE

. . .

//output OUTPUTVARIABLE TYPE

. . .

//preprocess STATEMENT

. . .

//postprocess STATEMENT

. . .

//conditions CONDITION1 ;

CONDITION2

State-table Section

. . .

//actions STATEMENT1 ; STATEMENT2 ; ...

[condition-action pairs]

//multimatch STATEMENT

//nomatch STATEMENT

//procedures

procedure PROCEDURE 1( )

Procedures Section

. . .

end procedure {PROCEDURE 1}

. . .

[more procedures]

procedure PROCEDURE N()

. . .

endprocedure {PROCEDURE_N}

[end of file]

```

| name         | module name (must agree with<br>filename of FSM module)                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------|

| include      | type declaration file                                                                                       |

| type         | type declaration                                                                                            |

| input        | input variable declaration                                                                                  |

| inparameter  | input parameter declaration                                                                                 |

| internal     | internal variable declaration                                                                               |

| state        | state variable declaration                                                                                  |

| output       | output variable declaration                                                                                 |

| outparameter | output parameter declaration                                                                                |

| preprocess   | preprocessed input variable declaration                                                                     |

| postprocess  | post processed output variable declaration                                                                  |

| conditions   | conditions for a state transition                                                                           |

| actions      | actions defining next state and output computations                                                         |

| multimatch   | actions defining next state and<br>output when multiple conditions<br>are satisfied                         |

| nomatch      | actions defining next state and<br>output when no condition is<br>satified                                  |

| procedures   | denotes beginning of procedures<br>part of FSM module; all code<br>after this line is strictly<br>Praxis () |

One or .more spaces delimit the remaining tokens. The declaration-token may be:

• •

name\_declaration

module name, if the identifier token is "name" file name, if the identifier is "include" user-defined type name, if the identifier is "type" variable name, if the identifier token is "input", "inparameter", "internal", "state", "output", or "outparameter"

statement\_declaration

compound statement, if the indentifier token is "conditions", "actions", "multimatch", "nomatch", "preprocess", or "postprocess"

•

•

(empty)

if the identifier token is (empty) or "procedures"

Variable names, user-defined type names, and module names are strings of 29 or less characters that are valid as Praxis names (this excludes control characters, names that begin with nonalphabetic upper case symbols and Praxis reserved words). Type declaration files can have any file name acceptable to VAX/VMS systems. A compound statement consists of simple statements separated by semi-colons (up to a total of less than 132 characters per compound statement with no linefeeds, carriage returns, or other control characters). A simple statement may be either a logical expression (only when the identifier token is "conditions") or a valid Praxis statement (otherwise). A logical expression in this context is the same as a boolean expression in Praxis, with the important generalization that logical operations are considered to be well-defined between string variables of different lengths; thus the expressions

```

string l = "long-or-short-word"

string l <> "anything_else"

```

- 5

have meaning when string 1 and string 2 are (in general) different-sized arrays of characters.

The type-token is only recognized when the identifier-token is "type", "input", "inparameter", "internal", "state", "output", or "outparameter". In these cases the declaration-token (a name declaration) and the type-token must both be present. The typetoken can take values:

| char                 | Praxis character variable or parameter            |

|----------------------|---------------------------------------------------|

| integer_1            | Praxis one byte integer<br>variable or parameter  |

| integer or integer_2 | Praxis two byte integer<br>variable or parameter  |

| integer_4            | Praxis four byte integer<br>variable or parameter |

| real or real_4       | Praxis four byte real<br>variable or parameter    |

| real_8               | Praxis eight byte real<br>variable or parameter   |

| logical or logical_l | Praxis one byte logical<br>variable or parameter  |

| logical_2            | Praxis two byte logical<br>variable or parameter  |

| logical_4            | Praxis four byte logical<br>variable or parameter |

This greatly enhances the clarity of the source code. The parser actually converts such expressions into valid Praxis functions in a later step.

• • •

booleanPraxis boolean variable or<br/>parameterpcharPraxis character variable or<br/>parameter initialized \$<NUL>stringpacked array of up to 31<br/>characters (not a standard<br/>Praxis variable type)oruser-defined typePraxis type declaration<br/>(can be one of three permissible

2

The first ten items in the list above are recognized by the parser as basic data types. The remaining items (except for user-defined types) are data types commonly used in FSM modules and their subsequent definitions are stored in a reference file named STANDARD.ISM located in HCSE\_LIBRARY. The types declared in this file along with the basic types described above are automatically incorporated into FSN modules (by the parser) prior to the appearance of any type declaration lines in the source code.

structure)

data types: alias, array, or

In addition, the user has the capability to declare his own data types in terms of the predefined types presented above and/or other user-defined data types that were previously declared. Type definitions must pertain to either an alias, array, or structure data type construct and conform to the equivalent Praxis syntax (refer to the Praxis primer in Section 8.3). The three forms allowable are:

1

1

Page 33

٠

class: ALIAS

//type (alias\_name) (type\_name) [initially (init\_value)]

where alias\_name is the alias type being defined; type\_name is either a basic type or a previously declared user-defined type which the alias type is being defined in terms of; and init\_value is an optional initial value assigned to the type. (Initialization is only provided for alias types.)

class: ARRAY

//type (array\_name) [packed] array (no\_elements) of (type\_name)

where array\_name is the name of the array; packed is an optional parameter which indicates that the allocation of array elements in storage is packed or most efficient (unpacked is default); no\_elements is the number of elements; and type\_name is either a basic type or previously declared user-defined type.

class: STRUCTURE

//type (structure\_name) structure

(component\_name) : (type\_name)

(component\_name) : (type\_name)

(component\_name) : (type\_name)

endstructure

where structure\_name is the of name the structure: component\_name is the name of an individual component; and type\_name is a basic or user-defined type which can be used to define a component. The number of components in a structure definition is not restricted.

•

The user may place popular user-defined type declarations in file and have FSM modules access these type separate а definitions through the INCLUDE file statement. This eliminates repetitiously defining the same data types in a the waste of series of FSM modules. The //INCLUDE statement may appear anywhere within the initial portion of the FSM module; however, the type definition file must be attached (included) before anv definitions appear in type or variable declaration of its statements in the FSM module. To ensure against a fatal compilation error, it is best to place the //include line prior to all type declarations in the FSM module. The type declaration file must reside on the same directory where the FSM modules are directories whose logical names are FSN\$INCLUDE\_0 or to FSM\$INCLUDE\_4.

A short example to clarify the use of user-defined types in a FSM module has been provided.

```

//type pinteger_2 integer_2 initially Ø

//type longstring packed array(512) of pchar

//type db_mailbox structure

mb_length : pinteger_2

mb_seqno : pinteger_2

mb_time : integer_4

mb_data : longstring

endstructure

```

Note that the types "pinteger\_2" and "longstring" were defined before they could be used in the structure declaration. The two declarations may have been defined in another external file and attached to the above list of type declarations through the "//include (file\_name)" statement. However, this approach is

2

.

only valid if the separate file is included before the structure type is declared. If the first two types were not declared before their appearance in the "db\_mailbox" declaration, a compilation error would have resulted. The rest of the types used in the module are either basic types declared by the parser (integer\_2 and integer\_4) or types defined in the file STANDARD.ISM (pchar).

The comment delimiter in the first part of an FSM file is a vertical bar (!); all comments and the end-of-line are passed through as text by the parser whenever the comment delimiter is present. In the <u>procedures</u> part of the FSM file, the Praxis comment delimiter (double-slash) should be used after the line "//procedures" which inititates the second part of the FSM file; double-slash is no longer recognized by the parser as a line delimiter.

In summary, the structure of a FSM source file consists of a first part where lines beginning with a double-slash indicate the action to be performed. This initial part consists of a declaration section starting with a module-name line followed by lines which define all user-defined types, and then declare all variables used by the FSN module. Data type declarations are accomplished by attaching external type definition files to the FSM module and/or defining the data types themselves within the module. Following type definitions, inputs, input parameters, internal variables, state variables, outputs, and output parameters are declared. The current implementation of the

2

:

parser does not require that declaration lines appear in any specific order, but a user-defined data type must be defined before it is used in a variable declaration or in another data type declaration. In any case, it is advantageous to follow the order in which the type definition and variable declaration lines are specified in Table 1, for it greatly enhances clarity. The second section of the first part normally consists of optional preprocess statements, followed by as many condition-action sets as there are lines of the state table, followed by optional multimatch and no match actions, followed by optional postprocess statements, and ending with a line which inititates the procedures declarations. The second part of an FSM source file is written strictly in Praxis and normally consists of a set of procedures. The file ends with an end-of-line (EOL) character, which is generated automatically by the carriage-return key on a terminal; no other terminator should be used.

'n

<u>Composing Source Files</u>: In composing FSM source files, a number of additional considerations can be used to produce compact modules and avoid programming errors. The following factors should be carefuly noted by the user.

(a) Upper and lower case: Upper and lower case variable names are not distinguished by Praxis, except in the values of constants or variables of type "char" and "pchar". For the convenience of the user, all alphabetic string values are converted to upper case so that the string "abcd" is regarded as equal to the string "ABCD".

(b) <u>Predeclared variables</u>: All variables and parameters employed in condition and action statements of an FSM source file must be pre-declared, with the exception of certain variables that are pre-declared by the parser and are available in all modules. The pre-declared variables which may be accessed by the user are:

| Variable      | Type    | Explanation                                             |

|---------------|---------|---------------------------------------------------------|

| curs          | string  | current state of the module                             |

| nexts         | string  | next state of the module                                |

| first_entry   | boolean | flag set true only on<br>the first cycle of a<br>module |

| compute_delay | integer | simulated computing-<br>delay in ticks                  |

| output_delay  | integer | simulated output<br>delay in ticks                      |

The (implicit) identifier-token for these variables should be treated as "internal". The global variable name\_curs, where "name" is the module name, is the global variable written to common memory corresponding to the local variable "curs".

The role of "curs" and "nexts" is obvious. By predeclaring the type of the state to always be "string", the user is free to choose names for the states that are convenient and meaningful in the context of his application. The number of possibilities is virtually unlimited. Using state names that have meaning greatly

: : :

simplifies programming and reduces programming errors.

5

By testing the variable "first\_entry" in a condition statement, the user can predefine the initial state and internal parameters of a module in the corresponding action statement so that the module is self-initializing.

Output\_delay is the number of ticks that the output is delayed each time a module is scheduled. This emulates a communications delay; if the output delay is greater than the scheduling delay, the module may receive new information from common memory before its previous output has been written. Compute\_delay is the number of ticks (in addition to the output delay) that the output is delayed by emulated computation; this variable may be defined within a procedure so that the delay depends on which state-transition is begin emulated. In contrast the output-delay, a compute-delay will also delay the to scheduled reading of variables from common memory whenever it is longer than the scheduled delay. In this case, the next read cycle occurs immediately upon expiration of the delayed writecycle. The initial value of these variables is zero ticks (on every activation).

(c) Further discussion of the "state" variable: The values of state variables are both written into and read from common memory. Although this manual has emphasized that no module

The scheduling interval is specified in the building step (see Section 4.3).

should input and output the same variable, there are moments when the internal activity of individual modules needs to be monitored to ensure that these modules are running correctly (or running at all). For example, in the current implementation of common memory, an FSM would go to sleep if its input variables do not implementation since, in theory, change. This is a practical inputs of a state machine determine its outputs; and if the inputs and outputs of a state machine do not change, it serves no purpose to continue cycling through the state transition table of However, with the utilization that machine. of internal variables in the HCSE, output values may change in response to internal activity such as an internal counter. The situation would result with the module being put to sleep, even though the states of the FSM are still in transition. This is a common occurrence in the HCSE and one of the motives behind designing the "state" variable. By declaring locally processed variables as "state", intermediate variables will be represented as input values which will subsequently cause module deactivation (that is, if state variables do change).

(d) Local and global variables: Varables declared within procedures are local to these procedures. Variables declared by the identifer-token "internal" are local to the module produced by an FSN source file but are global with respect to the

Another way to activate a sleeping FSM is to call the subroutine CM\_WAKE\_FSM. (see entry (k) for subroutine descriptions)

procedures within it. A variable declared as "inputs", "inparameters", "outputs" or "outparameters" are stored in common memory and hence are available to all other modules of the emulation. Variables declared as "state" is stored in common memory, but the variable is only intended for a single module to read and write. The predeclared variable "name\_curs" is also stored in common memory at each write cycle and is available by this name to all other modules ("name" denotes the name\_token of the FSM file).

(e) User-defined types: User-defined type declarations between different modules should be consistent. If individual modules define the same type name with different attributes, only the first definition passed into common memory will be used in the emulation. In addition, users are not permitted to modify the type definitions of basic types (see section 4.1). Any efforts to do so will be ignored. In either case, the appropriate error message will be output to the screen while the emulation continues to run unhindered.

(f) Variable-naming in FSM source files: A variable of the same name and type identified as an "output" in one FSM source file and "input" in another FSM source file will automatically be passed between them through common memory in the emulation. This is all that is required in order to transmit information between two modules through common memory. Otherwise, common memory is entirely transparent to the user. While this feature is very valuable, it also requires that a variable-naming convention be

2

. .

adopted in advance so that different users will write modules which are compatible. Even slight differences in variable names (aside from case) will result in communication failure; the variables will be stored in common memory, but under different names; if two modules happen to use the same variable name for different purposes, an unintended communication may occur (although this will not happen if one of the variables is identified as "internal"). Only those variables identified as "inputs", "inparameters", or "states" will be retrieved from common memory on each scheduled read cycle, and only those variables identified as "states", "outputs", or "outparameters" will be written on each scheduled write cycle. Undeclared common memory variable names used in a module. will result in fatal compilation or linking erors. The data dictionary capability (Section 6) is very valuable in identifying such discrepancies. should never be any need to declare the same variable as There both input and output of a module (except in the case of "state" variables). To do so will result in errors during compilation and linking. No two modules should declare the same variable as a state, output, or outparameter. This will not necessarily produce error messages but may result in undetected overwrite conflicts in common memory.

5

(g) Syntax of condition/action statements: In Praxis, the logical operator (=), used in condition statements and declaration sections, is distinguished from the equivalence operator (:=), used in action statements, by a preceding colon.

•

Condition statements are sequences of boolean expressions (separated by semicolons) while action statements are sequences of complete Praxis statements (also separated by semicolons); a condition statement line is not a valid line of a Praxis program.

(h) Procedure arguments: The arguments lists of procedures declared in an FSN source file should always be empty, as denoted by the empty argument list "()" following the procedure name in the declaration and in all procedure calls within action statements. In view of the scoping rules (see (d)), procedure arguments should never be necessary. On rare occasions, it is useful to declare a variable as global to all procedures in an FSM source file without declaring it as an "internal" variable, e.g., a two-dimensional array. This can be achieved by including a valid Praxis declaration statement prior to the first procedure declaration in the FSM file.

(i) Line continuation: No line continuation character is provided in the first part of an FSM source file. Up to 132 characters are permitted on a source file line, however. In almost all cases, statements can be separated to appear on succeeding lines with the initial statement containing the identifier-token. In fact, a block of equivalent FSM statements needs only the first line to contain the identifier-token; all succeeding lines with blank identifier-tokens are automatically associated with the last identifier specified. However, identifier-tokens may appear in as many lines as the user wishes. Thus, a long state transition condition may appear on multiple

2

. .

lines following a "conditions" token and/or multiple actions for a given condition can be stated on multiple lines following an "actions" token. However, an action line is always associated with the nearest preceding set of condition lines.

5

(j) Use of preprocess and postprocess variables: Preprocess statements are useful when different values of a particular function of the input and current state values may trigger different state transitions. Defining the value of a declared "internal" or "state" variable to equal this function, the values of the variable may be tested in successive condition statements -- e.g., state transitions may depend on the range of the sum of two real-valued input variables. Similarly, part of an output computation may be common to all state transitions and thus may be most readily placed in a "postprocess" statement. Intermediate parameters in this computation must be declared as internals, states, or through a procedure call.

(k) Default for multimatch and nomatch: If no "multimatch" or "nomatch" actions are provided and one of these conditions occurs, then no change will occur in the module state or parameters. If possible, the conditions statements of a module should be complete and mutually exclusive.

(1) External procedures: Procedures and functions from the libraries described in Section 3.2 are automatically retrieved when they are called from within a module. The following are of particular utility:

TST(stringl,string2): a boolean function which is true when the value of stringl is equal to the value of string2.

NTH \$SORT (real expression): A real function which returns the square root of its argument. Similarly SIN, COS and ATAN2 may be accessed.

MTH'\$RANDOM(iseed): a real function which returns a random number approximately uniformly distributed between 0.0 and 1.0. This is called with a seed which is initialized with an integer and thereafter is called with the new seed returned by the function, i.e., the seed must be 'static'. This is useful in emulating random events.

CM\_TICKSPACING (): a real function which returns the current tick-spacing in seconds (tickspacing is currently 0.1 seconds).

CH\_GET\_TIME(time,ticksize): a procedure which returns the emulated time in ticks (integer) and the tick-spacing (real). This is useful for wall-clock synchronization of the emulation and for emulating scheduled startup times.

CH\_WAKE\_FSM(n\_fsm\_name,h\_fsm\_name): A procedure whose function is to reactivate non-cycling FSM modules. As discussed earlier in (d), common memory was provided with a built-in safeguard that would force an fsm module to sleep (become non-functioning) if it continuously received unchanging input. A call to CM\_WAKE\_FSM

2

from a module will override the above disabling mechanism and force the module through its read and write cycles on a given tick. The parameters n\_fsm\_name and h\_fsm\_name (name and integer pointer of the fsm which is stored in common memory) are automatically assigned when an FSM module is parsed.

÷.

CM\_LOGGING\_ON(newflag, prevflag) A procedure which controls whether all variable transitions are logged in logging files. The parameter newflag is a boolean variable passed into the procedure and is true if system-wide variable logging is to be performed. Prevflag is also a boolean variable which holds the value of the previous logging state.

CI1\_LOG\_VARIABLE(iptr,newflag,prevflag) A procedure which controls whether specific variables are logged. This procedure should be used only when system-wide logging is disabled. The parameter iptr is an integer handle which points to the location of a specific variable in common memory. If newflag is true, logging for the variable represented by iptr will be enabled. Prevflag indicates the previous logging state of that variable.

CN\_DISABLE(fsm\_name,fsm\_handle) This procedure disables a specific FSM module so that it can no longer cycle through its state tables, even if input values change. The name of the FSM integer handle pointing to the location of the FSM name in common memory, is passed into the procedure. CM\_EMABLE(fsm\_name,fsm\_handle) This procedure enables a specific FSM module that has been disabled. However, this does not guarantee that a module will cycle through for it may be asleep (caused by unchanging input values). The name and integer handle are passed in as parameters.

Procedures for external file manipulation are also available through the Praxis textio library (see Section 8.3). Further library procedures and functions are documented in the Programmer's Manual.

4.2 Parsing State Machine Modules (PARSE, PRAXIS)

The result of the previous section is a file or collection of files in the user's current working directory with type FSN, for instance

#### MODNAME.FSM;version

The parser translates this into a Praxis source file in HCSE format; the command syntax is simply

#### PARSE HODNAME

The parser will automatically use the most current version of MODNAME.FSM, and will produce a file

#### -- MODNAME.PRX;version

in the current working directory with a version number one

greater than any previous file by this name. The parser checks for type declarations errors and outputs several different error messages. A common message is

Error: Non-existent (construct\_component) type (construct) name was: (name) (construct\_component) type was: (type)

5

which indicates that a type "name" was being defined in terms of a "type" that did not exist. "Construct" indicates whether the declaration was an alias, array, or structure definition and "construct\_component" describes the particular component being defined (type, array element, or structure component). Remember that a type must be defined prior to its appearance in other subsequent declarations. If the user attempts to modify a basic type (see section 4.1), the following is outputted

Error: Illegal to redefine a built-in type Type name was: (type) Only first declaration will be used

with the "type" name returned to the user. If the user attempts to redefine another user-defined type previously declared, the parser outputs the error message

Error: Duplicate type declaration Type name was: (type) Only first declaration will be used

where the type name is again returned. If the parser cannot find a specified INCLUDE type declaration file, the message

2

Error in file name in an include statement File name was: (file name) will be printed on the terminal screen. Errors in FSM syntax will also cause an error message. If the parser is unable to recognize a token in the FSM code, the message

#### Unrecognized token in line - (line text) Token was (token)

would be displayed on the user's terminal returning the actual line and token causing the error. All errors should be corrected in the source file and the parser should be run again before proceeding. If no error messages occur, the module should be compiled with the command

#### PRAXIS MODNAME

The praxis compiler will automatically use the most current version of MODNAME.PRX and produce files

#### MODNAME.CBJ;version MODNAME.SPS;version

with appropriate version numbers in the current working directory. The second file is a Praxis synopsis file used at build time to define the calling sequence of the Praxis funtion. Praxis error messages are described in Appendix E of the Praxis Language Reference Manual (see Section 1.3) and in the on-line file PRAXIS.DOC. Errors should be corrected in the FSM source file, but the PRX file produced by the Parser may be consulted for assistance in debugging if necessary. All errors should be

2

.

-

See page 23.

•. ••

traceable to the FSM source file, as there are no known Praxis errors that can be introduced by the parser.

#### 4.3 Building Processes (DICT, BUILD)

The previous steps are performed for each of the modules in the user's application, resulting in an OBJ and SPS file for each module. At this stage, it is desirable to produce a data dictionary to assure that all of the modules use a consistent set of variable names. If the module names are MOD1, MOD2, ..., MODN, then the command

#### DICT MOD1, MOD2, ..., MODN

will display a data dictionary at the user's terminal. The standard keyboard commands CTRL/S, CTRL/Q can be used to suspend or continue the listing; this may be directed to a file by first issuing the system command

define/user SYS SOUTPUT DICT.LIS,

which produces the file

#### DICT.LIS; version

in the user's directory. The dictionary begins with a listing of () all user-defined types declared in the FSM modules, followed by a

SYS \$OUTPUT may be defined to any file the user wishes. The filename DICT.LIS was used in this example for convenience.

set of variable descriptions which are referred to as dictionary entries. The format of each dictionary entry is

(variablename) (type) Written by : (modulename) Read by : (modulename) comments: (comments from variable declaration lines)

The dictionary program recognizes descrepancies between the type declarations of different modules. If an equivalent type name is given inconsistent definitions in two different modules, the message

Conflicting definitions for a user-defined type in (modulenamel) and (modulename2) Type name: (typename) Latest definition will be given

will be outputted. In addition, the dictionary program also recognizes type conflicts in the variable declarations of different modules. The message

Type conflict (module name) Changing type from (type1) to (type2) of (variable name)

will be printed prior to the dictionary listing for each error. In addition, the user should survey the list for spelling errors (which will generate separate entries), variables that have no reader or writer (which often indicates a failure to link two modules through common memory), and variables with multiple writers (which will lead to overwrite conflicts). Since comments are carried through from all modules, inconsistent comments for a variable may indicate that the same variable name or variable has been unintentionally given different meanings in different modules. The data dictionary is very valuable for debugging. All FSN modules should be corrected, if any of these errors are noted, before proceeding.

The data dictionary only lists those variables which will be communicated through common memory (i.e., inputs, inparameters, and internals are not passed through common memory, nor are any variables defined within the procedures of a module. Any errors remaining in these variables must be determined at run-time or through the logging list (Section 4.7). Since only those variables in common memory can be monitored, the user must declare all variables that are to be monitored as "state" ,"outputs", or "outparameters" in the module where they are defined. Outputs of this type may appear legitimately in the data dictionary with no readers.

Under VIS, object modules must be linked in order to produce executable process image files. The versatility of the HCSE is greatly enhanced by the possibility of grouping the modules of an emulation into subsets which are linked and later executed as independent processes. The BUILD command constructs processes from groups of modules.

The user is free to decide on what basis the set of modules for an emulation should be partitioned into groups. Traditionally, all modules might be linked as a single group into one process. Another possibility is to link simulation and

.

.\*

emulation modules as separate processes. A third possibility is to group modules according to the emulated processor (computer) on which they are to be implemented, i.e., a separate process for each piece of hardware. Grouping by level in the hierarchy is another possibility.

Since different processes may run on different terminals, there is the possibility of grouping processes according to the terminal on which they are to be run. For instance, one terminal might run the emulation monitor display, while another might emulate (at actual speed) an operator's console, graphic display, or device interface. As described in the <u>HCSE Applications</u> <u>Guide</u>, a physical device with a serial interface (such as a robot) can actually be operated by the emulation while running its own process! The design of shared memory to support this sort of operation enormously increases the power of the HCSE over conventional simulation techniques.

Another consideration in grouping modules is that logging of variables is done on a "per-process" basis, so that the timing, computational burden, and common memory traffic within and between different processes can be readily monitored.

In order to link MOD1, ..., MODM, (M<N), in the preceding example into PROC1, the syntax of the BUILD command would be

BUILD PROC1 MOD1/interval1, MOD2/interval2, ...,

1

The ellipsis (...) are only notational; this is not a feature of the BUILD command.

: :

#### MODM/intervalm

Ϊ,

where intervall ,..., intervalm are integer constants which denote the scheduling interval (in ticks) of each module. As described in Section 2.3, this defines the rate at which each module takes inputs from common memory. Unless the compute\_delay and output\_delay variables are used (Section 4.1), a module writes its outputs on the same cycle as it reads. Compute\_delays longer than the scheduling interval simply cause a postponement of subsequent reads; in this case, synchronization of the reading-rates of various modules may not be maintained indefinitely during the emulation.

The scheduling intervals of various modules may significantly affect the run-time efficiency of the emulation because they strongly affect the rate and volume of data transfer in and out of common memory. Thus, modules should be scheduled at the lowest rate consistent with the task or subtask they implement, with the required degree of responsiveness to errors occuring in other modules, and with the emulated computing-time requirements.

In the above example, the BUILD command generates a Praxis file

#### PROC1.PRX;version

in the user's current working directory. The builder also constructs a linker options file

#### PROC1.OPT; version

with the appropriate version number. The process-building step is completed by compiling and linking the above module:

#### PRAXIS PROCI LINK PROCI/OPT

#### which produces the executable process image

#### PROC1.EXE

#### 4.4 Running The HCSE

ĥ

An emulation consisting of K process files PROC1, ..., PROCK is run by starting each process and finally starting the DISPLAY process, which is designed as a special process module that acts like a probe for the ongoing emulation and provides a user \*

# BEGIN PROCI

to start all of the emulation processes. In a hierarchical control system emulation, only the top module will normally proceed, while the others will wait in an "idle" state until receiving their first commands. The BEGIN command reserves sufficient system resources for the emulation. Next, the display

٩.

The emulation can be run in batch mode by omitting the display.

process is run be issuing the command

#### DISP or DISPLAY

This process sends output directly to the user's terminal. The first request is

"Hit any key to start display".