NBS PUBLICATIONS

# NBSIR 79-1756

Measurement Techniques for High Power Semiconductor Materials and Devices: Annual Report, October 1, 1977 to September 30, 1978

F. F. Oettinger, Editor

Electron Devices Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Washington, DC 20234

Issued June 1979

Prepared for partment of Energy vision of Electric Energy Systems ishington, DC 20545 100 U56 79-1756 C.2 NBSIR 79-1756

MEASUREMENT TECHNIQUES FOR HIGH POWER SEMICONDUCTOR MATERIALS AND DEVICES: ANNUAL REPORT, OCTOBER 1, 1977 TO SEPTEMBER 30, 1978 Rolling Bureau of Stanta de SEP 25 1979 Not Acc. Curc BCICO USG 79-1756 C. 2-

F. F. Oettinger, Editor

Electron Devices Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Washington, DC 20234

Issued June 1979

Prepared for Department of Energy, Division of Electric Energy Systems Washington, DC 20545

U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary Jordan J. Baruch, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director

### TABLE OF CONTENTS

### Page

| Exec | cutive | e Summar | y          |                                       | •••             | •  | • | 1  |

|------|--------|----------|------------|---------------------------------------|-----------------|----|---|----|

| 1.   | Intro  | oduction | 1          |                                       | • • •           |    | • | 5  |

| 2.   | Deep   | Level M  | leasuremen | ts                                    | •••             | •  | • | 6  |

|      | 2.1    |          |            |                                       |                 | •  | • | 6  |

|      | 2.2    |          |            |                                       |                 |    | • | 6  |

|      | 2.3    | -        |            | This Year                             |                 |    | • | 7  |

|      |        |          |            | cture Development                     |                 |    | • | 7  |

|      |        | 2.3.2    |            | l Measurement Methods                 |                 | •  | • | 16 |

|      |        |          | 2.3.2.1    | Improved Thermometry for Deep Lev     | e1              |    |   |    |

|      |        |          |            | Measurements                          |                 | •  | • | 16 |

|      |        |          | 2.3.2.2    | Use of Deep Level Measurement Tec     | h <b>niqu</b> e | es |   |    |

|      |        |          |            | to Measure the Isotope Shift of S     | ulfur           |    |   |    |

|      |        |          |            | in Silicon                            |                 |    |   | 20 |

|      |        |          | 2.3.2.3    | Use of Deep Level Measurement Tec     | hnique          | es |   |    |

|      |        |          |            | to Separate the Midgap Sulfur Maj     | -               |    |   |    |

|      |        |          |            | and Minority Carrier Emission Rat     |                 |    |   | 20 |

|      |        |          | 2.3.2.4    | Use of Deep Level Measurement Tec     |                 |    |   |    |

|      |        |          |            | to Characterize the Shallow Sulfu     |                 |    |   |    |

|      |        |          |            | in Silicon                            |                 |    |   | 22 |

|      |        |          | 2.3.2.5    | Use of Deep Level Measurement Tec     |                 |    | • |    |

|      |        |          | 2.3.2.3    | to Study the Variation of the Rel     |                 | -0 |   |    |

|      |        |          |            | Density of Shallow and Deep Sulfu     |                 |    |   |    |

|      |        |          |            | Centers with Implantation Fluence     |                 |    |   | 24 |

|      |        |          | 2.3.2.6    | Artifacts for Comparative Deep Le     |                 |    |   | 24 |

|      |        |          | 2.3.2.0    |                                       |                 |    |   | 26 |

|      |        |          | 0 2 0 7    | surements                             |                 |    | - |    |

|      |        | 0 0 0    |            | Deep Level Transient Spectroscopy     |                 |    |   | 26 |

|      |        | 2.3.3    |            | on of Defects with Device Paramet     |                 |    |   | 27 |

|      |        |          | 2.3.3.1    | Reverse Leakage Current and Forwa     |                 |    |   | •  |

|      |        |          |            | age Drop of Diodes                    |                 |    |   | 28 |

|      |        |          | 2.3.3.2    | Measurement of Minority Carrier L     | lfetin          | ne | • | 31 |

| 3.   | Sprea  | ading Re | esistance  | Measurements                          | • • •           | •  | • | 41 |

|      | 3.1    | Objecti  | ives       |                                       |                 |    |   | 41 |

|      | 3.2    |          |            |                                       |                 |    |   | 41 |

|      | 3.3    | Accompl  | lishments  | This Year                             |                 |    |   | 45 |

|      |        | 3.3.1    |            | reparation Procedures for Radial      |                 |    |   |    |

|      |        |          |            |                                       |                 |    |   | 45 |

|      |        | 3.3.2    |            | reparation Procedures for Depth P     |                 |    |   |    |

|      |        |          |            | · · · · · · · · · · · · · · · · · · · |                 |    |   | 54 |

|      |        | 3.3.3    |            | f Benefits of Specimen Preparatio     |                 |    | · |    |

|      |        |          |            | olishing                              |                 |    |   | 55 |

|      |        | 3.3.4    |            | ecies Dependence on Calibration f     |                 |    | • |    |

|      |        | 0.0.7    |            | nts                                   |                 |    |   | 60 |

|      |        |          | -JFOPC     |                                       | · · ·           |    | • |    |

#### Page

| 4. References                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix A                                                                                                                                                                                                                                           |

| Appendix B                                                                                                                                                                                                                                           |

| Appendix C                                                                                                                                                                                                                                           |

| Appendix D                                                                                                                                                                                                                                           |

| List of Figures                                                                                                                                                                                                                                      |

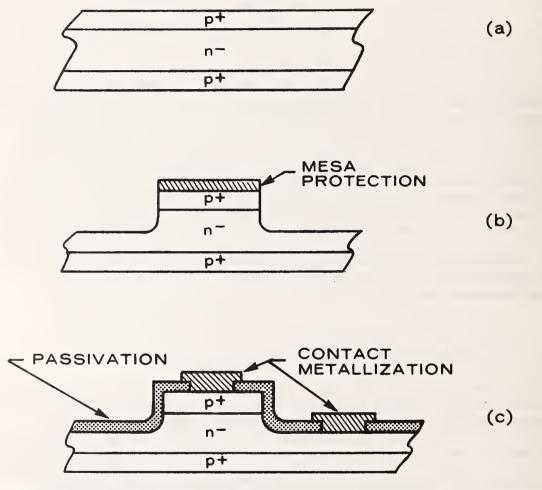

| <ul> <li>2-1. The basic mesa diode processing steps: a) starting wafer;</li> <li>b) mesa protection, junction isolation; c) passivation,</li> <li>contact cut, and metallization</li></ul>                                                           |

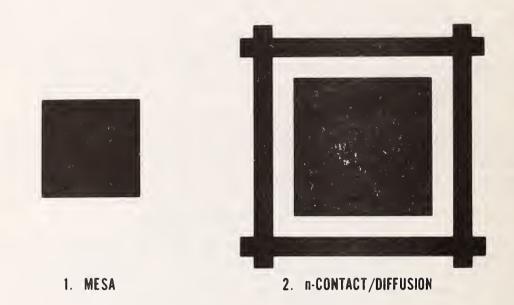

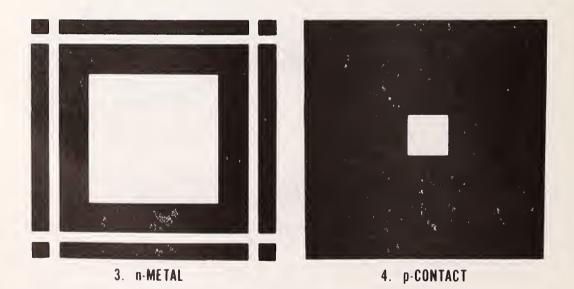

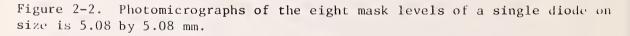

| 2-2. Photomicrographs of the eight mask levels of a single diode<br>on test pattern NBS-20 10                                                                                                                                                        |

| 2-3. Photomicrograph of a mesa diode fabricated with test pattern NBS-20                                                                                                                                                                             |

| 2-4. Thermally stimulated capacitance and current curves measured<br>on a mesa diode fabricated on a $p^+n^-p^+$ -wafer using test pat-<br>tern NBS-20; the heating rate is about 5 K/s                                                              |

| 2-5. Temperature deviation of the thermocouple temperature, $T_{TC}$ ,<br>and the temperature-sensing diode, $T_D$ , compared with a refer-<br>ence temperature, $T_R$ , derived from the calculated sulfur emis-<br>sion rate parameters in silicon |

| 2-6. | Semilog plot of reduced emission rate against inverse tem-  |    |

|------|-------------------------------------------------------------|----|

|      | perature for electron and hole emission from the deep level |    |

|      | centers of <sup>32</sup> S and <sup>34</sup> S in silicon   | 21 |

|      |                                                             |    |

## 2-7. Activation energy and emission coefficient with standard deviations for the shallow level of <sup>32</sup>S and <sup>34</sup>S in silicon . . 23

| 2-8. | Dynathermal capacitance and current responses of a silicon                                |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | $p^{+}n$ -junction diode implanted with <sup>32</sup> S to a dose of 1 x 10 <sup>13</sup> |    |

|      | $cm^{-2}$ and the current response with $^{34}S$ of the same dose                         | 25 |

####

| 2-10. | Wafer maps of the gold acceptor defect density, the reverse |    |

|-------|-------------------------------------------------------------|----|

|       | leakage current, and the forward voltage drop for the gold- |    |

|       | diffused wafer                                              | 32 |

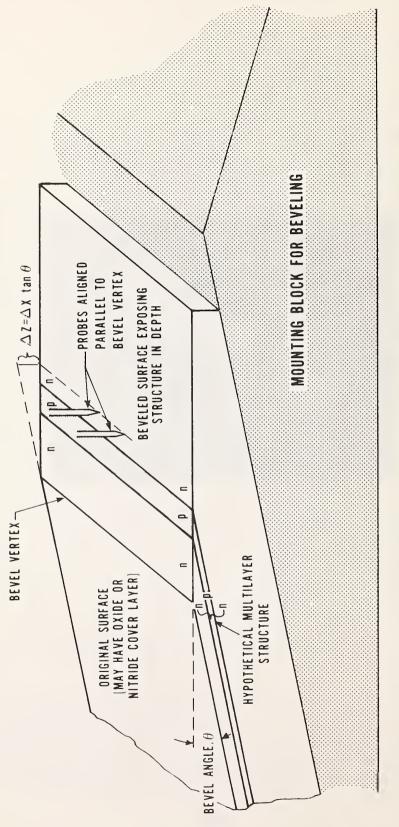

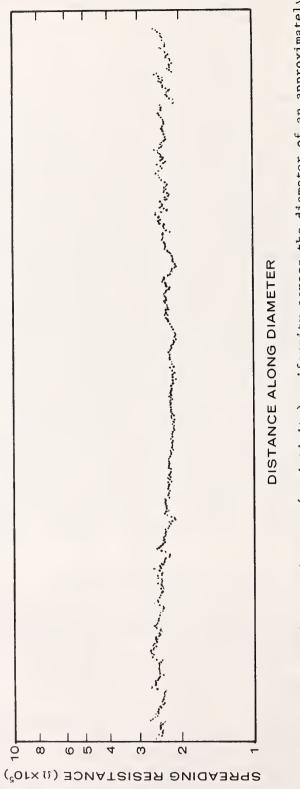

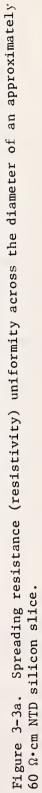

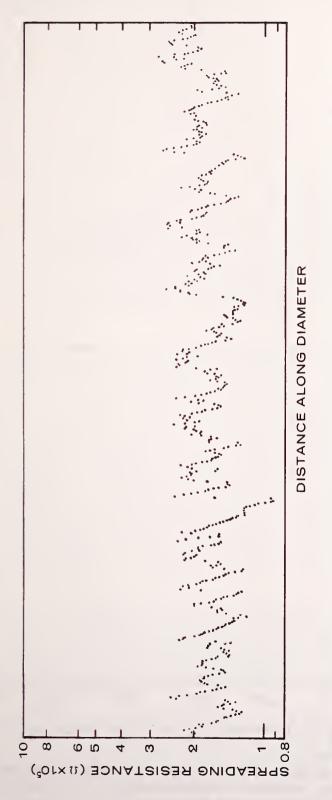

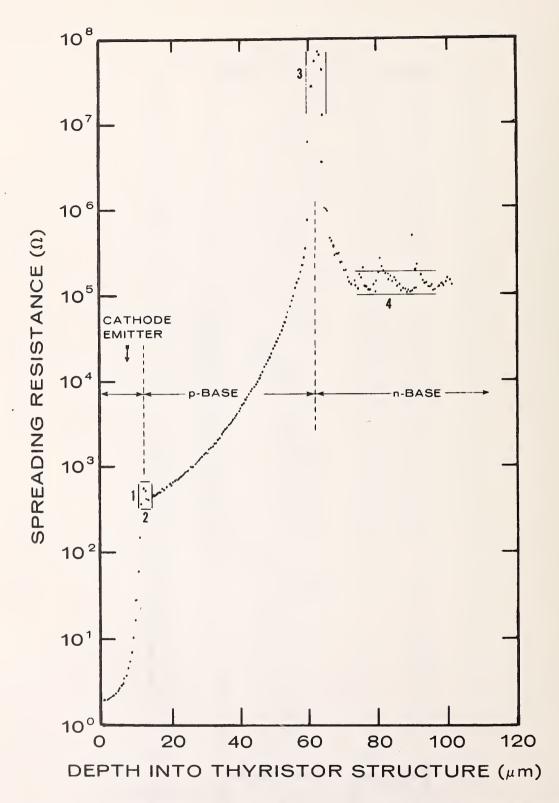

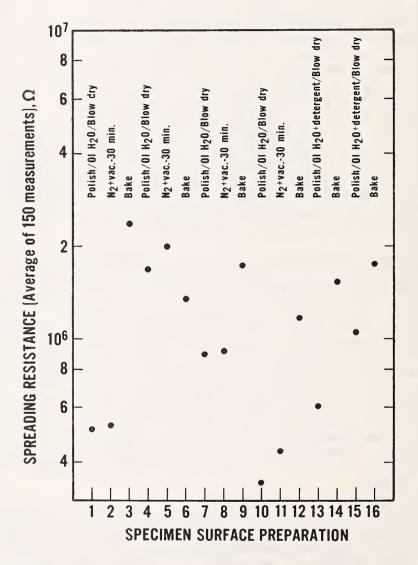

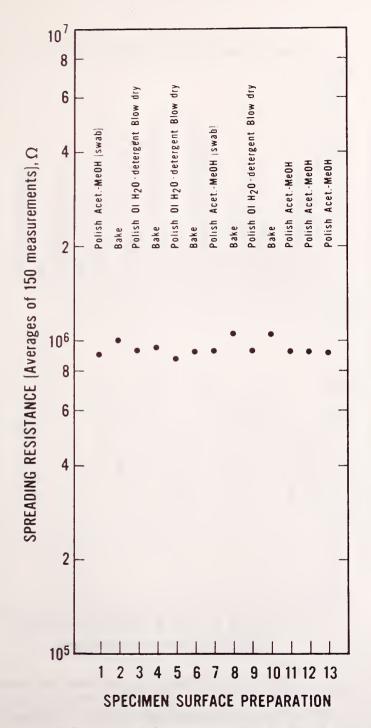

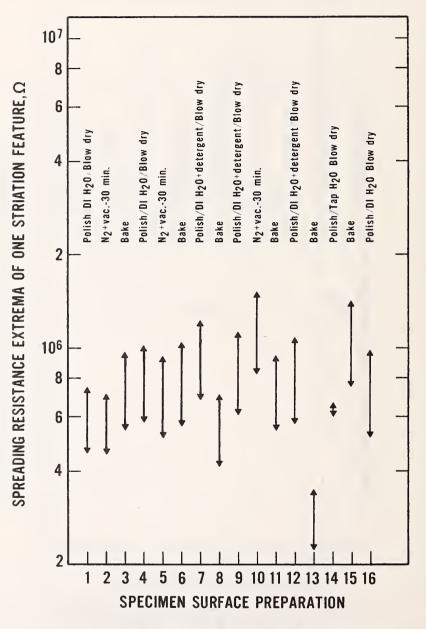

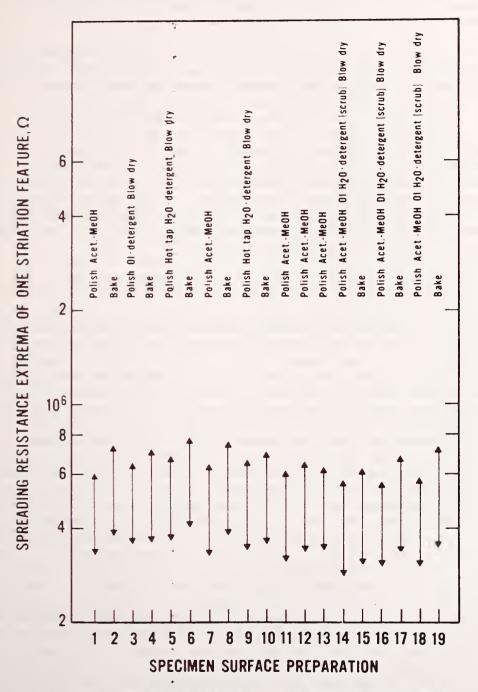

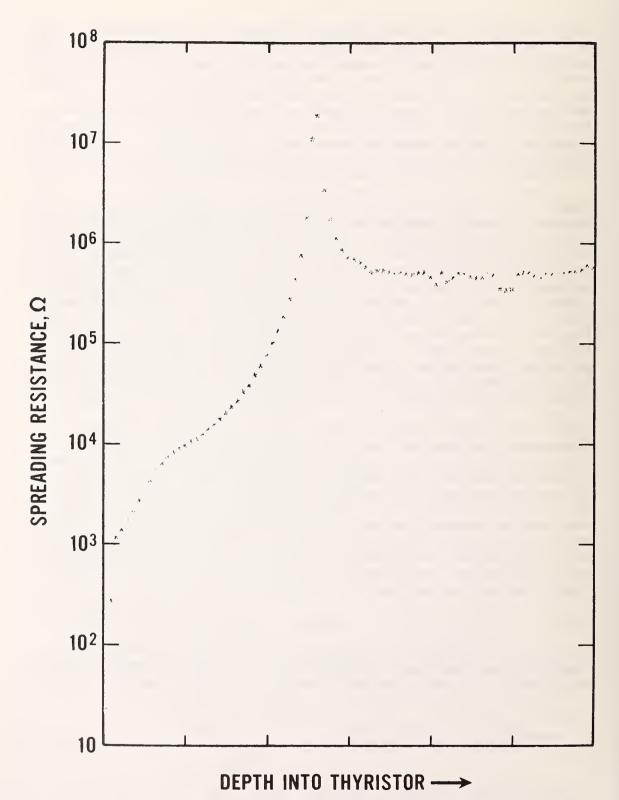

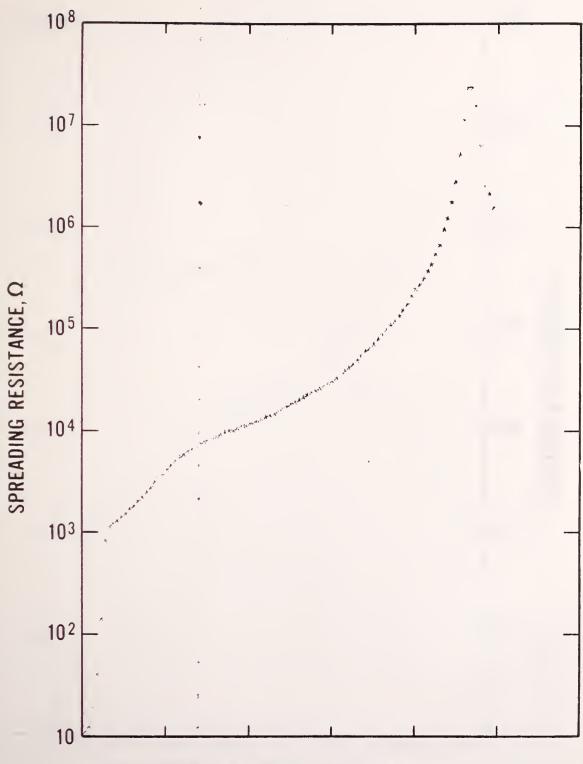

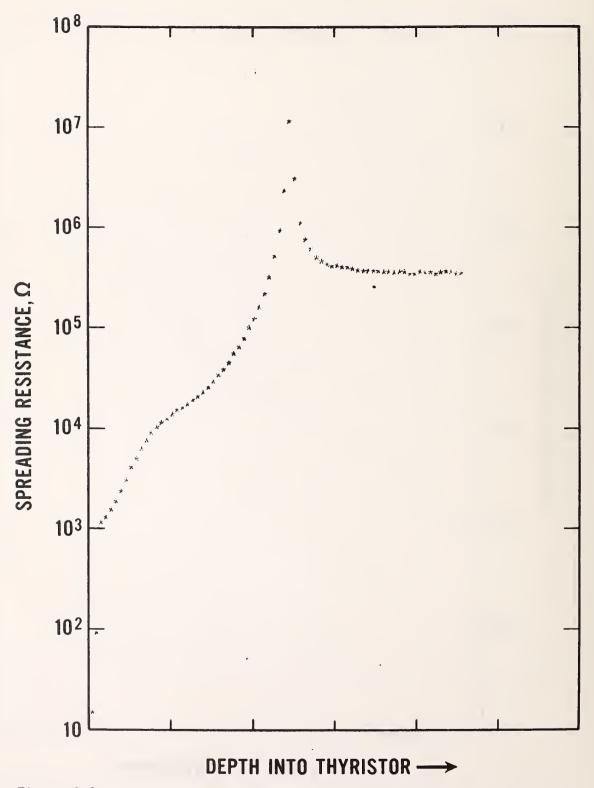

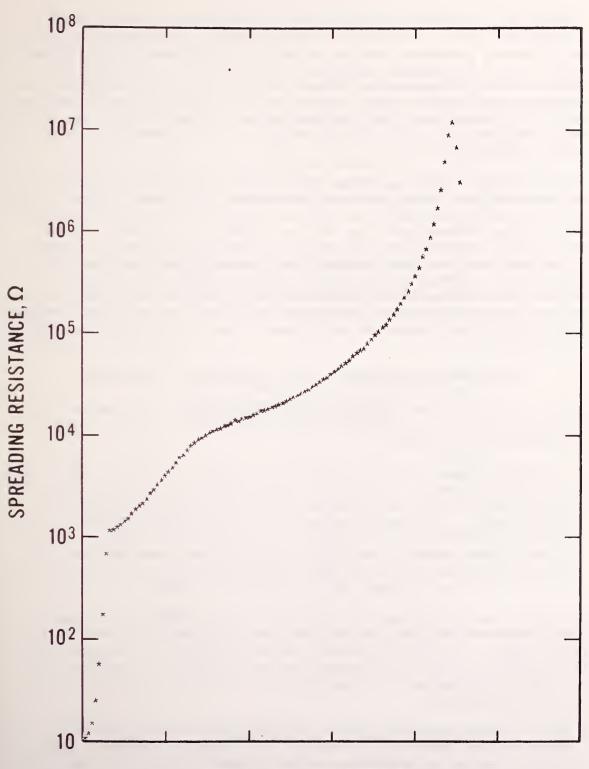

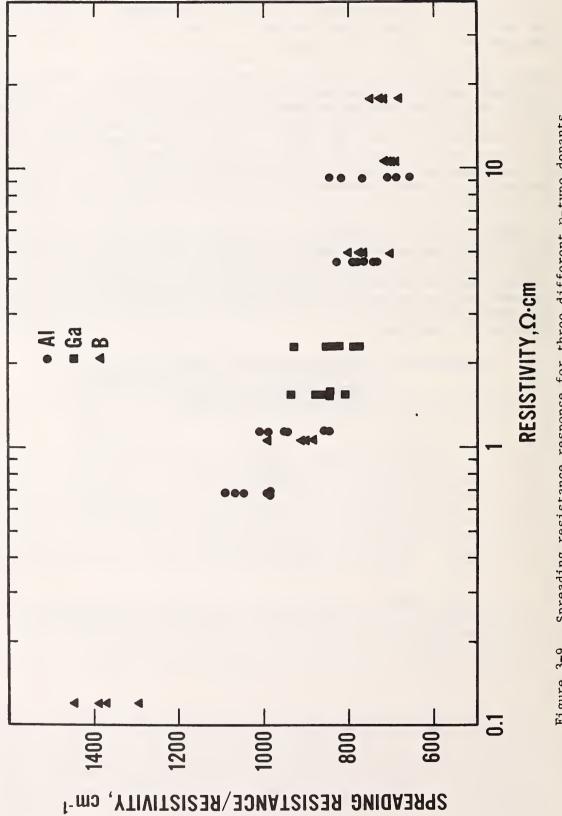

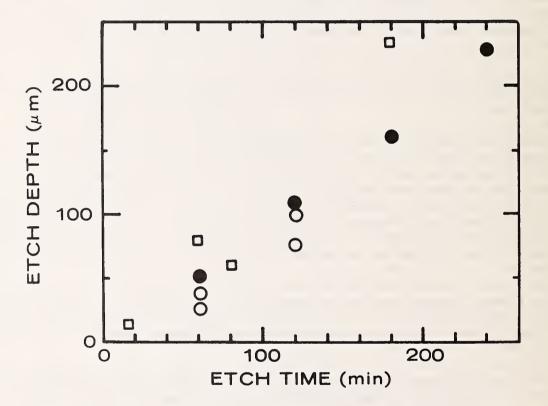

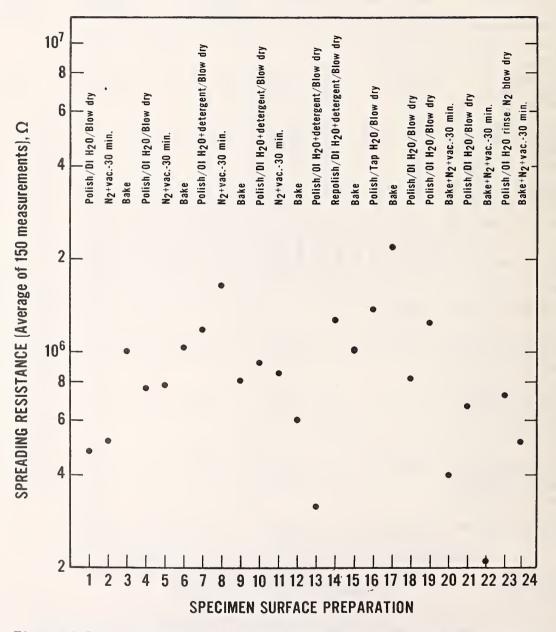

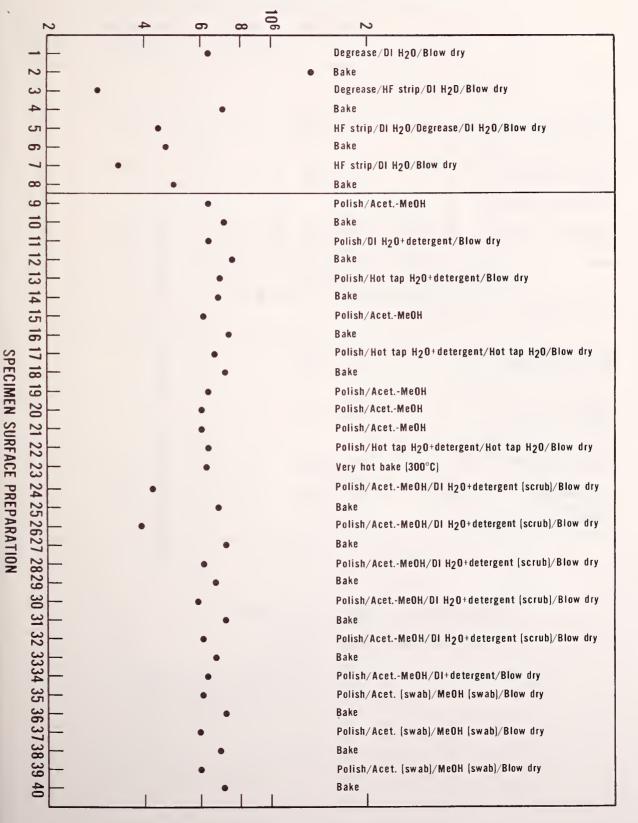

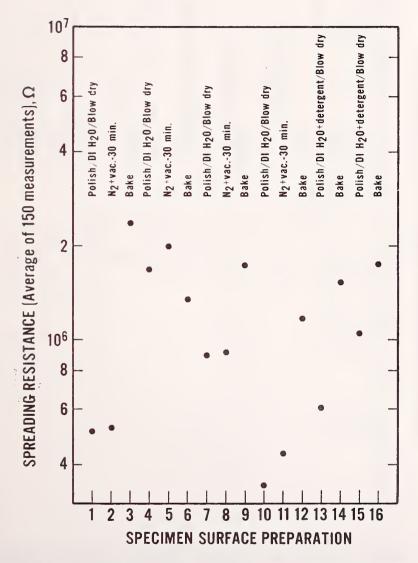

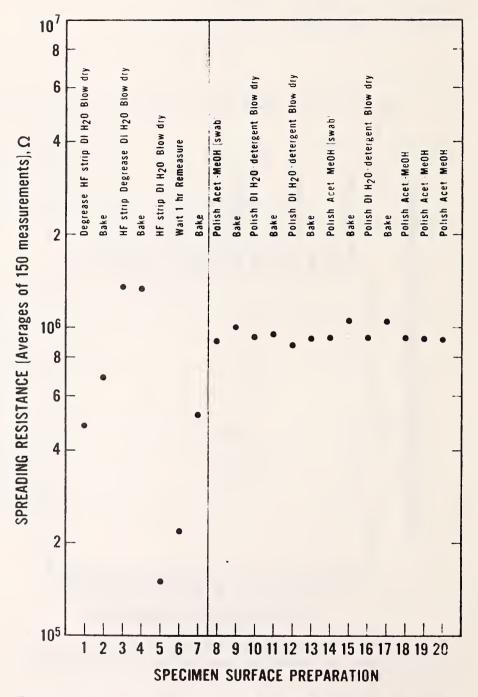

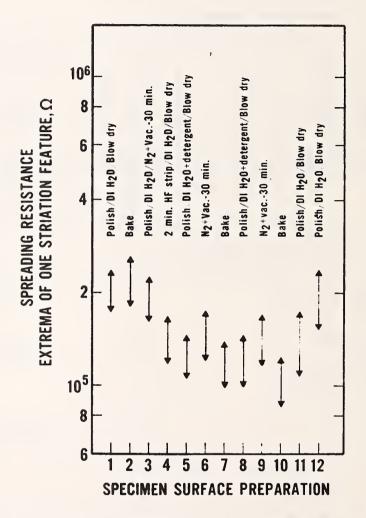

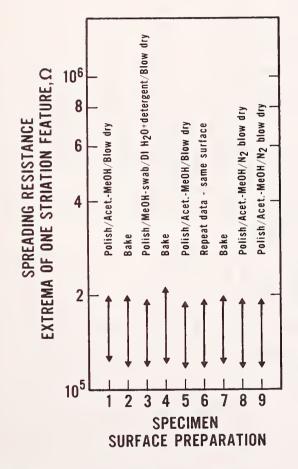

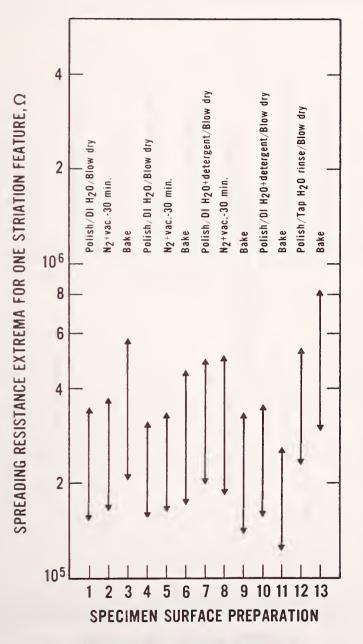

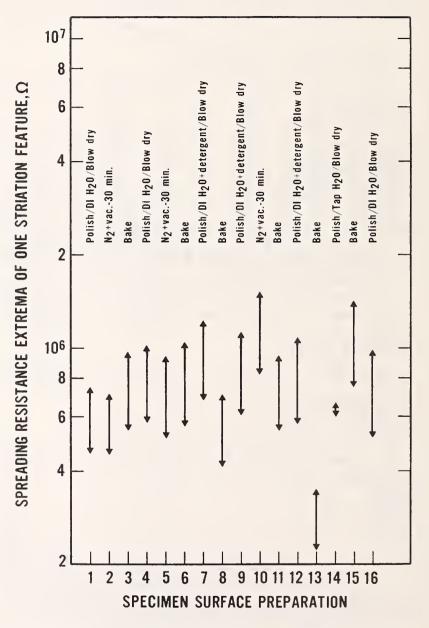

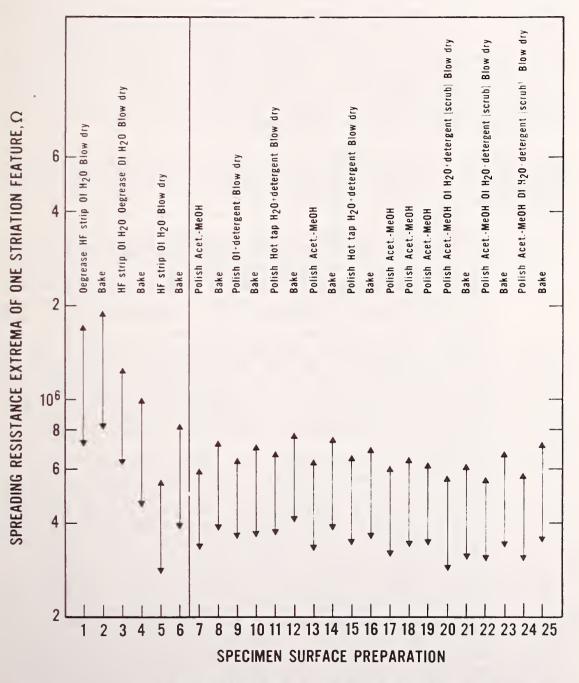

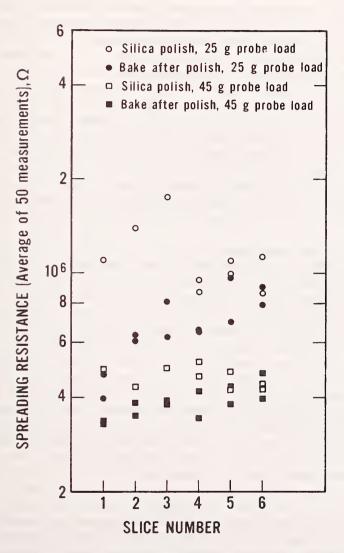

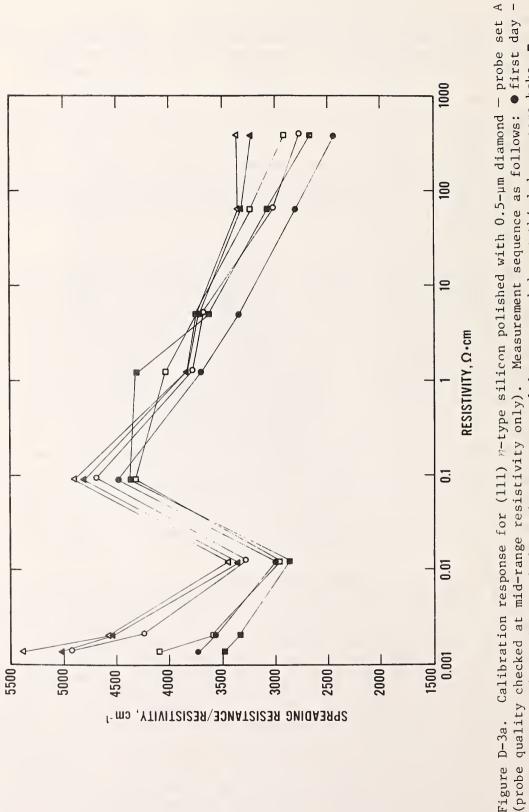

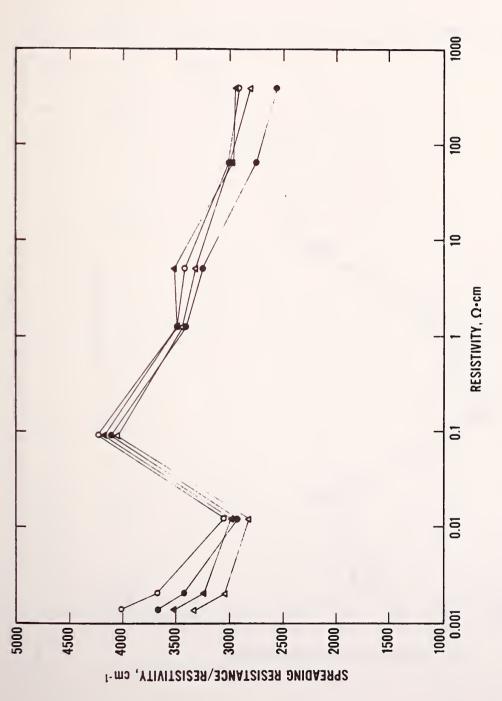

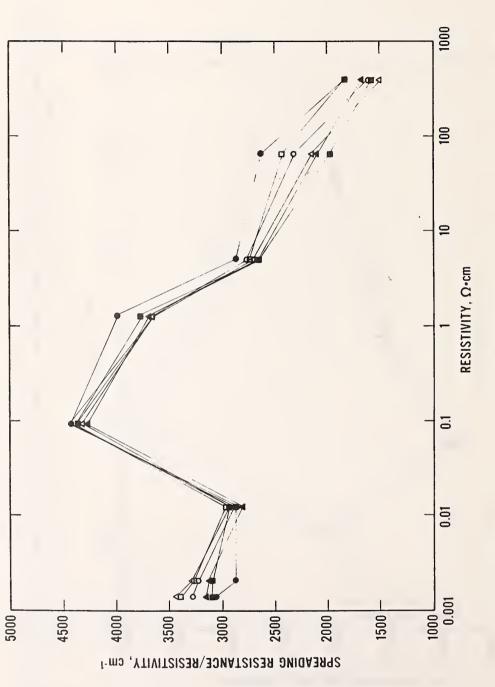

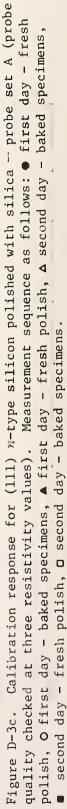

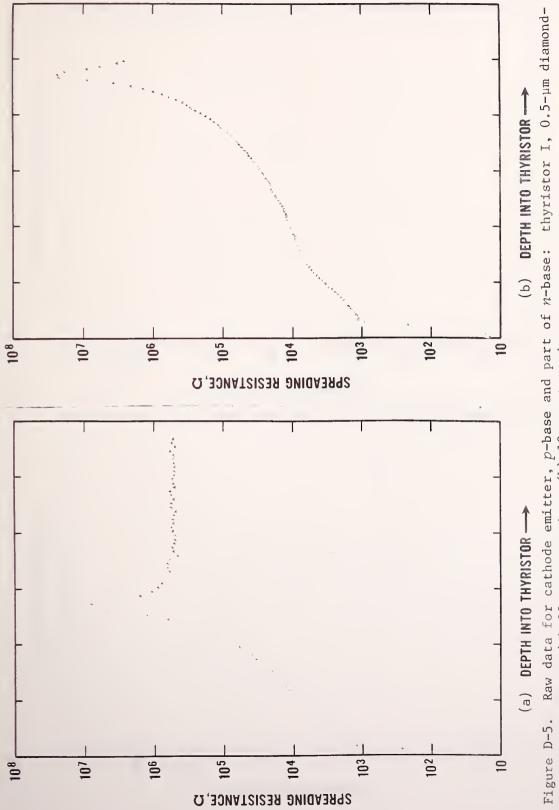

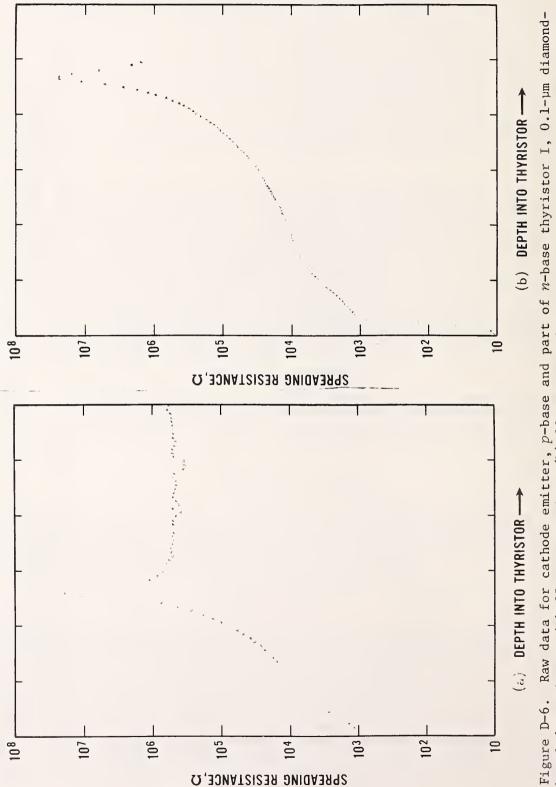

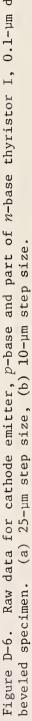

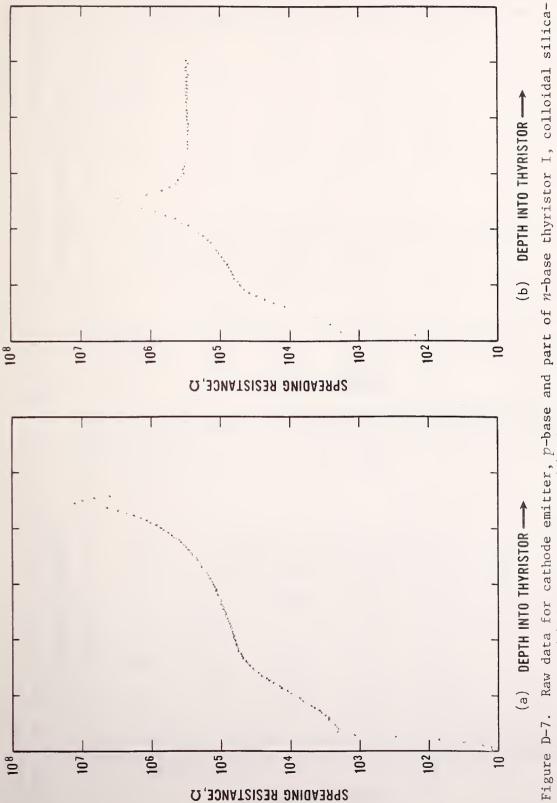

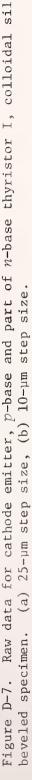

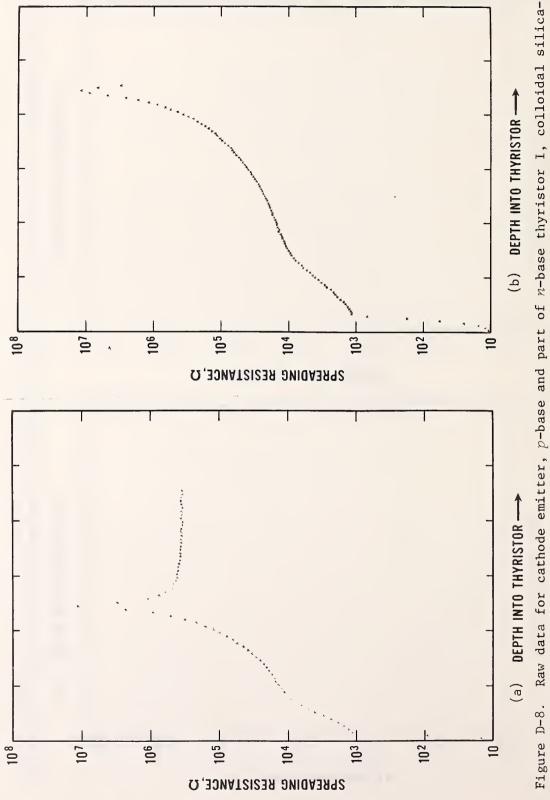

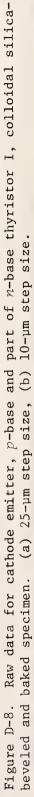

2-11. Wafer maps of the reverse leakage current and the forward voltage drop for the commercial rectifier wafer . . . . . . 33 2 - 12An OCVD response of a typical power rectifier diode . . . . 35 2 - 13. The diode reverse recovery characteristic of a typical 37 2 - 14. Schematic diagram of method used to measure the diode re-38 Wafer maps of the minority carrier lifetime of the com-2 - 15. mercial rectifier wafer determined by the open circuit voltage decay and reverse recovery techniques . . . . . . 39 Wafer maps of OCVD lifetime of two similar commercially 2-16. 40 Silicon chip mounted on beveling block with piston and 3-1. 43 3-2. Schematic representation of a multilayer semiconductor structure which has been bevel-sectioned for depth profiling by spreading resistance probes ....... 44 3-3a. Spreading resistance uniformity across the diameter of an 46 3-3Ъ. Spreading resistance uniformity across the diameter of an approximately 60  $\Omega$  · cm standard float-zoned silicon slice . . 47 3-4. Spreading resistance profile of thyristor structure from 48 3-5a. Spreading resistance average vs. surface preparation: colloidal silica series - 400  $\Omega$  · cm NTD silicon specimen . . . 50 3-5b. Spreading resistance average vs. surface preparation: 0.5- $\mu$ m diamond polish series -- 400  $\Omega$ ·cm NTD silicon specimen . . 51 3-6a. Spreading resistance maximum and minimum vs. surface preparation for one resistivity striation feature: colloidal silica series - 150 Ω·cm float-zoned silicon specimen . . . 52 3-6b. Spreading resistance maximum and minimum vs. surface preparation for one resistivity striation feature: 0.5-um diamond polish series - 150 Ω·cm float-zoned silicon specimen 53 . 3-7a. Raw data for cathode emitter, p-base and part of n-base

Page

v

|       | thyristor I, 0.1-µm diamond-beveled specimen, 25-µm step<br>size                                                                                                              | 56 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3-7Ъ. | Raw data for cathode emitter, $p$ -base thyristor I, 0.1-µm diamond-beveled specimen, 10-µm step size                                                                         | 57 |

| 3-8a. | Raw data for cathode emitter, $p$ -base and part of $n$ -base thyristor I, colloidal silica-beveled and baked specimen, 25-µm step size                                       | 58 |

| 3-8Ъ. | Raw data for cathode emitter, $p$ -base thyristor I, colloidal silica-beveled and baked specimen, $10-\mu m$ step size                                                        | 59 |

| 3-9.  | Spreading resistance response for three different $p$ -type dopants                                                                                                           | 62 |

|       | List of Tables                                                                                                                                                                |    |

| 2-1.  | Activation Energies and Emission Coefficients for Combined<br>and Separated Electron and Hole Emission Rates from $^{32}$ s and<br>$^{34}$ S Midgap Defect Centers in Silicon | 22 |

| 2-2.  | Activation Energies and Emission Coefficients for Electron Emission from the $^{32}$ S and $^{34}$ S Shallow Level in Silicon                                                 | 24 |

| 3-1.  | Resistivity Values of Specimens Used to Test Comparability of<br>Spreading Resistance Measurements on Boron-, Aluminum-, and<br>Gallium-Doped Silicon                         | 61 |

Page

This work was conducted as a part of the Semiconductor Technology Program of the National Bureau of Standards (NBS). This program serves to focus NBS research to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in specifying materials and devices in national and international commerce and for use by industry in controlling device fabrication processes. This research leads to carefully evaluated and well-documented test procedures and associated technology. Special emphasis is placed on the dissemination of the results of the research to the electronics community. Application of these results by industry will contribute to higher yields, lower cost, and higher reliability of semiconductor devices. Improved measurement technology also leads to greater economy in government procurement by providing a common basis for the purchase specifications of government agencies and, in addition, provides a basis for controlled improvements in fabrication processes and in essential device characteristics.

The segment of the Semiconductor Technology Program described in this annual report is supported by the Division of Electric Energy Systems of the Department of Energy (DOE) under DOE Task Order AO21-EES, Amendment No. 2. Previous work reported under this DOE Task was on a calendar year basis. Beginning with this Annual Report, reporting will be on a fiscal year basis; thus there is a three-month overlap between the last annual report and this one. The contract is monitored by Dr. Russell Eaton of DOE. The NBS point of contact for information on the various task elements of this project is F. F. Oettinger of the Electron Devices Division at the National Bureau of Standards. The work reported herein also drew upon the results of studies carried out under other parts of the Semiconductor Technology Program which were funded by the Defense Advanced Research Projects Agency under Order No. 2397, Program Code 7D10, and by the NBS.

#### Disclaimer

Certain commercial equipment, instruments, or materials are identified in this report in order to specify adequately the experimental procedure. In no case does such identification imply recommendation or endorsement by the National Bureau of Standards, nor does it imply that the material or equipment identified is necessarily the best available for the purpose.

Measurement Techniques for High Power Semiconductor Materials and Devices

ANNUAL REPORT October 1, 1977 to September 30, 1978

F. F. Oettinger, Editor

#### EXECUTIVE SUMMARY

This annual report describes results of NBS research directed toward the development of measurement methods for semiconductor materials and devices which will lead to more effective use of high-power semiconductor devices in applications for energy generation, transmission, conversion, and conservation. It responds to national needs arising from the rapidly increasing demands for electricity and the present crisis in meeting long-term energy demands. Emphasis is on the development of measurement methods for materials for thyristors and rectifier diodes. Application of this measurement technology will, for example, enable industry to make devices with higher individual power-handling capabilities, thus permitting very large reductions in the cost of power-handling equipment and fostering the development of direct current (dc) transmission lines to reduce energy waste and required rights-of-way.

The major tasks under this project are (1) to evaluate the use of thermally stimulated current and capacitance measurements and other deep level measurement techniques as a means for characterizing lifetime-controlling or leakage source defects in power grade silicon material and devices and (2) to develop procedures to enable spreading resistance measurements of thyristor starting material and layer profiles to be made on a reliable basis.

Deep Level Measurements — The presence of deep level impurities in semiconductor power devices is a consequence of their unintentional introduction during the wafer fabrication procedure or their intentional introduction in order to adjust the switching properties of the device. In either case, the dominant effect of the deep level is to modify the minority carrier lifetime. Measurement techniques to detect, characterize, and identify such deep levels are required in order to monitor the presence of unintentional contamination or to characterize fully and understand the behavior of intentional ones. The use of such techniques for process diagnostics would enhance the manufacturer's ability to control the quality (yield, reliability, and cost) of his product.

1

The effective utilization of these measurement methods to the design and fabrication of power devices has several prerequisites: 1) the ability to fabricate test structures on starting and in-process material for the purpose of deep level studies, 2) the establishment of well-characterized measurement procedures and methods for analyzing data, and 3) establishment of the relationship between the presence of deep levels and electrical device parameters. Research efforts during this contract period were aimed at satisfying these requirements.

Development of procedures for the fabrication of test structures on diffused thyristor wafers was completed. The basic process consists of mesa formation by plasma etching, passivation with a deposited silicon dioxide, and contact metallization. These fabrication procedures utilize no steps requiring temperatures higher than 400°C. A new test pattern (NBS-20) was designed to implement these fabrication procedures, and resulting devices were evaluated.

Deep level measurement procedures established during the previous contract period were implemented and demonstrated during this contract period. The two levels of sulfur in silicon were used as the measurement vehicle and were characterized in detail using the developed procedures. The critical dependence of these measurements on thermometry has been established, and an improved technique to decrease temperature uncertainties was implemented. Use of the procedures for deep level measurements and the improved precision in temperature measurement enabled the detection of an isotope shift in the midgap energy level of sulfur.

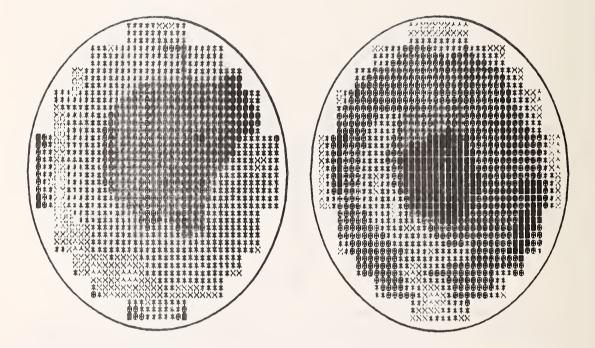

By utilizing the previously developed variable-temperature wafer probing apparatus, a variety of device parameters were measured as a function of wafer position. Wafer maps of reverse leakage current, forward voltage drop, diode reverse recovery lifetime, open circuit voltage decay lifetime, and defect density were made; direct correlations were observed.

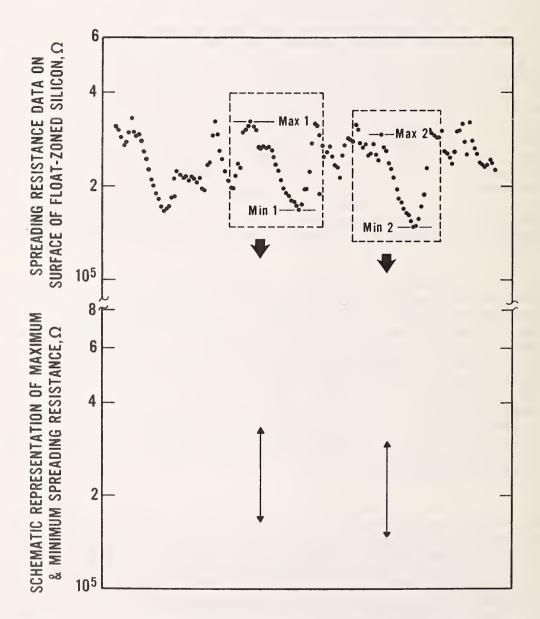

Spreading Resistance Measurements — Knowledge of the resistivity (dopant) variations which exist in a semiconductor structure is of primary importance for use in design and modeling of the structure and for quality control during its fabrication. Most such resistivity variations are intentional resulting from device fabrication procedures such as thermal diffusion or ion implantation. Some, however, are unwanted and are due to loss of process control or to microsegregation effects during crystal growth, as, for example, in the *n*-base region of a thyristor fabricated in float-zoned silicon. The spreading resistance technique, although destructive in that contact damage is incurred, is presently the primary method for measuring resistivity variations in silicon material and devices. This technique, which has been in use for a number of years in the semiconductor industry, is based on the constriction resistance of pressure contacts between small metal probes and the semiconductor bulk material or multilayered device structure of interest. The technique gains its widespread usefulness from a unique combination of performance characteristics: lateral spatial resolution of about 5 µm, effective depth resolution of about 20 nm, and a dynamic resistivity response of 8 or 9 orders of magnitude for both nand p-type silicon. The spreading resistance technique has undergone steady improvement in precision and accuracy. However, it has had noticeable shortcomings, including some that are virtually unique to measurements on thyristors and related high-power control devices. Those shortcomings which related to control of the (111) *n*-type silicon specimen surface to obtain acceptable measurement precision and to calibration of the measurement for *p*-type dopants commonly used in thyristor fabrication were successfully addressed during the contract period.

The repeatability of spreading resistance measurements on high resistivity *n*-type silicon has been observed to be unsatisfactory in many laboratories. The effect of this on power device fabrication is twofold: 1) loss of reliability of measurements of starting crystal uniformity and 2) uncertainty whether apparent shifts in *n*-base resistivity, sometimes observed after device fabrication, are real or simply measurement artifacts. The cause of the unsatisfactory measurement was believed to be improper preparation of the silicon specimen surface which resulted in loss of control of the metal probe-semiconductor contact properties.

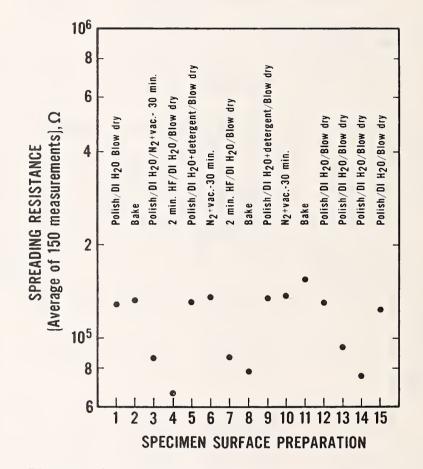

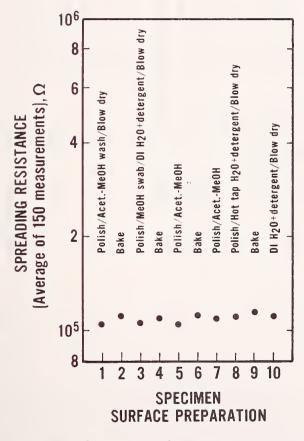

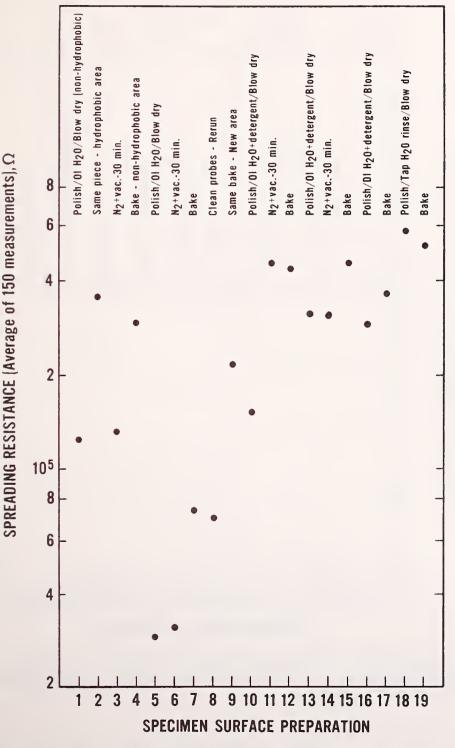

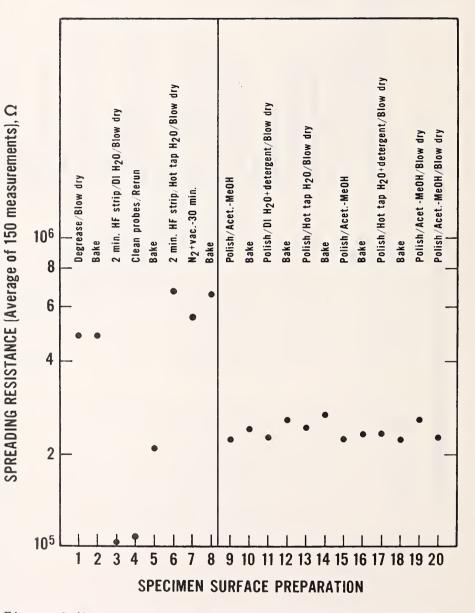

Several methods for preparing the silicon specimen surface were investigated for bulk silicon specimens in the resistivity range from 30 to 400  $\Omega$ ·cm. Polishing with either 0.5- or 3-µm particle size diamond suspended in a nonaqueous fluid was found to be clearly superior to traditional chem-mechanical polishing methods with silica in basic aqueous solution. The superiority obtained by diamond polishing is evidenced by greatly improved reproducibility of average spreading resistance values following specimen repolishing, by less point-topoint measurement scatter on any one specimen surface and by reduced sensitivity of measurements to specimen treatment subsequent to polishing. Of the two polycrystalline diamond polishes tested for top surface polishing, the one with the smaller diamond particle size (0.5 µm) was adopted as the preferred method of specimen preparation. This choice was based

3

primarily on a higher quality specimen surface (lighter scratch damage) obtained with the 0.5-µm diamond.

The use of diamond was also applied to bevel-sectioning of tnyristor devices for depth profiling. However, the beveling process must be done against a harder surface than is used for top surface polishing in order to maintain flatness of beveled surface and sharpness of beveled surface interface. It was found necessary when using such a hard work surface to use a still smaller size diamond,  $0.1 \ \mu\text{m}$ , for beveling to maintain measurement quality. Measurements on diamond-beveled devices retain high repeatability for the *n*-base layer and give good agreement with silica-beveled and baked thyristor sections for the cathode emitter and *p*-base layers.

Tests were made of the equivalence of spreading resistance response on bulk specimens of silicon variously doped with boron, aluminum, or gallium at levels typical of those used in thyristor diffusions. Spreading resistance data acquired during these tests clearly show that boron-doped silicon specimens, which are readily available, can be reliably used to calibrate spreading resistance measurements on silicon doped with gallium or aluminum. It has been customary to assume this equivalence, but it had not been demonstrated previously.

#### 1. INTRODUCTION

This project is directed toward the development of measurement methods for semiconductor materials and devices which will lead to more effective use of high-power semiconductor devices in applications for energy generation, transmission, conversion, and conservation. It responds to national needs arising from rapidly increasing demands for electricity and the present crisis in meeting long-term energy demands. Emphasis is on the development of measurement methods for materials for thyristors and rectifier diodes.

The project is designed to provide, disseminate, and foster the standardization of improved measurement methods required in high-power semiconductor technology, for use in specifying materials and devices in commerce, and by industry in controlling device manufacturing processes, and in designing systems. Application of this measurement technology will, for example, enable industry to: (1) make power semiconductor devices with greater uniformity of characteristics, thus permitting improvements in parallel and series connections of devices for applications from fusion generation to ac/dc conversion, (2) make devices with higher individual power handling capabilities, thus permitting large reductions in the cost of power handling equipment and fostering the development of dc transmission lines to reduce both energy waste and the extent of required rights-of-way, and (3) provide devices, and the systems utilizing them, with the reliability and performance required in energy generation, utilization, and conservation.

The major tasks under this project are (1) to evaluate the use of thermally stimulated current and capacitance measurements and other deep level measurement techniques as a means for characterizing lifetimecontrolling or leakage source defects in power grade silicon material and devices and (2) to develop procedures to enable spreading resistance measurements of thyristor starting material and layer profiles to be made on a reliable basis.

#### 2. DEEP LEVEL MEASUREMENTS

by

R. Y. Koyama J. Krawczyk W. E. Phillips Y. M. Liu D. R. Myers\*

2.1 Objectives

The overall objective of this task is to evaluate the use of thermally stimulated current and capacitance measurements (TSM) and other deep level measurement techniques for characterizing defects which control leakage current and lifetime in power grade silicon materials and devices. Phases 1 and 2 of this continuing task were completed in September 1976 and September 1977, respectively. Phase 3 of the task, October 1977 through September 1978, had the following objectives:

- 2.1 Complete the development of the fabrication procedures used to produce mesa diodes. These procedures are to be compatible with thyristor manufacturing procedures so that they can be used routinely to analyze and control manufacturing processes using deep level measurement (DLM) techniques.

- 2.2 Establish routine procedures for utilizing TSM (dynathermal and isothermal) and analyzing TSM data with emphasis on investigation of the metrological aspects of the measurement method associated with midgap defect centers which control the carrier lifetime. Defects such as gold or platinum (common lifetime killers) or other purposely introduced defects will be used as study vehicles in establishing these procedures.

- 2.3 Develop capabilities to measure electrical parameters of devices (fabricated test structures such as p-n junctions and MOS capacitors, and commercial devices such as rectifiers and thyristors) so that the parameters can be related to the presence of defects.

This report discusses the progress that has been made in each of these objective areas during the period October 1977 through September 1978.

#### 2.2 Background

Deep level defect measurements such as TSM [2-1] and deep level transient spectroscopy (DLTS) [2-2] utilize the ability of active defects in depletion regions to trap carriers and to emit them after receiving

<sup>\*</sup>NBS-NRC Postdoctoral Research Associate.

sufficient thermal energy. Suitable analysis of the measured data allows determination of the density, energy level, and emission rate of the defect. The interest in measurement of deep levels in semiconductors, particularly in application to power devices, stems from two related aspects: 1) detection, identification, and control of unwanted intrinsic or process-induced impurities or defects; and 2) characterization and control of defects specifically introduced for lifetime control. These techniques, which have generally been confined to laboratory studies of packaged devices, have now been extended to measurements on devices in wafer form [2-3], and routine procedures for measurement and analysis of data have been established so that these techniques can be utilized as diagnostic tools in the fabrication area as well as in the research laboratory.

The approach in this program has been twofold. Apparatus has been developed to permit deep level measurements on both packaged devices (TO-5) and full-sized wafers. Although the developed measurement techniques are fully applicable to either device format, each offers distinctive advantages. The packaged device format permits much higher precision in thermometry; this in turn allows more precision in the measurement of emission parameters and energy levels. Although such measurements can also be done on the full-wafer apparatus, this equipment is more suited for mapping of such parameters as deep level defect density and a variety of electrical device parameters. In addition, where it is used as a diagnostic tool in the manufacturing of power devices, the wafer probing apparatus offers the advantage of allowing deep level measurements to be made on processed wafers without waiting for the time-consuming packaging step.

2.3 Accomplishments This Year

### 2.3.1 Test Structure Development (Objective 2.1)

The objective of these studies is to develop a procedure which can be used to fabricate diode test structures on diffused power device wafers for the purpose of diagnostic measurements by deep level detection techniques. Preliminary investigations which established the general procedures and outlined a variety of techniques were reported previously [2-4, pp. 31-38]. A primary consideration in the development of these procedures is to minimize or eliminate the use of high temperature treatments on the test wafer in order to avoid alteration of the wafer characteristics. In order to compare and evaluate various process procedures, mask set NBS-13 was designed and implemented.

The basic test structure to be fabricated is a mesa diode utilizing one of the two  $p^+n$  junctions of a basic thyristor wafer which has undergone the first diffusion step (see fig. 2-1). Due to the deep diffusions of typical high power thyristor structures, the mesa diode test structures may require removal of as much as 80 to 100  $\mu$ m of material in order to isolate the junction. Junction isolation is followed by the application of a junction passivation and protection layer; metal contacts are then applied to complete the procedure.

Figure 2-1. The basic mesa diode processing steps: a) starting wafer; b) mesa protection, junction isolation; c) passivation, contact cut, and metallization.

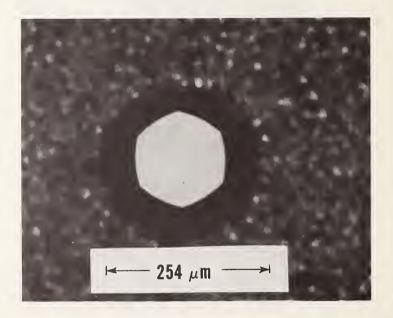

During this contract period, most of the effort on this task was devoted to evaluating mesa etching procedures and junction passivation techniques. In terms of routine fabrication and repeatability, these two steps are considered the most important. The mesa etching procedure must be controllable in order to assure proper etching depths for the diode structures. Mesa etching techniques which were evaluated included ultrasonic machining, chemical etching, and plasma etching. The plasma etching technique was found to be the most reproducible procedure and provided mesas of high quality. The passivation of the junction following the mesa etch is an important step to assure devices of low leakage characteristics which are required for the deep level measurements. This was successfully accomplished with the use of chemical-vapordeposited silicon dioxide.

The following two sections give, respectively, the detailed procedure for fabricating mesa diodes on diffused thyristor wafers and the results of an evaluation measurement mode on a mesa diode using the developed procedures. Some additional details describing the mesa etching procedure (ultrasonic and plasma methods), the mesa passivation procedure, and contact metallization are given in Appendix A.

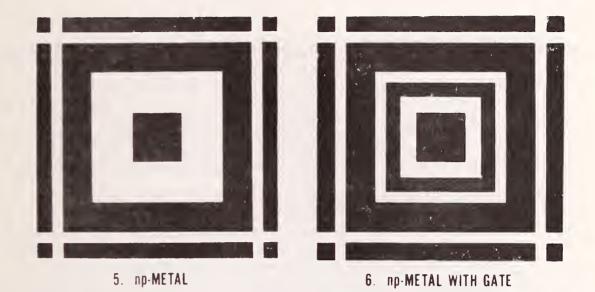

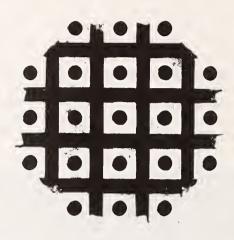

The use of test pattern NBS-13 [2-4, pp. 34-36] was extremely successful in providing information to allow judicious choices among the alternative processing techniques that were available. In addition, it revealed the advantages and limitations of both the processes and the test structures that were used in the fabrication procedures. One of the major limitations of the plasma etching procedure revealed by processing with test pattern NBS-13 was the high rate of lateral etch (undercutting). For the small structures on test pattern NBS-13, this resulted in poorly defined mesa areas. In order to compensate for this lateral etching, a different test pattern, designated NBS-20, was designed. Test pattern NBS-20 consists of square mesa diodes of dimensions 2.54 by 2.54 mm, spaced in a square array at 5.08-mm intervals. The contact and metallization masks are designed with wide tolerances to allow for lateral etching and ease of mask alignment. Figure 2-2 shows photographs of the eight levels of a single diode in test pattern NBS-20. As in the case of test pattern NBS-13, additional mask levels were included in this set to allow for process variations or alternative contact schemes. Each level is identified in the figure.

A Mesa Diode Fabrication Procedure - This section details a procedure which has been used to fabricate mesa diodes with electrical and physical properties which are suitable for deep level measurements. The starting wafer is assumed to have undergone the first high temperature diffusion step to yield a  $p^+n^-p^+$  wafer structure.

#### 1. Wafer Preparation

The diffused wafers are first chem-mechanically polished on one side. The amount of material to be removed depends on the depth of the  $p^+$ -diffusion. It is necessary that the diffused material not be removed completely; generally only enough mate-

7

np-CONTACT

8 IN METAL

test pattern NBS-20. The mesa (level 1) is 2.54 by 2.54 mm and the overall die

rial to achieve a reasonable polish is removed. The principle reason for this operation is to avoid liftoff of the aluminum masking material during plasma etching. The polished surface also aids in the alignment procedures during masking operations.

#### 2. Wafer Cleanup

The wafers are first etched in a 1:1:2 solution of ammonium hydroxide, hydrogen peroxide, and water  $(NH_4OH:H_2O_2:H_2O)$  for 20 min at 50°C; then they are rinsed in deionized water for 10 min at 23°C (hereafter called "rinsed"). Next, they are etched in a 1:1:2 solution of hydrochloric acid, hydrogen peroxide, and water  $(HC1:H_2O_2:H_2O)$  for 20 min at 50°C, then rinsed. Finally, they are etched in a 1-percent hydrofluoric acid (HF) solution for 30 s at 23°C, rinsed, and blown dry with nitrogen.

#### 3. Plasma Etching Procedure

Aluminum is evaporated onto the polished surface of the wafers to a thickness of 1000 nm by an electron-gun evaporator. The mesa areas are then defined on the aluminum layer by photolithography (level 1, NBS-20). Following the spin-on application of 1.5 to 1.0 µm of positive photoresist (KTI-II\* with a viscosity of 25 centistokes is found to be satisfactory), the wafers are baked for 20 min at 75°C. The resist is then typically exposed for 20 s and developed for 30 s, and then rinsed. This is followed by a 20-min bake at 120°C. The aluminum metal is then etched in a 20:5:1 solution of phosphoric acid, water, and nitric acid (H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O:HNO<sub>3</sub>) (hereafter called "aluminum etch") for about 8 min at 23°C and then rinsed. Finally, the resist is stripped with acetone, and then the wafers are rinsed. The wafers are placed in the plasma etching system and processed for the time required to obtain the desired etch depth; this time is chosen from a previously established calibration of etch depth vs. time. Following plasma etching, the aluminum "caps" protecting the mesa regions are removed in warm (35 to 40°C) aluminum etch and the cleanup procedure given in step 2 above is repeated.

#### 4. Passivation-Protection Layer

The wafers are etched for 30 s in an ice-bath cooled solution of CP-6 (nitric acid, hydrofluoric acid, and acetic acid, HNO3:HF:CH3COOH, 5:3:4) and then rinsed and blown dry with nitrogen. The wafers are then placed in a chemical vapor deposition reaction system. The chemical-vapor-deposited silicon dioxide (CVD-SiO<sub>2</sub>) is formed by the pyrolytic decomposition

<sup>\*</sup>KTI Chemicals, Inc., Sunnyvale, CA 94086.

of 4-percent silane  $(SiH_4)$  in nitrogen  $(N_2)$  flowing at 0.28 standard liters per minute (sLpm), oxygen  $(O_2)$  flowing at 0.025 sLpm, and nitrogen  $(N_2)$  flowing at 20 sLpm. The wafers are preheated and held at 400°C during deposition. The deposition rate is approximately 40 nm/min; final thicknesses in the range from 600 to 800 nm were used.

5. *n*-Contact Metallization

Using photolithographic techniques, the CVD-SiO<sub>2</sub> is etched to expose the appropriate n -regions of the wafer (level 2, NBS-20). Buffered-HF at room temperature is the etchant, and typical thicknesses of CVD-SiO<sub>2</sub> require 20 to 25 min of etching time to reach the silicon. The wafers are then rinsed, dried, and immediately placed in the evaporator bell jar. About 200 nm of gold (doped with 0.6% Sb) is filament-evaporated onto the front surface. The gold layer is then microalloyed at 400°C for 20 min in nitrogen to form the contact. Following this, the gold layer is photolithographically defined (level 3, NBS-20) for the n-contacts.

6.  $p^+$ -Contact Metallization

Contact cuts through the CVD-SiO<sub>2</sub> layer on top of the mesas are photolithographically defined with level 4 of NBS-20. Aluminum metal is e-gun evaporated over the front surface and then photolithographically defined with level 5 of NBS-20.

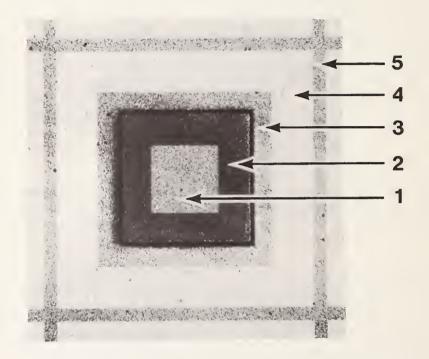

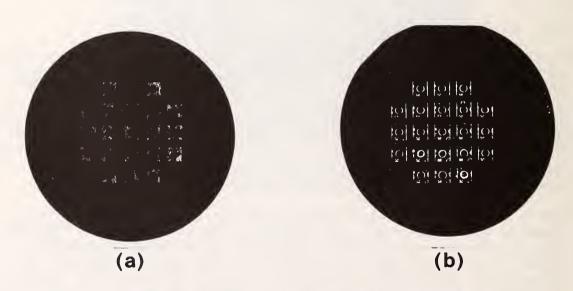

Figure 2-3 shows a photomicrograph of a mesa diode fabricated with levels 1, 2, 3, 4, and 5 of test pattern NBS-20. The following areas are identified: 1) aluminum on  $p^+$ -silicon; 2) CVD oxide on  $p^+$ -silicon; 3) CVD oxide on  $n^-$ -silicon; 4) aluminum on gold (0.6% Sb) on  $n^-$ -silicon (see discussion in Appendix A-3 regarding the possible formation of gold-aluminum intermetallic compounds); and 5) cell boundaries, CVD oxide on  $n^-$ -silicon.

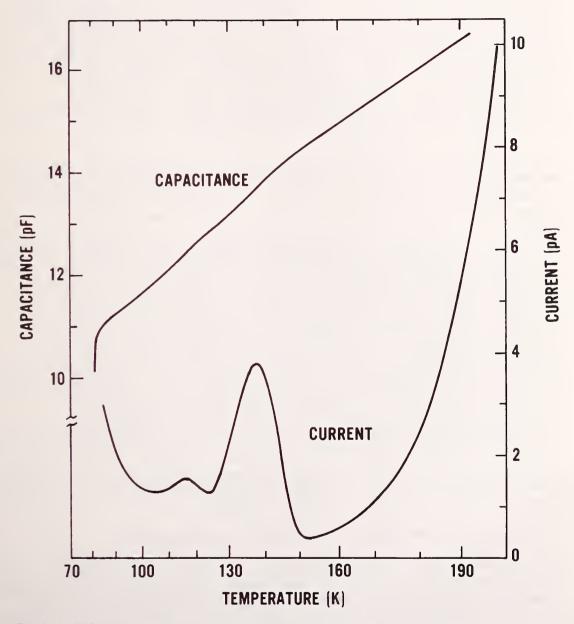

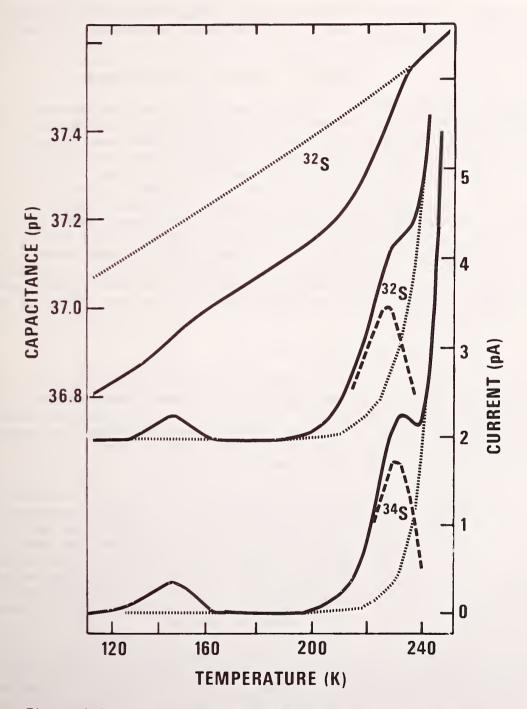

The procedure detailed above has been successfully used to fabricate mesa diode structures with reverse leakage significantly less than 1  $\mu$ A with applied bias exceeding 30 V. These would be suitable for deep level measurements. As an example, figure 2-4 displays thermally stimulated capacitance and current curves for a mesa diode fabricated on a thyristor wafer whose  $p^+$ -diffusions were 90  $\mu$ m deep from each surface. The measurements were made on the wafer probing apparatus with a heating rate of about 5 K/s. There are two distinctly resolved emissions near 115 and 135 K; the low temperature tail on both curves implies the existence of at least a third level. These levels are all electron emitters in the upper half of the silicon band gap in the lightly doped  $n^-$ region of the  $p^+n^-p^+$  wafer. Although detailed measurements to determine the energy, origin, and identity of these levels have not been made, these results demonstrate the validity of the procedures used to fabricate the mesa diodes.

Figure 2-3. Photomicrograph of a mesa diode fabricated with test pattern NBS-20. The following areas are identified: 1) aluminum on  $p^+$ -silicon, 2) CVD oxide on  $p^+$ -silicon, 3) CVD oxide on  $n^-$ -silicon, 4) aluminum on gold (0.6% Sb) on  $n^-$ -silicon, and 5) cell boundaries, CVD oxide on  $n^-$ -silicon.

Figure 2-4. Thermally stimulated capacitance and current curves measured on a mesa diode fabricated on a  $p^+n^-p^+$ -wafer using test pattern NBS-20; the heating rate is about 5 K/s.

### 2.3.2 Deep Level Measurement Methods (Objective 2.2)

Detailed derivations and descriptions of several deep level measurement procedures were reported in the previous Annual Report [2-4, pp. 38-49], namely, 1) thermally stimulated current and capacitance measurements (TSM) which provide a quick identification of well-known defects and a measure of their density; 2) isothermal transient capacitance (ITCAP) measurements which provide a precise measurement of the combined electron and hole emission rates from the defect center over a range of temperatures and from which the energy level(s) can be determined; 3) isothermal initial and final capacitance measurements which provide a ratio of the minority-to-majority-emission rates; and 4) isothermal capacitance-leakage current measurements which provide a different combination of majority and minority emission rates, namely, the ratio of their product to their sum.

Investigation of the metrological aspects of these measurement methods and their utilization has continued with emphasis on their application to midgap defect centers which affect the operation of power devices by controlling carrier lifetime or contributing to leakage currents. Thermometry procedures were developed which improve the temperature measurement precision tenfold. This improved precision was utilized, together with an ion implantation technique developed last year [2-4, pp. 50-51], to study the sulfur midgap defect centers. Sulfur was chosen because it is a prototypical deep level having both a midgap and a shallow level and, like gold or platinum, can control the carrier lifetime. These techniques permitted the discovery of an isotope shift of sulfur in silicon. The existence of the isotope shift has significant implications for the theory of semiconductor deep levels. The four measurement procedures mentioned above were utilized to separate the majority and minority carrier emission rates for the midgap sulfur level in silicon for both <sup>32</sup>S and <sup>34</sup>S. The TSM and ITCAP procedures were also utilized for the characterization of the shallow sulfur level. Golddoped gated silicon diodes were fabricated for use in an interlaboratory comparative study of deep-level measurement precision. A DLTS system was set up and performed as expected in measurements on gold and sulfur defect centers in silicon. These various accomplishments are described in greater detail in the following sections.

2.3.2.1 Improved Thermometry for Deep Level Measurements

The identification and characterization of impurities and defect centers in semiconductors by deep level measurement techniques such as thermally stimulated current and capacitance measurements (TSM) [2-1,2-5,2-6], deep level transient spectroscopy (DLTS) [2-2], or isothermal transient capacitance measurements (ITCAP) [2-4, pp. 40-46; 2-6] are primarily limited in their precision by thermometry. Temperature measurement procedures were developed which use carefully calibrated forward-biased temperature-sensing diodes and have a two-sigma precision (+0.02 K) that is an order of magnitude better than commercially available digital readout thermocouple systems (+0.2 K). This significant improvement in thermometry procedures permits improved precision in the characterization of defect centers. This precision makes these deep level measurement techniques even more useful for the quick identification of defect centers necessary in an industrial environment, as well as for the more precise laboratory characterization and study of semiconductor materials.

Measurement Procedure — Two improvements were introduced to obtain the better precision of the temperature determination. First, the temperature-sensing element is placed in good thermal contact with the device under test. This is done by mounting both the temperaturesensing element and the device under test on a ceramic chip mounted on a 10-pin TO-5 header [2-1]. The ceramic is gold plated on the top and the bottom, with an isolation gap in the gold on the top forming separate areas for the temperature-sensing element and the device under test. The mounting may be by a gold eutectic or metal-impregnated epoxy. (However, it was observed that epoxy-mounted devices sometimes have extraneous TSM responses.) The TO-5 header is hermetically sealed, is coated with thermal compound, and is tightly clamped into a recess in the copper heat sink.

The second improvement is to use a forward-biased diode as the temperature-sensing device. The temperature-sensing diodes are commercially obtainable silicon diodes [2-7]. The basic parameter measured in this procedure is the voltage drop (approximately 0.35 to 1.0 V) across the diode with constant forward current. A commercial constant current generator is carefully adjusted to supply 10.000  $\mu$ A by measuring the voltage drop across a low-temperature-coefficient resistor ( $\sim 100 \ k\Omega$ ) of known value, and the current is then switched to the temperature-sensing diode. The voltage drop is measured with a high impedance (>10<sup>10</sup>  $\Omega$ ) 5 1/2-digit voltmeter with an analog output which drives the temperature axis of an X-Y recorder for the TSM. Stability of the constant current source is very important. This system has better than 0.02-percent stability after warmup. Because of fabrication nonuniformities, each temperature-sensing diode is unique and must be individually calibrated.

Calibration — The temperature-sensing diodes are mounted in TO-5 headers as discussed above and then calibrated individually in a temperatureregulated cryostat. The TO-5 header is in good thermal contact with a high-conductivity copper heat sink in which are embedded dual Type K [2-8] thermocouples. One thermocouple is connected to a commercial temperature regulator which controls the power input to a 150-W heater which is also embedded in the copper heat sink. The other thermocouple is connected to a commercial temperature indicator which electronically compensates for the reference potential, linearizes the thermocouple output, and digitally displays the temperature with tenth-degree resolution.

The heat sink containing the TO-5 header with the temperature-sensing diode is surrounded by an evacuated stainless steel jacket. The system

is cooled by liquid nitrogen flowing through an adjustable needle valve onto the heat sink [2-1].

The system is allowed to reach temperature equilibrium at each of 15 to 25 temperatures in the temperature range to be calibrated. The digital thermocouple reading and the temperature-sensing diode voltage are recorded at each temperature. A straight line is least squares fitted to the calibration data over the range of interest. During a given ITCAP measurement, the equation of the line is used to calculate temperature from the recorded diode voltage. The temperature drift of the system, as observed on the temperature-sensing diode voltage which drifts less than 10  $\mu$ V, is less than 5 mK over several (5 to 15) min. The stability of the temperature regulation system, the precision (+10  $\mu$ V) with which the relatively large temperature-sensing diode forward voltage drop (0.5 V) can be read, and the linearity of the diode over the appropriate temperature range (Pearson's linear correlation coefficient is 0.9999996 between 205.54 and 233.08 K) make it possible to exploit statistics to achieve a precision of +0.02 K which is a tenfold improvement in precision over the thermocouple precision of +0.2 K.

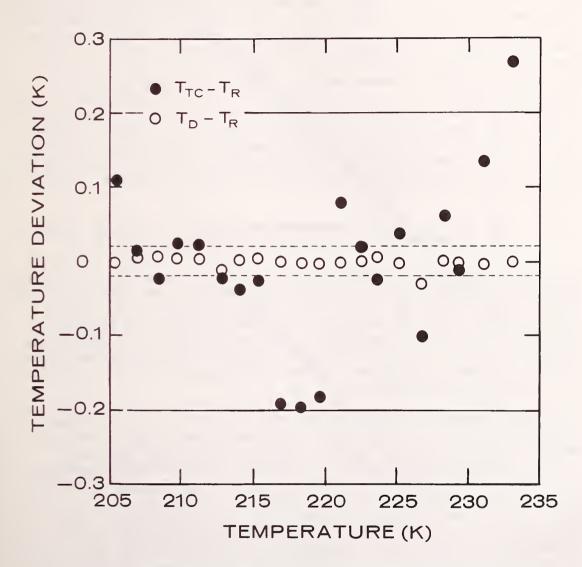

An example of this improvement is illustrated in figure 2-5 for a typical temperature-sensing diode. The closed circles show the imprecision of the thermocouple temperatures ( $\Delta T = T_{TC} - T_R$ ) and the open circles show the imprecision of the temperature obtained from the temperature-sensing diode ( $\Delta T = T_D - T_R$ ) as plotted against a reference temperature, TR, derived from the characterization values of a sulfur-implanted diode. That is, the Arrhenius emission rate equation (see eq (2) of ref. [2-1]) was solved iteratively for T from experimental values of T with  $B_x = 3.77 \times 10^6$  and  $\Delta E_x = 512$  meV [2-9], and the resulting values were least squares fitted to a straight line against the temperature diode voltages. The dashed horizontal lines are the two standard deviation limits on  $T_D - T_R$  and correspond to a change of +56  $\mu$ V in diode voltage. The expected 5 percent of the data points (one point) lies outside these limits. The solid horizontal lines are the two standard deviation limits on T<sub>TC</sub> - T<sub>R</sub> and correspond to a change of +7  $\mu$ V in thermocouple voltage. One point again lies outside these limits. The thermocouple voltage is seen to be much more subject to noise than is the temperature-sensing diode voltage, and the temperature-sensing diode has a much greater sensitivity (2784  $\mu$ V/K) than the thermocouple  $(34 \mu V/K)$ .

<u>Applications</u> — This improvement in thermometry has permitted a more precise measurement [2-10] of the midgap energy level of sulfur in silicon. In that measurement, the emission rate variation was three decades with a one-standard-deviation precision (+2 meV) which is even better than that of Rosier and Sah [2-11] (+4.5 meV) where measurements were made over seven decades of emission rate variation. The improved thermometry not only improved the precision of the characterization but also simplified the measurement, because a three-decade variation in emission rate can be obtained with much simpler procedures and instrumentation than a seven-decade variation.

Figure 2-5. Temperature deviation of the thermocouple temperature,  $T_{TC}$ , and the temperature-sensing diode temperature,  $T_D$ , compared with a reference temperature,  $T_R$ , derived from the calculated sulfur emission rate parameters in silicon. The horizontal lines are two standard deviation limits. The solid lines and solid circles correspond to the thermocouple measurements, and the dashed line and open circles are for the diode measurements.

### 2.3.2.2 Use of Deep Level Measurement Techniques to Measure the Isotope Shift of Sulfur in Silicon

The characterization of the energy levels of ion-implantationpredeposited <sup>32</sup>S in silicon by TSM were previously reported [2-4. pp. 40-47; 2-10]. The midgap level is 526 + 2 meV below the conduction band. This result is in good agreement with previous studies of the energy levels of sulfur diffused into silicon [2-11] with a midgap level of 528 + 4.5 meV below the conduction band. Natural sulfur is 95 percent  $32\overline{s}$  [2-12]. The present study was undertaken in order to evaluate the deep energy level of  $34\overline{s}$  in silicon and demonstrate the precision of the measurement methods. The energy level of the  $^{34}$ s defect was found to be 512 + 2 meV below the conduction band edge. The existence of this isotope shift of 14 + 4 meV in the sulfur deep level implies that these levels are strongly coupled to the lattice vibrations. Details of these results have been published [2-9]; the publication is included with this report as Appendix B. These results represent the first time that an isotope shift has been observed in a deep impurity level in silicon.

2.3.2.3 Use of Deep Level Measurement Techniques to Separate the Midgap Sulfur Majority and Minority Carrier Emission Rates

In order to evaluate the semiconductor deep level measurement techniques which were developed for the separation of majority and minority carrier emission rates [2-4, pp. 46-49], the techniques were applied to the midgap defect center of ion-implanted sulfur isotopes  $3^2$ S and  $3^4$ S in silicon. The objectives were to evaluate the ability of the procedures 1) to measure very low minority carrier emission rates and 2) to resolve the small differences between the energy levels of the isotopes. Both objectives were achieved.

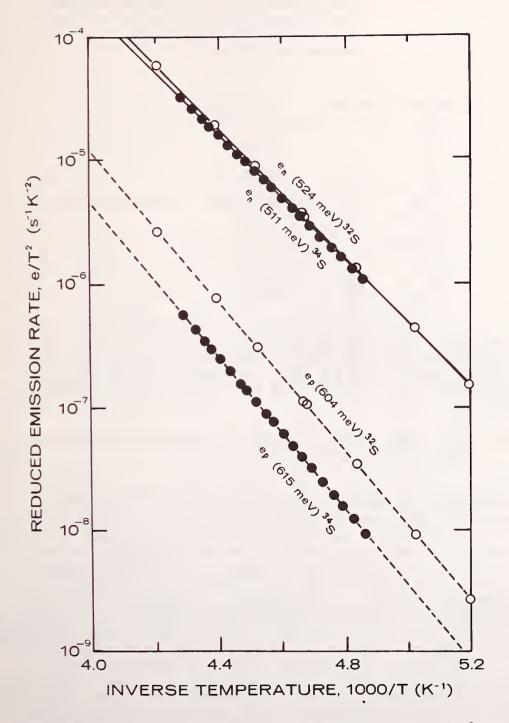

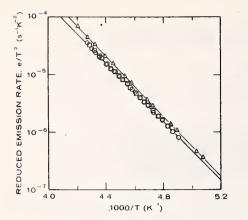

Isothermal transient capacitance measurements were made at various temperatures. These measurements give the sum of the electron and hole emission rates  $(e_n + e_p)$ . At the same time, the values for the initial and final capacitances were measured for each of the temperatures. These measurements give the ratio of hole-to-electron emission rates  $(e_p/e_n)$ . The sum  $(e_n + e_p)$  divided by  $1 + (e_p/e_n)$ gives  $e_n$ , and the sum minus  $e_n$  gives  $e_p$  at each temperature. Arrhenius plots of the logarithm of  $e_n/T^2$  and  $e_p/T^2$  against inverse temperature for each of the isotopes 32S and 34S are shown in figure 2-6. The open circles are 32S data points and the solid circles are 34S data points. The solid lines are a least squares fit to the electron emission rate data and the dashed lines, to the hole emission rate data. The activation energies are calculated as above from the slopes of the lines and the emission coefficients are calculated from the intercepts. The results are tabulated in table 2-1.

Table 2-1. Activation Energies  $(\Delta E_x)$  and Emission Coefficients  $(B_x)$  for Combined and Separated Electron and Hole Emission Rates from <sup>32</sup>S and <sup>34</sup>S Midgap Defect Centers in Silicon.

| Isotope         | Emission     | $\Delta E_{x}$ (meV) | $B_{x}$ (s <sup>-1</sup> K <sup>-2</sup> ) |

|-----------------|--------------|----------------------|--------------------------------------------|

| <sup>32</sup> s | e + e<br>n p | 526 <u>+</u> 2       | $(9.3 \pm 0.5) \times 10^6$                |

| <sup>32</sup> s | e<br>n       | 524 <u>+</u> 2       | $(7.5 \pm 0.8) \times 10^6$                |

| <sup>32</sup> s | e<br>p       | 604 + 3              | $(1.8 \pm 0.4) \times 10^{\prime}$         |

| <sup>34</sup> s | e + e<br>n p | 512 + 2.6            | $(3.8 \pm 0.6) \times 10^{6}$              |

| 34<br>S         | e            | 511 <u>+</u> 2       | $(3.5 \pm 0.6) \times 10^6$                |

| <sup>34</sup> s | e<br>p       | 615 <u>+</u> 4       | $(1.1 \pm 0.2) \times 10^7$                |

The sum of the activation energies from the defect level to the valence band  $\Delta E_p$  and to the conduction band  $\Delta E_n$  is 1128 + 4 meV for  $^{32}S$ . For  $^{34}S$ , the sum is 1126 + 5 meV. The sums are in satisfactory agreement with each other and with the known value of the band gap energy.

#### 2.3.2.4 Use of Deep Level Measurement Techniques to Characterize the Shallow Sulfur Level in Silicon

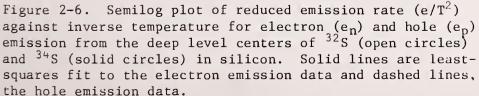

Isothermal transient capacitance methods [2-4, pp. 40-46] were utilized to characterize the shallow sulfur level in both  $^{32}$ S and  $^{34}$ S implanted  $p^+n$ -junctions fabricated on 5 to 10  $\Omega$ ·cm <111> n-type silicon as described in Appendix B. The devices were the same as used to characterize the midgap centers. The results of the evaluation of  $\Delta E_n$  and  $B_n$  in the emission rate equation,  $e_n = B_n T^2 \exp(-E_n/kT)$ , are tabulated in table 2-2 for two representative  $^{32}$ S implanted devices and one  $^{34}$ S device. Hole emission is negligible for this shallow level. The indicated uncertainties represent one standard deviation in the least squares fit of a straight line to the experimental data. The larger uncertainties in the  $^{34}$ S characterization as compared to  $^{32}$ S are due to a smaller density of  $^{34}$ S defect centers despite the use of a larger diode (device 19.6). These results are graphically displayed in figure 2-7. Despite the larger uncertainties in the  $^{34}$ S characterization, it is concluded that there is no evidence of an isotope shift of the shallow sulfur level in silicon.

Figure 2-7. Activation energy  $(\Delta E_n)$  and emission coefficient  $(B_n)$  with standard deviations for the shallow level of  $^{32}S$  and  $^{34}S$  in silicon.

Table 2-2. Activation Energies  $(\Delta E_n)$  and Emission Coefficients  $(B_n)$  for Electron Emission from the  ${}^{32}S$  and  ${}^{34}S$  Shallow Level in Silicon.

| Isotope         | Device | $\Delta E (meV)$   | $B_{n} (s^{-1}T^{-2})$ |

|-----------------|--------|--------------------|------------------------|

| <sup>32</sup> s | 9.1    | 235.0 + 1.6        | 11300 <u>+</u> 16%     |

| <sup>32</sup> s | 9.2    | 235.1 <u>+</u> 1.7 | 10700 <u>+</u> 17%     |

| <sup>34</sup> s | 19.6   | 235.0 + 3.6        | 8600 <u>+</u> 36.7%    |

### 2.3.2.5 Use of Deep Level Measurement Techniques to Study the Variation of the Relative Density of Shallow and Deep Sulfur Defect Centers with Implantation Fluence

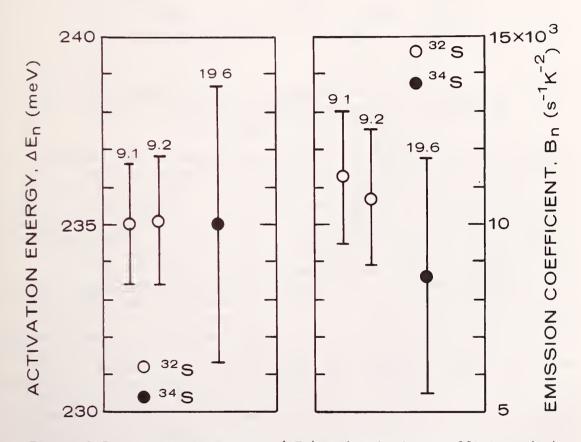

In order to study the effects of implantation density upon sulfurimplanted devices,  $^{32}$ S was implanted in  $p^+n$ -junctions to a dose of  $1 \times 10^{13}$  cm<sup>-2</sup> (compared to the previous dose of  $2 \times 10^{14}$  cm<sup>-2</sup>). The resultant defect densities were determined from the magnitude of the dynathermal capacitance transients. It was found that the defect density associated with the shallow level is not always the same as that of the deep level. For the case of  $^{32}$ S implanted to a dose of 2 x  $10^{14}$  $cm^{-2}$ , both centers were equally populated at 1.5 x 10<sup>13</sup> cm<sup>-3</sup>. This result is similar to that observed in previously published studies of sulfur diffused into silicon [2-11]. However, for the case of  $^{32}S$ implanted to a dose of  $1 \times 10^{13}$  cm<sup>-2</sup>, the transients for the shallow and deep centers were no longer of the same magnitude as illustrated in figure 2-8. The deeper sulfur defect appears at almost the same density as for the higher fluence implantation; however, the density of the shallow level is reduced by a factor of approximately seven. Implantation of  $^{34}$ S to a dose of 1 x 10<sup>13</sup> cm<sup>-2</sup> also led to unequal transients for the shallow and deep centers. The density differences observed in the more lightly implanted devices bring into question another aspect of the theoretical treatments of the sulfur center. Pseudopotential theories of the sulfur centers based on the effective mass theory [2-13] predict that substitutional sulfur would have two energy levels within the silicon bandgap, while models of the same center based on the Slater self-consistent field method [2-14] suggest that one of the sulfur energy levels would be resonant with the silicon valence band. The fact that equal densities had been seen for the shallow and deep defect levels had been taken as implying that both these levels arose from the same center, thereby supporting the pseudopotential treatment. However, the present results suggest that the density of the center responsible for the shallow level increases with increasing sulfur implant dose,

Figure 2-8. Dynathermal capacitance and current responses of a silicon  $p^+n$ -junction diode implanted with  $^{32}$ S to a dose of 1 x 10<sup>13</sup> cm<sup>-2</sup> and the current response with  $^{34}$ S of the same dose. The heating rate was about 10 K/s.

while the density of the center responsible for the deeper level remains nearly constant, thus weakening the support for the pseudopotential model.

This study illustrates the power of deep level measurements to answer fundamental questions related to understanding and controlling impurities in semiconductors.

#### 2.3.2.6 Artifacts for Comparative Deep Level Measurements

A comparative study was initiated so that interested laboratories could assess their ability to measure deep level impurities accurately. In this study, a pair of gold-doped silicon gated diodes was made available for measurement of defect energy levels and associated densities and emission rates by each interested laboratory. At the completion of this study, a listing of all the values obtained and the methods used by the participating laboratories will be made available. However, the names of the participating laboratories will not be associated with their data in this compilation. It is hoped that this type of interlaboratory comparison will raise the general level of competence in the field of deep level measurements to a point that they will become more effectively and widely used by the semiconductor industry. It is anticipated that at least three laboratories will participate in this study by the end of FY 79.

#### 2.3.2.7 Deep Level Transient Spectroscopy

The primary method used by this laboratory for the detection and characterization of deep levels have been the isothermal transient capacitance (ITCAP) technique and the thermally stimulated current and capacitance measurement (TSM) technique. These methods have been discussed in earlier reports [2-4, pp. 38-46; 2-15, pp. 74-87] and applied in the previous sections to the case of implanted sulfur.

In the ITCAP method, the device under test is held at a fixed temperature; the change in the depletion capacitance due to defect emission is recorded as a function of time after the defect is charged by the application of a momentary zero-bias pulse. In the TSM techniques, the device is cooled below the emission temperature of the defect and the defects are then charged; emission is then allowed by heating the device at some known heating rate. Effectively, both of these measurements occur at dc since the defects are charged once, and the emission response to the single charging event is directly recorded.

Another technique described in the last annual report [2-4, pp. 51-59] is an extension of the ITCAP method. Rather than recording the response to a single charging pulse as is done in ITCAP, charging pulses are applied to the device at regular intervals to allow a periodic repetition of charging and emission. This method transforms the measurement from dc to the repetition frequency of the pulses and allows alternative methods for signal processing. In this case, a minicomputer system was utilized to capture, digitize, and analyze the capacitance transient.

Another deep level measurement technique which is rapidly gaining popularity is the deep level transient spectroscopy (DLTS) method [2-2]. In principle, this method is the same as the extended ITCAP technique, but there are two basic differences in implementation. First, the capacitance measurements are made at higher frequencies (10 to 50 MHz), and, second, the technique utilizes a dual-channel box-car integrator for the signal processing. The attractive attributes of this method are the spectroscopic nature of the recorded data and the relative ease with which energy levels can be deduced. (However, as is true for all of the described methods, the accuracy of the results is dependent on the care exercised with the thermometry [see sec. 2.3.2.1].)

Because of the prevalence of the users of DLTS, an apparatus of this type was set up in this laboratory to allow direct comparison to existing methods. The apparatus is similar in nature to that described by Lang [2-16]. It basically consists of a high frequency capacitance bridge and the dual-channel box-car integrator system. To date, preliminary DLTS measurements have been made on the midgap gold acceptor, the shallow gold donor, and the midgap sulfur level; the energy levels determined agreed with previous measurements by the ITCAP method within experimental uncertainties.

### 2.3.3 Correlation of Defects with Device Parameters (Objective 2.3)

The bulk deep level defects in high power devices are already present in the starting material or are introduced either intentionally or unintentionally during wafer processing. In order to realize specific electrical characteristics of their devices, manufacturers must be able to control their processes to minimize unwanted defects and to optimize the nature and number of defects [2-17] which are used to control the lifetime of minority carriers [2-18] or switching characteristics of devices. Another aspect of the introduction of specific defects to control lifetime is the ability to fabricate wafers with controlled characteristics over the full area of the wafer. This is important, for example, in a thyristor's ability to switch without developing hot spots. In addition to lifetime, the influence of deep level defects on such electrical parameters as junction forward voltage drop and reverse leakage current must be well-characterized.

The hot/cold wafer-probing apparatus [2-19,2-20] was used to map the two-dimensional spatial variation of deep level defects across a golddiffused wafer. It was also used to map the diode reverse leakage and the forward voltage drop. Similar electrical measurements were made on commercially fabricated power rectifiers in wafer form; in addition, a direct comparison of the diode reverse recovery lifetime and the open circuit voltage decay (OCVD) lifetime was made.

2.3.3.1 Reverse Leakage Current and Forward Voltage Drop of Diodes

Reverse leakage current in pn-junctions can originate from at least three sources: 1) generation in the depletion layer, 2) diffusion of minority carriers into the depletion layer, and 3) conduction along the surface layer. In general, surface leakage is a consequence of surface contamination due to improper processing or a consequence of improper device design to minimize surface fields. At room temperature, leakage by diffusion of minority carriers into depletion regions is negligible for silicon devices. Hence, under most circumstances, the reverse leakage current is dominated by carrier generation in the depletion layer. Some qualitative estimates of the behavior of devices with such factors as lifetime, diffusion length, injection level, and forward voltage can be seen from an examination of the basic diode equations.

The generation leakage current,  $I_{GEN}$ , is proportional to the carrier generation rate per unit volume, U, and the volume of the depletion region. Thus:

$$I_{CFN} = q [U] WA , \qquad (2-1)$$

where q is the electronic charge and W and A are, respectively, the width and area of the depletion volume. The generation rate is given by [2-21]:

$$|\mathbf{v}| = \frac{N_i}{2\tau_0} \tag{2-2}$$

where

$$\tau_{0} \equiv \frac{\sigma n \varepsilon}{2^{\sigma} p^{\sigma} n^{v} th^{N} t} (E_{i} - E_{t})/kT$$

$$(2-3)$$

$N_i$  is the intrinsic carrier density,  $\sigma_n$  and  $\sigma_p$  are the electron and hole capture cross sections, respectively,  $E_i$  is the intrinsic Fermi energy,  $v_{th}$  is the thermal velocity of carriers, and  $N_t$  is the density of recombination-generation carriers at energy  $E_t$  in the gap. The generation rate is seen to be inversely proportional to  $\tau_0$ , which is the space charge generation lifetime, and directly proportional to the density of the recombination-generation centers. From the standpoint of space charge generation, devices of low reverse leakage characteristics require a long space charge generation lifetime and a small density of deep level defect centers.

Under forward bias conditions, the effect of the defect density is seen most directly at low level injection. When the injection level is very low, recombination of carriers occurs primarily in the depletion volume through the presence of the deep level defects. The forward recombination current,  $I_{I,I}$ , is then given by [2-22]:

$$I_{LL} = \frac{qN_{i}WA}{2\tau_{0}} (\varepsilon^{qV/2kT} - 1) . \qquad (2-4)$$

V is the forward voltage drop across the diode; simplifying assumptions entering this result include  $\sigma_p = \sigma_n$  and  $E_t = E_i$  in eq (2-3). It is evident from eq (2-4) that for a given low level injection current, devices with large  $\tau_0$  (i.e., low N<sub>t</sub>) also have large forward voltage drop.

Typical high power devices operate in the high injection regime. Efficient operation under these conditions requires high forward current with low forward voltage drop. At high injection, the voltage across the lightly doped *n*-region of a typical diode structure is given by [2-23]:

$$V_n \approx \frac{2kT}{q} \left(\frac{d}{L_a}\right)^2$$

, (2-5)

where d is the half-width of the *n*-region and  $L_a$  is the ambipolar diffusion length. Large values of  $L_a$  (resulting from long high level lifetime) are necessary for low forward drop in this region.

Wafer map measurements of reverse leakage current and forward voltage drop were made at room temperature on two fabricated wafers to observe the correlations indicated by eqs (2-3) and (2-4). One wafer was a gold-diffused wafer fabricated in our facilities. The tested structure was a 430-µm diameter gated diode (device number 10 of test pattern NBS-3 [2-24]) spaced at 5.08-mm intervals on the wafer. After fabrication of the  $p^+n$ -structure by diffusion of boron (3.0 µm) into <111> 5 to 10  $\Omega$  cm n-type silicon, gold was diffused into the wafer from a backsurface-evaporated layer by a 24-h, 800°C heat treatment. The other wafer was a commercially fabricated rectifier wafer consisting of an array of 2.54-mm devices spaced on a 3.43-mm grid. The devices were  $p^+nn^+$ -structures rated at 16 A.

The reverse leakage measurements were made with a digital electrometer with an applied reverse bias of 15 V. The gates on the gold-diffused devices were biased to minimize the surface leakage; the rectifiers did not have gates.

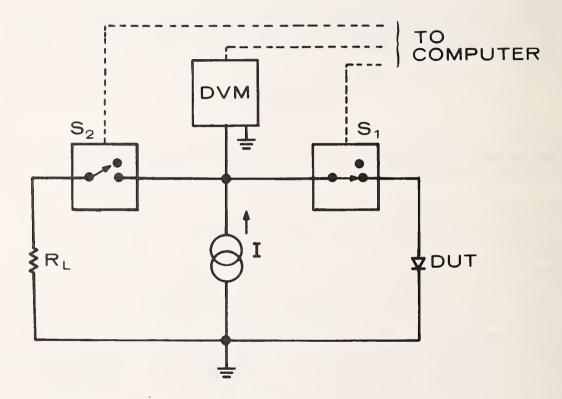

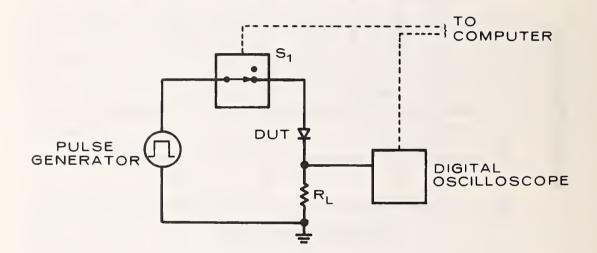

The forward voltage drop measurements (low injection) were made under computer control. A schematic is shown in figure 2-9. A digital voltmeter (DVM) measures the voltage across the diode which has a constant current I (10  $\mu$ A) through it. Switch S<sub>1</sub> is actually the probe which contacts the device. In a typical sequence, switch S<sub>2</sub> is closed to

Figure 2-9. Schematic diagram of method used to measure forward voltage drop of diodes.

ţ

divert the current through  $R_L$  (to allow a measurement of the current and to prevent compliance limiting); then  $S_1$  is opened and the prober is instructed to move to the next device. After reaching the next device, the device is probed (i.e., close  $S_1$ ), switch  $S_2$  is opened, and then the DVM is instructed to read. Measurements can be made at the rate of about one per second.

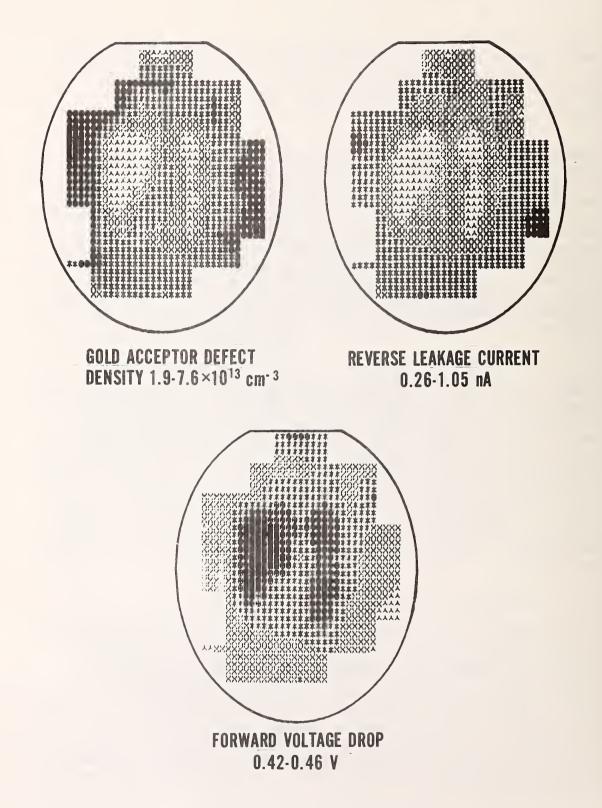

Figure 2-10 displays wafer maps of the gold acceptor defect density, the reverse leakage current (at 15 V), and the forward voltage drop (at 10  $\mu$ A) for the gold-diffused wafer. (The lighter areas represent the smaller values of the parameter.) There is a factor of four variation in the defect density and the reverse leakage current; as seen from the patterning of the maps, regions of low defect density result in low leakage current as indicated by eqs (2-2) through (2-4). The forward voltage drop map shows similar patterning but is inversely related to the reverse leakage and the defect density maps. As indicated by eq (2-4), for a given low level current, devices with long lifetime have large forward voltage; hence, regions of low defect density (i.e., long lifetime) on the wafer correspond to regions of high forward voltage drop.

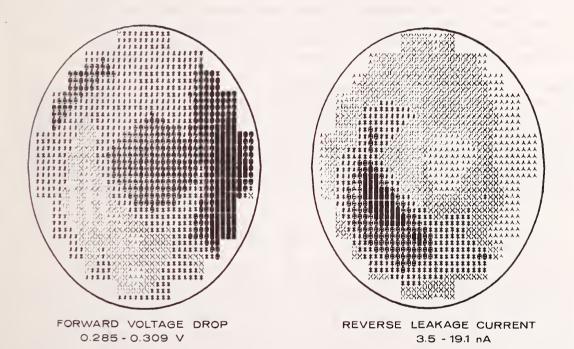

Figure 2-11 compares the forward voltage drop (at 10  $\mu$ A) and the reverse leakage current (at 15 V) of the commercial rectifier wafer. As was observed in the gold-diffused wafer, these parameters have an inverse relationship on the wafer maps. Although no guard gate is available to control surface leakage on these devices, the general correspondence of the maps would indicate that generation current in the depletion region dominates the reverse leakage. Note that there is a very wide variation in the reverse leakage current. Although the wafer map for defect density for this wafer has not yet been measured, one can infer from the results on the gold-diffused wafer discussed above that the same variation exists in the density of the midgap defect center which controls the leakage. Confirming measurements of the defect density are planned for the future.

2.3.3.2 Measurement of Minority Carrier Lifetime

It is evident even from relatively simple considerations that lifetime of minority carriers plays an important part in the performance of semiconductor devices. The presence of deep levels in the device strongly affects the minority carrier lifetime. As seen earlier, greater density of deep levels in the depletion region results in higher reverse leakage current. The design of high power thyristors generally requires short lifetime in order to improve the recovery characteristics; however, too large a density of deep levels can also result in degradation of forward conduction characteristics. Hence, the minority carrier lifetime must be tailored to meet the specific design requirements of the devices.

Figure 2-10. Wafer maps of the gold acceptor defect density, the reverse leakage current, and the forward voltage drop for the gold-diffused wa-fer. (The lighter areas represent the smaller values of the parameter.)

Figure 2-11. Wafer maps of the reverse leakage current and the forward voltage drop for the commercial rectifier wafer.

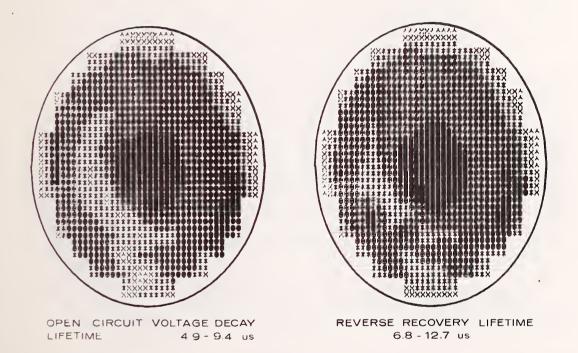

Two techniques for measuring minority carrier lifetime include the open circuit voltage decay (OCVD) and the diode reverse recovery methods. These two methods were implemented in order to correlate the lifetimes with the other measured electrical parameters and also to correlate the results of the two different lifetime measurements.

The OCVD lifetime is determined from the slope of the decaying forward voltage on a diode following the abrupt termination of the forward injection current. Consider the  $p^+nn^+$ -structure of a typical rectifier. Under conditions of high level injection in the lightly doped *n*-region, the steady-state electron and hole concentrations greatly exceed the equilibrium donor concentration, and charge neutrality causes the electron and hole concentration to be equal [2-25]. When the current is suddenly terminated, the excess carriers cause an open circuit voltage across the  $p^+n$ - and the  $nn^+$ -junctions; this excess concentration decreases in time by recombination, and hence the open circuit voltage decays with time.

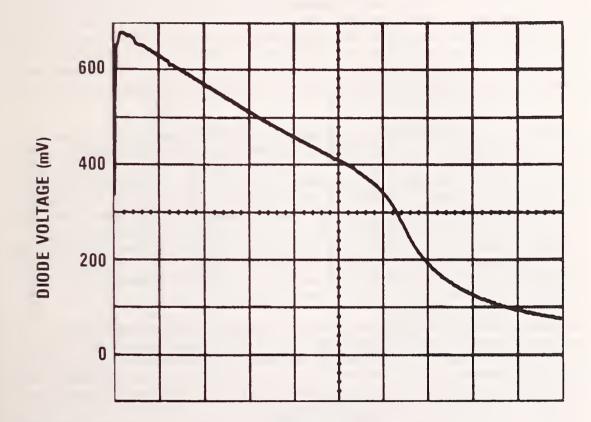

Figure 2-12 shows a typical oscilloscope trace of an OCVD response of one of the devices on the commercially fabricated rectifier wafer discussed earlier. The measurements were made with a commercially available OCVD instrument.\* This instrument provides a repetitive series of voltage pulses which result in alternating forward injection and open circuit on the diode. The effective high level lifetime is determined from the slope of the linear portion of the decaying voltage [2-26]

$$\tau_{\rm HL} = -\left(\frac{2kT}{q}\right) \left(\frac{dV}{dt}\right)^{-1}$$

(2-6)

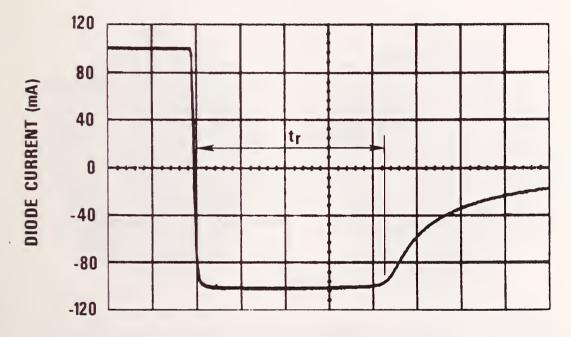

For the diode reverse recovery method, the diode is first placed in a steady-state forward bias condition as in the case of the OCVD method. But, rather than terminating the device into an open circuit as in OCVD, the voltage across the diode is abruptly reversed. At this instant, there is an abrupt reversal of current which is limited only by the external circuit; this reverse current persists as the excess carriers leave the lightly doped region (i.e., the *n*-region of a  $p^+nn^+$ -structure) by diffusion. At some time,  $t_r$ , after reversal of the voltage, depletion begins at the  $p^+n$ -junction and the device then begins to sustain a reverse voltage. At this point, the reverse current begins to decay toward the steady-state reverse leakage value. The minority carrier lifetime,  $\tau$ , is related to the recovery time  $t_r$  by the following relationship [2-27]:

erf

$$[t_r/\tau]^{1/2} = (1 + I_r/I_f)^{-1}$$

. (2-7)

<sup>\*</sup>Solid State Measurements, Inc., Monroeville, PA, Model OCD-2.

## TIME (5 $\mu$ s/DIV)

Figure 2-12. An OCVD response of a typical power rectifier diode. The high level lifetime is given by the slope of the linear portion of the high voltage region of the curve ( $\tau_{\rm HL} = 4.7 \ \mu s$ ).

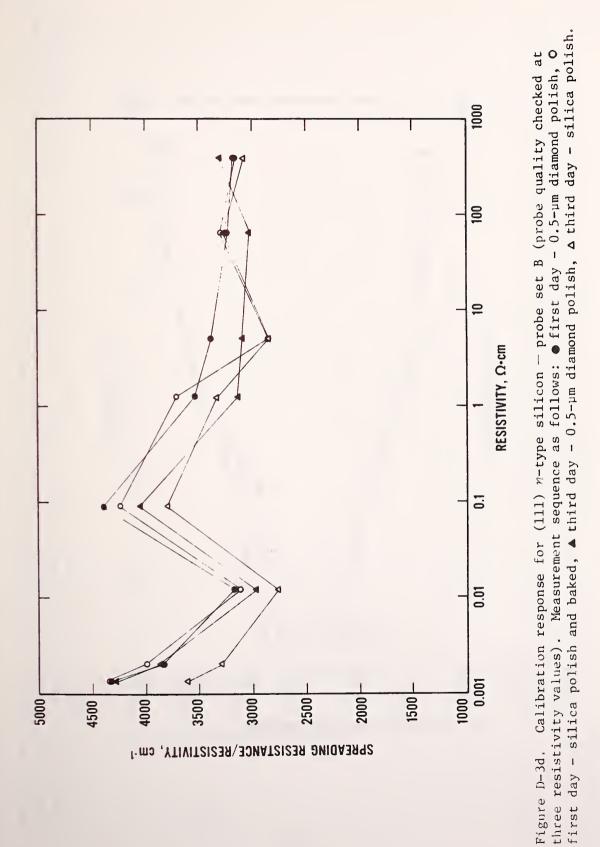

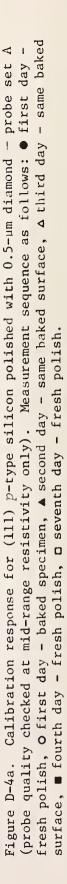

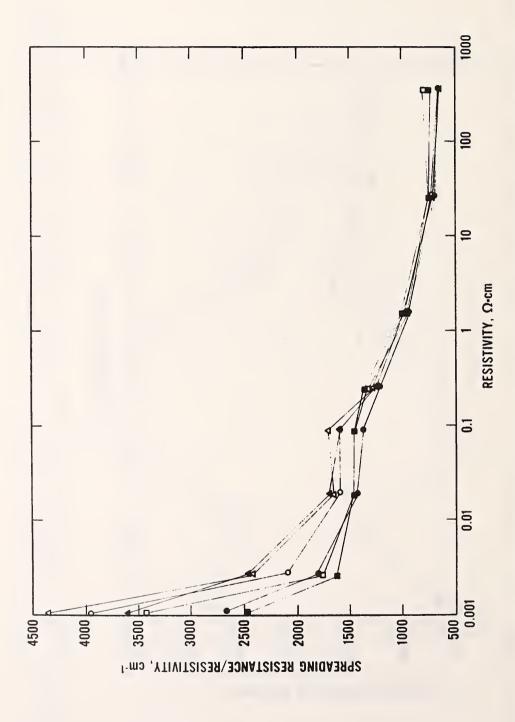

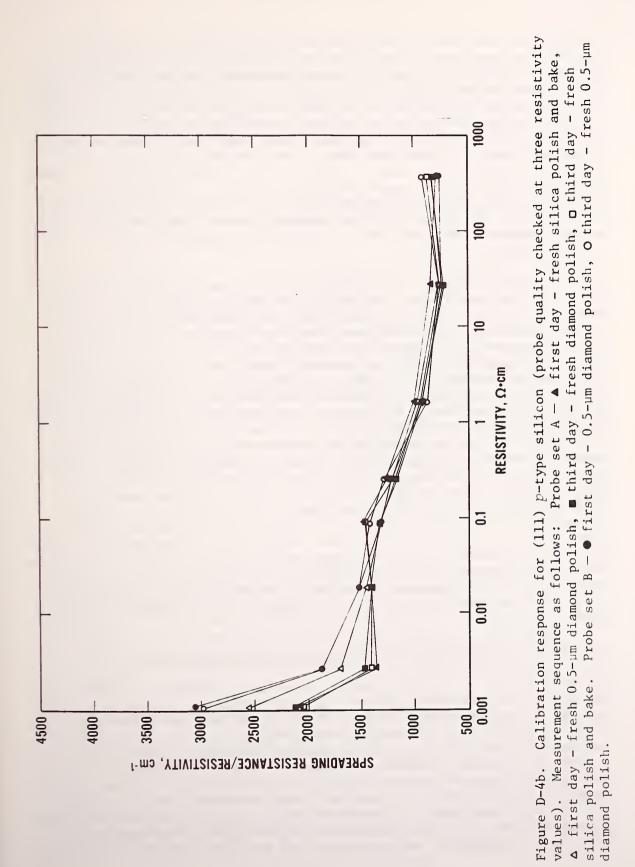

$I_r$  and  $I_f$  are the magnitudes of the reverse and forward currents; for the case when  $I_r = I_f$ ,  $\tau \approx 4 t_r$ . Figure 2-13 displays an oscilloscope trace of a diode reverse recovery characteristic with  $I_r =$  $I_f$ ; the recovery time is shown on the figure. This is a characteristic which is typical of devices on the commercial rectifier wafer discussed previously.