W. Murray Bullis, Editor

**Electron Devices Division** Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Washington, D.C. 20234

June 1979

Prepared for

00

100

U56

C.2

The Defense Advanced Research Projects Agency The National Bureau of Standards The Division of Electric Energy Systems, Department of Energy The Division of Distributed Solar Technology, Department of Energy The Defense Nuclear Agency The Charles Stark Draper Laboratory The Army Electronics Research and Development Command **\ir Force Avionics Laboratory Vaval Material Command Vaval Weapons Support Center** Solar Energy Research Institute 79-1591-3

#### SEMICONDUCTOR TECHNOLOGY PROGRAM

### TABLE OF CONTENTS

| Reverse-Bias Second Breakdown         |     | 3   |

|---------------------------------------|-----|-----|

| Integrated Gated-Diode Electrometer . | • • | 3   |

| Random Fault Measurements             |     | 4   |

| Pattern Generator Positional Accuracy |     | 4   |

| Intrachip Linewidth Variation         |     | 5   |

| Transient Upset in TTL Circuits       |     | 5   |

| Photoresist Sensitometry              |     | 6   |

| Optical Linewidth Measurements        |     | 7   |

| Spreading Resistance Profiling        |     | 7   |

| Model Spreading Resistance Data       |     | 8   |

| Silicon Resistivity SRMs              |     | 8   |

| Sheet Resistance Measurements         |     | 8   |

| New Topics                            | • • | . 9 |

| Work in Progress                      |     | 9   |

| Recent Publications                   |     | 9   |

| Publications in Press                 |     | 10  |

ABSTRACT - This report provides information on the current status of NBS work on measurement technology for semiconductor materials, process control, and devices. Results of both in-house and contract research are covered. Highlighted activities include studies of: reverse-bias second breakdown, an integrated gated-diode electrometer, random fault measurements, pattern generator positional accuracy, intrachip linewidth variation, transient upset in TTL circuits, photoresist sensitometry, optical linewidth measurements, spreading resistance profiling, model spreading resistance data, silicon resistivity SRMs, and sheet resistance measurements. In addition, brief descriptions of new and selected on-going projects are given. The report is not meant to be exhaustive; contacts for obtaining further information are listed. Compilations of recent publications and publications in press are also included.

KEY WORDS: Electronics; integrated circuits; measurement technology; microelectronics; semiconductor devices; semiconductor materials; semiconductor process control; silicon.

1

# Preface

This report covers results of work during the forty-third quarter of the NBS Semiconductor Technology Program. This Program serves to focus NBS research on improved measurement technology for the use of the semiconductor device community in specifying materials, equipment, and devices in national and international commerce, and in monitoring and controlling device fabrication and assembly. This research leads to carefully evaluated, well-documented test procedures and associated technology which, when applied by the industry, are expected to contribute to higher yields, lower cost, and higher reliability of semiconductor devices and to provide a basis for controlled improvements in fabrication processes and device performance. By providing a common basis for the purchase specifications of government agencies, improved measurement technology also leads to greater economy in government procurement. Financial support of the Program is provided by a variety of Federal agencies. The sponsor of each technical project is identified at the end of each entry in accordance with the following code: 1. The Defense Advanced Research Projects Agency; 2. The National Bureau of Standards; 3. The Division of Electric Energy Systems, Department of Energy; 4. The Division of Distributed Solar Technology, Department of Energy; 5. The Defense Nuclear Agency; 6. The C. S. Draper Laboratory; 7. The Army Electronics R&D Command; 8. The Air Force Avionics Laboratory; 9. The Naval Material Command; 10. The Naval Weapons Support Center; and 11. The Solar Energy Research Institute.

This report is provided to disseminate results rapidly to the semiconductor community. It is not meant to be complete; in particular, references to prior work either at NBS or elsewhere are omitted. The Program is a continuing one; the results and conclusions reported here are subject to modification and refinement. Further information may be obtained by referring to more formal technical publications or directly from responsible staff members, telephone: (301) 921-listed extension. General information, past issues of progress briefs, and a list of publications may be obtained from the Electron Devices Division, National Bureau of Standards, Washington, D.C. 20234, telephone: (301) 921-3786.

### **Reverse-Bias Second Breakdown**

A qualitative model of transistor turnoff switching behavior has been developed. Typically, the voltage storage time associated with turnoff is defined as the interval between the initiation of turnoff (base current reversal) and the time at which the collector voltage (usually reaches 10% of its peak clamped) value. However, there is a significant interval between the time that the device voltage begins to rise above its saturation voltage (leaves saturation and enters quasi-saturation) and the time it reaches 10% of its peak value. This is because the collector region of a typical modern power transistor is long and lightly doped. Significant power is dissipated during this interval because the voltage is rising and the current is constant at its peak Depending upon the operating value. conditions, 10 to 30% of the total energy dissipated during one turnoff cycle can be dissipated before the voltage reaches 10% of its peak value. To account for this region of high energy dissipation, another time interval must be defined. The voltage storage time then becomes the time interval from the initiation of turnoff until the time at which the device leaves saturation. The other time interval, as yet unnamed, which accounts for quasi-saturation, exfrom the time the transistor tends leaves saturation until the time at which the collector voltage reaches 10% of its peak value. Current crowding occurs only in this latter time interval. Consequently, the voltage at which second breakdown occurs is most sensitive to the magnitude of the reverse base current during this time interval and is relatively insensitive to the magnitude during the voltage storage time as newly defined above. Preliminary experiments confirm that the reverse base current

magnitude is not important as far as the second breakdown voltage is concerned until the device reaches its quasisaturation region. [Sponsor: 2] (D. L. Blackburn, x3621)

### **Integrated Gated-Diode Electrometer**

Continuing studies of the integrated gated-diode electrometer were carried out. Experimental measurements of the interactions between the designed elements of the circuit and the parasitic circuit elements are being compared with computer circuit simulations.\* Preliminary conclusions reinforce confidence both in the analytical model for the equivalent circuit for this integrated test structure and in the methods developed to measure the structure. Insights have been obtained which provide alternative methods to overcome limitations of the device. For example, it was verified experimentally that a large fixed capacitor, connected in parallel with the diode junction, dominates both the junction capacitance and parallel parasitic capacitances so that only the added fixed capacitance need be considered when calculating the leakage current. Measurements of leakage current with and without the capacitor give the same result, although the presence of the additional large capacitance substantially decreases the output voltage decay rate. Under certain circumstances, the tradeoff may be desirable if it results in a more accurate measurement by reducing the effects of parasitic capacitance.

As an extension of the utility of the integrated test structure, pulsed capacitance measurements of the charge build-

<sup>\*</sup>Design and fabrication of the test devices used in the experiments and the computer simulations were carried out by the Westinghouse Advanced Technology Laboratories, Baltimore, MD.

up in the gate inversion layer are being In these measurements, investigated. the diode gate is used as an MOS capacitor, and the diode junction and the electrometer are employed as a chargesensing amplifier. Unlike conventional capacitor transient measurements where capacitance is measured as a function of time following a voltage pulse which biases the capacitor into deep depletion, in this procedure the charge buildup in the gate inversion layer is measured as a function of time. Evaluation of the experimental results awaits completion of an analytical description of the time rate-of-increase of the inversion layer charge density, but it is anticipated that this technique will complement the gated-diode reverse-bias voltage decay measurement by providing a second method for measurement of bulk lifetime. An extension of this technique would use the integrated test structure to measure recovery time or storage time in a dynamic memory cell. In this application, the diode gate functions as the transfer electrode, and the diode junction and electrometer operate as a charge integrator, a configuration analogous to the charge-sensing output amplifier frequently used in CCDs. [Sponsors: 1,2,6] (G. P. Carver, x3541)

### **Random Fault Measurements**

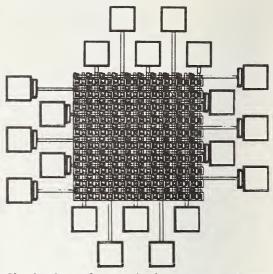

Initial test results have demonstrated that the location of a fault can be identified from electrical measurements on memory-type MOSFET array test struc-In some cases, fault type has tures. also been identified electrically from the data taken to date. Four such structures appear on test pattern NBS-16. This pattern is being used to develop process assessment methods to evaluate the electrical performance, tolerance, and radiation yield of radiation-hardened, silicon-gate CMOS/SOS LSI circuits. Each randomfault test structure consists of a 10 by 10 array of *n*- or *p*-channel MOSFETs, each with its gate connected to its level 3) and the doped regions (mask drain.

Check plot of a typical p-channel MOSFET array found on test pattern NBS-16. The probe pads around the periphery of the array are 80 µm by 80 µm.

columns and the gates and drains are connected in rows, as illustrated in the accompanying check plot of a typical pchannel MOSFET array. Each device is electrically isolated from its neighbors (except for the common row and column connections). Threshold voltage, breakdown voltage, and source-to-drain leakage current can be individually measured for each MOSFET on the array by addressing the appropriate row and column probe pads. Further analysis is continuing in order to establish improved criteria for identifying fault types from electrical data. [Sponsor: 8]

(L. W. Linholm, x3541)

#### Pattern Generator Positional Accuracy

The metal-to-doped region potentiometric electrical alignment test structures on test pattern NBS-15 were used to evaluate the positional accuracy of a typical computer-controlled pattern generator. A composite 10X reticle was made up by flashing the rectangles from the mask levels for both the metal areas (mask The sources are connected in level 1) on the same plate. This reticle was stepped and repeated to construct a 1X working photomask. Two wafers were fabricated by contact printing the pattern on an aluminum film evaporated on an oxidized silicon substrate and defining the pattern by wet chemical The misalignment was measured etching. at 266 locations on each wafer. The mean value of the measured misalignment (35 nm) is indicative of the positional accuracy of the pattern generator. This indicates that rectangles could be positioned within 350 nm on the 10X reticle, well within the stated accuracy of the pattern generator employed. Variability in the alignment may be introduced by the processing of the 10X reticle, the 1X photomask, and the wafers. The average of the sample standard deviations was 49 nm, which suggests that variability from processing exceeds the afterreduction positioning error of the pattern generator. [Sponsor: 1]

(T. J. Russell, x3541)

#### **Intrachip Linewidth Variation**

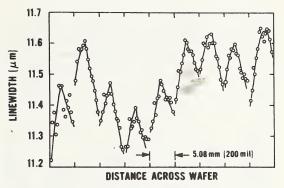

Additional measurements of periodic and random variations in linewidth over an integrated circuit wafer were made using test pattern NBS-21. This single-level pattern consists of an 8 by 15 array of identical cross-bridge sheet resistors with a drawn linewidth of 0.600 mils (15.24 μm). The array fits within a square 200 mils (5.08 mm) on a side and is repeated across the mask on 200-mil centers each way. The pattern is fabricated by delineating (with the use of contact printing and wet chemical etching techniques) the cross-bridge resistors in an 800-nm thick aluminum film evaporated on an oxidized silicon wafer. Each wafer contains 53 arrays. All the arrays on a given wafer exhibited a similar pattern of linewidth variation which was on the order of 0.2 µm for the smallest to the largest value, as illustrated by the example of data from one row in the arrays across the diameter of a wafer shown in the accompanying fig-Similar periodic variations have ure. been measured on other wafers from vari-

Linewidth variations in one row of the nine arrays across the diameter of a wafer as measured by the cross-bridge structures of test pattern NBS-21.

ous lots, all fabricated with the same photomask. These periodic variations can be attributed to the system used to fabricate the photomask. In addition, variations over the wafer were observed when the same structure in each array was measured. These variations, which are also evident in the example shown in the figure, can be attributed to the photolithography associated with the contact printing or to variations in etching the pattern or to both. The range in measured linewidth across the entire wafer was typically about 0.5 µm. [Sponsors: 1,2] L. W. Linholm, x3541)

## **Transient Upset in TTL Circuits**

During an on-going study of transient upset in digital integrated circuits, being conducted in collaboration with the Naval Research Laboratory, a temperature dependence of the upset threshold was observed in standard transistortransistor logic (TTL) circuits. Preliminarv results indicate that the threshold increases with temperature over the range from 20 to 150°C. Other workers addressing this problem have disagreed in predictions of the direction of the temperature dependence. Based on the limited amount of data currently available, it has been hypothesized that upset is due to photocurrent generated in the depletion layer of the

collector-substrate junction. The decrease in sensitivity to upset with increasing temperature in a standard golddoped TTL gate would result from the reduction in thickness of the depletion layer as the resistivity of the gold-The capacidoped material decreases. tance of the depletion layer in such a gate was measured and was found to inincreasing temperature, crease with which supports this hypothesis. Further support for the hypothesis is given by the fact that in Schottky-clamped versions of the same gate (74S series), the upset sensitivity and the junction capacitance do not depend significantly on The Schottky-clamped detemperature. vices are not gold-doped. [Sponsor: 5] (T. F. Leedy, x3621)

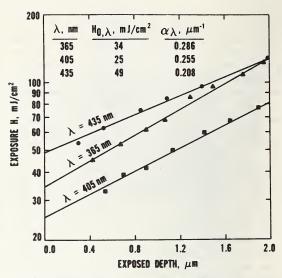

### Photoresist Sensitometry

A more rapid and precise technique than direct measurement of photoresist linewidth variations as a function of exposure has been found for measuring exposure characteristics of photoresist. The linewidth measurement technique suffered both from the inability to locate the line edges accurately and from large variability in the resulting data. The current technique is based on the property that the depth of photoresist dissolved during a controlled amount of development after exposure to a known amount of monochromatic radiation corresponds to a specific fraction of photolysis. The depth of the exposed pattern is measured with a surface profilometer; plots of log exposure against developed depth of a positive resist exposed to radiation of wavelength 365, 405, or 436 nm (the three strong lines of high pressure, short arc mercury lamps typically used in microelectronic patterning) show a linear relationship. Examples of these plots are given in the accompanying figure. The linear behavior is predicted from theoretical modeling of resist exposure performed and reported The development of this previously. technique represents an initial step in the complete characterization of resist

Semilog plot of photoresist exposure, H, as a function of exposed depth, d, for a positive resist exposed to monochromatic radiation of wavelength  $\lambda$ . The data follow the relationship

$\log H = \log H_{0,\lambda} + \alpha_{\lambda} d$ .

The quantity H is proportional to time of exposure to a constant flux of radiation.

exposure. Each relation of monochromatic exposure against depth constitutes an element in the additive effect of these exposures when a resist is simultaneously exposed to the complete radiation spectrum of the mercury lamp. One unexpected result was obtained: the 405-nm radiation appears to be more effective than the 365-nm radiation despite the greater absorbance of the resist at 365 In general, it had been assumed nm. that radiation of the wavelength for which the resist exhibits the greatest absorbance has the greatest effect on the resist exposure. The 436-nm radiation, which is least sensitive, also has the lowest absorbance, and so follows the expected trend. Also, an aging effect, a decrease in resist sensitivity with time, was observed; this behavior suggests that this method of resist exposure characterization may provide a tool for assessing resist shelf life and aging effects. [Sponsor: 1]

(D. B. Novotny, x3621)

1

### **Optical Linewidth Measurements**

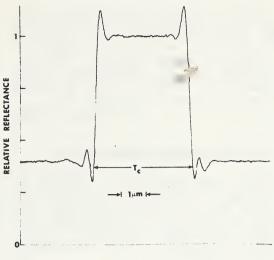

The prototype system for optical linewidth measurements on wafers in reflected light was completed. Linewidths down to 0.5 µm can be measured with a sensitivity of 0.01 µm. For measurements of features with steep edges in thin layers, the capability of the reflected light system is comparable to that of the scanning photometric microscope developed earlier for measurements on photomasks in transmitted light. However, the two systems differ significantly. Both systems operate with Kohler illumination and modified bright field illumination (the illuminating numerical aperture must be one-fourth or less of that of the imaging objective for low contrast materials), but the reflected light system uses a 0.5-W krypton laser source and a more sensitive photomultiplier-detector system. In addition, the alignment requirements for the optics of the reflected light system, which illuminate a much smaller field of view, are more stringent than those for the optics of the transmitted light system. All of these conditions result from the need for illumination with very narrow spectral bandwidth which is dictated by the strong wavelength dependence of both the reflectance and optical phase difference associated with thin films. The reflectedlight system produces image profiles like that shown in the accompanying figure.\* From such an image profile, the linewidth is determined using the coherent optical threshold T<sub>c</sub> with appropriate corrections for the reflectances of the materials and the optical path difference which occurs at the edge on reflection. At the present time, both and transmitted the reflected light light systems are limited to films less than 400 nm thick. For thicker layers the edge detection equations are no longer valid and determination of best focus is ambiguous. Research is under-

#### DISTANCE

Line image profile of a  $3.9-\mu m$  line etched in a 150-nm thick layer of silicon dioxide on a silicon wafer.

way to develop accurate edge detection and focusing procedures for thick layers. [Sponsors: 1,2]

(D. Nyyssonen, x3621)

#### **Spreading Resistance Profiling**

A continuum formulation of spreading resistance correction factors was obtained by deriving a differential equation for the kernel of the correction factor integral in the limit as the layer thickness approaches zero. This differential equation is nonlinear and inhomogeneous, but, because it is of the Riccati type, it can be transformed into a linear, second-order equation which can be solved analytically in several cases. The continuum form of the correction factor was compared with the correction factor generated from the multilayer version of the Laplace equation description of spreading resistance for the case of a specimen with exponentially varying resistivity. The difference between the results obtained from the two forms depends on the exponential constant, the total thickness of the structure, and (most importantly) the number of layers used in the discrete form.

<sup>\*</sup>To obtain this feature, the NBS linewidth calibration pattern (NBS 77) was contact printed from an anti-reflection chromium photomask and plasma etched. The wafer pattern contains lines as narrow as 0.55 µm. (Y. M. Liu, x3541)

Typically, for the case of ll layers, the discrete form yields a factor about one-third that yielded by the continuum form, but for the case of 201 layers the difference is only about 6%. These differences represent a fundamental limitation to the accuracy of the multilayer correction factor. [Sponsor: 1]

(J. H. Albers, x3625)

### **Model Spreading Resistance Data**

Studies were made of model spreading resistance data\* for deep diffusions (up to 90  $\mu$ m). For diffusions deeper than about 5  $\mu$ m, the simple relationship between spreading resistance,  $R_{sp}(x)$ , and incremental sheet resistance,  $R_{s}(x)$ :

$R_{sp}(x) = \frac{1}{\pi} R_s(x) \ln \frac{s}{a},$

where s is the probe spacing and a is the effective contact radius, is no longer valid. It is found that, for all diffused layers investigated, the spreading resistance is approximately linear in ln s with a slope which is approximately proportional to the sheet resistance. This result would indicate that, for diffusions, probe spacing experiments could be safely interpreted in terms of a sheet resistance, even though the interpretation of the intercept as being related to the probe radius holds only for uniform layers and shallow diffusions. [Sponsor: 1]

(J. H. Albers, x3625)

## Silicon Resistivity SRMs

Twenty sets of SRM 1522, Silicon Power Device Level Resistivity Standard, have been fabricated and individually measured and certified. This new standard reference material is comprised of three 51-mm diameter slices of neutron transmutation doped (n-type) silicon with nominal resistivities (at room temperature) of 25, 75, and 180  $\Omega$ ·cm. Each slice is nominally 25 mils (0.64 mm) thick. A two-operator two-instrument experiment was performed on five specimens from each crystal to estimate the precision of the certification measurements. Results of the experiment give estimates of the 95% confidence interval about the certified values as follows:  $\pm 0.2$ ,  $\pm 0.4$ , and  $\pm 0.6\%$  for the 25-, 75-, and  $180-\Omega \cdot cm$  specimens, respectively. [Sponsor: 2] (J. R. Ehrstein, x3625)

### **Sheet Resistance Measurements**

Results of an interlaboratory experiment on the measurement of the sheet resistance of thin silicon layers by the four-probe method were analyzed. The experiment was coordinated by NBS for ASTM Committee F-1 on Electronics. Tt was conducted to evaluate the precision to be expected when ASTM Test Method F 374, Sheet Resistance of Silicon Layers, is used for the measurement of lavers less than 3 µm thick. The procedure requires the use of a probe assembly with four blunt probe tips, terminating either in a hemisphere with a radius between 100 and 250 um or in a circular truncation of a cone with a circle diameter between 100 and 250 µm. A probe force between 0.30 and 0.80 N (31 and 82 gf) is required for either configuration of probe tips. Six types of implanted layers and two types of epitaxial layers were used as test specimens in the ex-Layer thicknesses were beperiment. tween 0.2 and 1.5 µm, and layer sheet resistance values were between 200 and 6000  $\Omega/\Box$ . The analysis, which accounted for laboratory-to-laboratory differences, run-to-run differences within a given laboratory, and differences in the six measurements on each specimen in any run, indicated that overall precision generally degraded with increasing The precispecimen sheet resistance. sion can be expressed in terms of the reproducibility interval for the average of six measurements on a specimen, the reproducibility interval being the 95% confidence interval for the difference in averages of specimen sheet resistance

1

<sup>\*</sup>An annotated computer program to calculate model spreading resistance data is available on request. The program is written in double-precision UNIVAC FORTRAN V.

measured by two different laboratories. A conservative estimate for this reproducibility interval, which covers all specimens tested, is ±10% of the average sheet resistance value. [Sponsor: 2]

(J. R. Ehrstein, x3625, and J. Orban\*)

New Topics . . .

Applications of Neutron Transmutation Doped Silicon - A survey is being undertaken to determine the technical impediments to more effective utilization of NTD silicon for thyristor pro-During this period, discusduction. sions with several industrial users of NTD silicon were completed to determine present areas of concern in NTD usage and to assess the potential for application of NTD silicon in other high power In addition, groups involved devices. in silicon materials research were also contacted. Additional information from individuals and organizations interested in this topic is welcomed. [Sponsor: 31 (D. R. Myers, x3625)

Gallium Arsenide Characterization -Evaluation of improved practical methods for characterizing device quality gallium arsenide substrates and epitaxial layers was initiated. Initial activity is directed toward extension to gallium arsenide of measurement techniques for silicon characterization. These include capacitance-voltage profiling, resistivity and Hall measurements on van der Pauw specimens, deep level transient spectroscopy (DLTS), and spreading resistance measurements. In addition. photo-DLTS and optical absorption mea- \*Weglein, R. D., and Wilson, R. G., An surements are being explored for applicability to characterization of semiinsulating gallium arsenide. [Sponsor: 71 (A. C. Seabaugh and R. Y. Koyama, x3625)

### Work in Progress . . .

An improved pattern for linewidth calibration artifacts has been designed. \*NBS-NRC Postdoctoral Research Associate, NBS Statistical Engineering Division.

The improvements are based on results from the 10-laboratory evaluation of procedures for optical measurement of linewidths in the 0.5- to 10-1m range on chromium photomasks with transmitted light. Additional elements are included in the artifact to enable the user to check for lead-screw errors in filar and image-shearing microscope evepieces. Several minor design changes were made to reduce confusion in locating and identifying each measurement element and to facilitate distinguishing the multiple lines in line-spacing measurements with image-shearing eyepieces. Procurement of anti-reflective chromium and iron-oxide artifacts with the improved initiated. pattern was Sponsors: 1.2] (J. M. Jerke, x3621)

Wafer maps of the forward voltage of power rectifiers at low injection levels were previously found to be correlated with the reverse leakage current; regions of high forward drop corresponded to regions of low reverse leakage cur-However, at values of forward rent. current exceeding the high injection threshold, the correlation with reverse leakage is found to disappear abruptly. This transition is related to the dependence of the forward drop on the carrier lifetime. At low injection, the minority carrier lifetime dominates, whereas at high injection the forward drop depends on the high level lifetime. [Sponsor: 3] (R. Y. Koyama, x3625)

### **Recent Publications** . . .

- Acoustic Gray Scale for Scanning Acoustic Microscopy and Diagnostic Ultrasound, Ultrasound Imaging 1, 89-100 (January 1979).

- Sawyer, D. E., Kessler, H. K., and Schafft, H. A., Solar Cell Measurement Technique Development and Other Services. Proc. Photovoltaic Advanced Materials Review Meeting, October 24-26, 1978, SERI/TP-49-105, CONF. 781017, pp. 41-50 (January 1979).

\*Reports of Contract Research.

- Gilsinn, D., and Kraft, R., Semiconductor Measurement Technology: DISTRIB I, An Impurity Redistribution Computer Program, NBS Spec. Publ. 400-57 (February 1979).

- Russell, T. J., Maxwell, D. A., Reimann, C. T., and Buehler, M. G., A Microelectronic Test Pattern for Measuring Uniformity of an Integrated Circuit Fabrication Technology, *Solid State Tech*nology 22 (2) 71-74 (February 1979).

- \*Weglein, R. D., A Model for Predicting Acoustic Material Signatures, Appl. Phys. Letters <u>34</u>, 179-181 (1 February 1979).

- Berning, D. W., Semiconductor Measurement Technology: A Reverse-Bias Safe Operating Area Transistor Tester, NBS Spec. Publ. 400-54 (March 1979).

- \*Goldsmith, N., and Mayer, A., High-Speed Spreading Resistance Probe, NBS-GCR-79-166 (March 1979).

- Mayo, S., and Evans, W. M., Development of Hydrogen and Hydroxyl Contamination in Thin Silicon Dioxide Thermal Films, NBSIR 78-1558 (March 1979).

- Russell, T. J., and Maxwell, D. A., Semiconductor Measurement Technology: A Production-Compatible Microelectronic Test Pattern for Evaluating Photomask Misalignment, NBS Spec. Publ. 400-51 (April 1979).

# Publications in Press . . .

- Buehler, M. G., Microelectronic Test Patterns with Test Structures Designed Within a 2 by N Pad Array, *Proc. Microelectronics Measurement Technology* Seminar, San Jose, CA, February 6-7, 1979.

- Carver, G. P., and Buehler, M. G., The Development of Test Structures for Characterization of the Fabrication and Performance of Radiation-Hardened CCD Imagers, NBSIR 79-1744.

- Dickey, D. H., and Ehrstein, J. R., Semiconductor Measurement Technology: Spreading Resistance Analysis for Silicon Layers with Nonuniform Resistivity, NBS Spec. Publ. 400-48.

- Ehrstein, J. R., Two-Probe (Spreading \*Reports of Contract Research.

Resistance) Measurements for Evaluation of Semiconductor Materials and Devices, Nondestructive Evaluation of Semiconductor Materials and Devices, NATO Advanced Study Institute, Frascati, Italy, September 18-30, 1978.

- Galloway, K. F., Mayo, S., and Roitman, P., Radiation Levels Associated with Advanced Lithographic Techniques, J. Electrochem. Soc.

- Galloway, K. F., and Mayo, S., Radiation Levels Associated with the Electron Beam Metallization Process, Solid State Technology.

- \*Ham, W. E., Semiconductor Measurement Technology: A Comprehensive Test Pattern for SOS Technology, NBS Spec. Publ. 400-56.

- Harman, G. G., Nondestructive Tests Used to Insure the Integrity of Semiconductor Devices with Emphasis on Passive Acoustic Techniques, Nondestructive Evaluation of Semiconductor Materials and Devices, NATO Advanced Study Institute, Frascati, Italy, September 18-30, 1978.

- \*Helms, C. R., The Morphology and Electronic Structure of Si-SiO<sub>2</sub> Interfaces and Si Surfaces, J. Vac. Soc. Tech.

- Test Pattern for Evaluating Photomask \*Kasden, H. L., Linewidth Measurements by Misalignment, NBS Spec. Publ. 400-51 Diffraction Pattern Analysis, NBS-GCR-(April 1979). 78-142.

- Koyama, R. Y., and Buehler, M. G., Novel Variable-Temperature Chuck for Use in the Detection of Deep Levels in Processed Semiconductor Wafers, *Rev. Sci. Instrum.*

- Leedy, T. F., LSI Digital Testing An Annotated Bibliography, NBS Tech. Note 1102.

- \*Li, S. S., Semiconductor Measurement Technology: The Theoretical and Experimental Study of the Temperature and Dopant Density Dependence of the Hole Mobility, Effective Mass, and Resistivity in Boron-Doped Silicon, NBS Spec. Publ. 400-47.

- Myers, D. R., Koyama, R.Y., and Phillips, W. E., An Implantation Predeposition Technique for Deep Level Characterization, *Radiat*. *Eff*.

- Myers, D. R., Roitman, P., and Mayo, S., Electrical Characterization of Low-Dose (Continued on Back Cover)

1

| NBS-114A (REV. 9-78)                                                                               |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------|----------------------------------------------|--|--|

| U.S. DEPT. OF COMM.                                                                                | 1. PUBLICATION OR REPORT NO.                                                                                                                                                                                            | 2. Gov't: Accession No.                                         | 3. Recipient's Ac                 | cession No.                                  |  |  |

| BIBLIOGRAPHIC DATA<br>SHEET                                                                        | NBSIR 79-1591-3                                                                                                                                                                                                         |                                                                 |                                   | 100                                          |  |  |

| 4. TITLE AND SUBTITLE                                                                              |                                                                                                                                                                                                                         |                                                                 | 5. Publication Da                 | te                                           |  |  |

| Semiconductor Technology Program — Progress Briefs                                                 |                                                                                                                                                                                                                         | June 1979                                                       | 44.TM                             |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         | 4. Performing Organization Code                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 | A D ( ) A                         |                                              |  |  |

| 7. AUTHOR(S)<br>W. Murray Bullis,                                                                  | Editor                                                                                                                                                                                                                  | •                                                               | 8. Performing Org                 | an. Report No.                               |  |  |

| 9. PERFORMING ORGANIZATIO                                                                          | IN NAME AND ADDRESS                                                                                                                                                                                                     |                                                                 | 10. Preject/Task/                 | Work Unit No.                                |  |  |

| NATIONAL BUREAU OF STANDARDS                                                                       |                                                                                                                                                                                                                         |                                                                 | 11. Contract/Grant No.            |                                              |  |  |

| DEPARTMENT OF COMM                                                                                 | ERCE                                                                                                                                                                                                                    |                                                                 |                                   |                                              |  |  |

| WASHINGTON, DC 20234                                                                               |                                                                                                                                                                                                                         |                                                                 | See item 15.                      |                                              |  |  |

| NBS, Washington, DC 20<br>20305; Dept. of Energy<br>Cambridge, MA 02139;<br>R&D Command, Ft. Monmo | DN NAME AND COMPLETE ADDRESS (Stre<br>0234; ARPA, Arlington, VA 22209;<br>, Washington, DC 20545; C. S. Dra<br>AFAL, Wright-Patterson AFB, OH 45<br>uth, NJ 07703; NavMat Command, Hd<br>47522; SERI, Golden, CO 80401. | DNA, Washington, DC<br>per Laboratory,<br>433; Army Electronics | Interim                           | t & Period Covered<br>far. 1979<br>ency Code |  |  |

| Agreement EX-77-A01-60<br>(Navy contract N 00030                                                   | ARPA Order 2397, Program Code 9Y10<br>10, T. O. A021-EES and T. O. A054-<br>-78-C-0100); AFAL, MIPR FY117578N2<br>P. O. NOOU37781P89010; NWSC, P. O                                                                     | SE; C. S. Draper Labor<br>062; Army Electronics,                | atory, P. O. DL<br>R&D Coumand, P | -H-162208 '<br>. 0. 78-                      |  |  |

| 16. ABSTRACT (A 200-word or                                                                        | less factual aummary of most significant inf                                                                                                                                                                            | ormation. If document includ                                    | les a significant bil             | liography or                                 |  |  |

| literature survey, mention it i                                                                    | nere.)                                                                                                                                                                                                                  |                                                                 |                                   |                                              |  |  |

| This report provi                                                                                  | des information on the cur                                                                                                                                                                                              | rent status of NB                                               | S work on me                      | easurement                                   |  |  |

|                                                                                                    | miconductor materials, pro                                                                                                                                                                                              |                                                                 |                                   |                                              |  |  |

| both in-house and                                                                                  | contract research are cov                                                                                                                                                                                               | ered. Highlighte                                                | d activities                      | include                                      |  |  |

| studies of: reverse-bias second breakdown, an integrated gated-diode electrome-                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

| ter, random fault measurements, pattern generator positional accuracy, intrachip                   |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

| linewidth variation, transient upset in TTL circuits, photoresist sensitometry,                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

| optical linewidth measurements, spreading resistance profiling, model spreading                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    | silicon resistivity SRMs,                                                                                                                                                                                               |                                                                 |                                   |                                              |  |  |

|                                                                                                    | escriptions of new and sel                                                                                                                                                                                              |                                                                 |                                   |                                              |  |  |

|                                                                                                    | nt to be exhaustive; conta                                                                                                                                                                                              |                                                                 |                                   |                                              |  |  |

| are listed. Compilations of recent publications and publications in press are                      |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

| also included.                                                                                     |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

|                                                                                                    |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

| separated by semicolons)                                                                           | ntries; alphabetical order; capitalize only ti                                                                                                                                                                          |                                                                 |                                   |                                              |  |  |

|                                                                                                    | grated circuits; measureme                                                                                                                                                                                              |                                                                 |                                   |                                              |  |  |

| conductor devices                                                                                  | ; semiconductor materials;                                                                                                                                                                                              | semiconductor pr                                                | ocess contro                      | ol; sili-                                    |  |  |

| con.                                                                                               |                                                                                                                                                                                                                         |                                                                 |                                   |                                              |  |  |

| 18. AVAILABILITY                                                                                   | 🗶 Unlimited                                                                                                                                                                                                             | 19. SECURIT<br>(THIS RE                                         |                                   | 21. NO. OF<br>PRINTED PAGES                  |  |  |

| For Official Distribution                                                                          | . Do Not Release to NTIS                                                                                                                                                                                                | UNCLAS                                                          | IFIED                             | 12                                           |  |  |

| Order From Sup. of Doc.,<br>20402, SD Stock No. SNO                                                | U.S. Government Printing Office, Washingt<br>103-003-                                                                                                                                                                   | on, DC 20. SECURIT<br>(THIS PA                                  |                                   | 22. Price<br>\$4.00                          |  |  |

| Corder From National Tec<br>VA, 22161                                                              | chnical Information Service (NTIS), Springfie                                                                                                                                                                           | Id, UNCLAS                                                      | SIFIED                            | 94°00                                        |  |  |

USCOMM-DC

(Continued from Page 10)

Ion Implanted Silicon Annealed with Microsecond Laser Pulses, Proc. MRS Symp. on Laser-Solid Interactions and Laser Processing, Boston, MA, November 28- \*Schwarz, S. A., and Helms, C. R., A Sta-1978 (AIP Symposium December 1, Series).

ment Effects on Implantation Profiles in Silicon, Radiat. Eff.

Nyyssonen, D., Optical Linewidth Measurement - A Basic Understanding, Proc. Microelectronic Measurement Technology Seminar, San Jose, CA, February 6-7, 1979.

Rubin, S., and Oettinger, F. F., Semiconductor Measurement Technology: Thermal Resistance Measurements on Power Transistors, NBS Spec. Publ. 400-14.

Schafft, H. A., Semiconductor Measurement Technology: Reliability Technology for Cardiac Pacemakers III - A Workshop Report, NBS Spec. Publ. 400-50.

Schafft, H. A., Performance Criteria for "Wilson, R. G., and Weglein, R. D., Photovoltaic Power Conditioning, Control, and Storage, Proc. DoE Photovoltaic Technology Development and Applications Program Review, Arlington, VA, \*Reports of Contract Research.

November 7-9, 1978.

Schafft, H. A., Standards for Photovoltaic Energy Conversion Systems, NBSIR 79-1743.

tistical Model of Sputtering, J. Appl. Phys.

Myers, D. R., and Wilson, R. G., Align- \*Schwarz, S. A., and Helms, C. R., An Ion Knock-On Mixing Model with Application to Si-SiO<sub>2</sub> Interface Studies, J. Vac. Sci. Tech.

> \*Sulouff, R. E., Investigation of Moisture Measurement, Failure Rate, and Leak Rate and Study of Moisture Infusion, NBS-GCR-78-144.

> "Wilson, R. G., and Comas, J., Correlation of Atomic Distribution and Implantation Induced Damage in Be Ion-Implanted Silicon, Radiat. Eff.

> "Wilson, R. G., and Comas, J., Channeling and Random Equivalent Depth Distributions of 150-keV  $\frac{3}{2}$ Li,  $\frac{2}{2}$ Be, and  $\frac{1}{5}$ B Implanted into <100> and <110> Silicon. Radiat. Eff.

> Acoustic Material Signatures Using the Reflection Acoustic Microscope, Proc. 1st Internat. Symp. Ultrasonics Matls. Characterization, Washington, DC, June 8-10, 1978.

U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary Jordan J. Baruch, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director