Mattonal Burcau of Standards

- the sect

QC100

11

12144

APR 17 1979

Allol 726536

NBSIR 78-1444-2

# Semiconductor Technology Program Progress Briefs

W. Murray Bullis, Editor

Electron Devices Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Washington, D.C. 20234

**July 1978**

#### Prepared for

00

56

8-1444-2

The Defense Advanced Research Projects Agency The National Bureau of Standards The Division of Electric Energy Systems, Department of Energy The Division of Solar Technology, Department of Energy Defense Nuclear Agency Charles Stark Draper Laboratory Irmy Electronics Research and Development Command Air Force Avionics Laboratory ABSTRACT - This report provides information on the current status of NBS work in measurement technology for semiconductor materials, process control, and devices. Results of both in-house and contract research are covered. Highlighted activities include: profiling of the Si-SiO2 interface by Auger electron and x-ray photoelectron spectroscopies; use of the laser scanner to detect hairline cracks in solar cells; use of gated diodes in evaluation of CCD imager wafers; availability of silicon resistivity standard reference materials; observation of unintentional channeling effects in low-fluence random equivalent ion implantations; initiation of a comparative study of deep level measurements; implementation of the NBSdesigned circuit for determining safeoperating-area limits of forward-biased transistors; observation of acoustic material availability of test pattern signatures; NBS-4; conduct of a workshop on moisture measurements; and comparison of carrier lifetimes as measured by the surface photovoltage and photoconductive decay methods. In addition, brief descriptions of new and selected on-going projects are given. The report is not meant to be exhaustive; contacts for obtaining further information are listed. Compilations of recent publications and publications in press are also included.

#### SEMICONDUCTOR TECHNOLOGY PROGRAM

#### TABLE OF CONTENTS

| Profiling the Si-SiO <sub>2</sub> Interface |   | • | . 3 |

|---------------------------------------------|---|---|-----|

| Detection of Cracks in Solar Cells .        | • | • | . 3 |

| Gated Diodes and CCD Dark Current           | • | • | . 4 |

| Silicon Resistivity SRMs                    | • | • | . 4 |

| Unintentional Ion Channeling Effects        | • | • | . 5 |

| Deep Level Measurements                     | • | • | . 5 |

| Transferability of SOA Test Circuit .       | • | * | . 5 |

| Acoustic Material Signatures                | • | • | . 6 |

| Availability of Test Pattern NBS-4 .        | • | • | . 6 |

| Moisture Measurement Workshop               | • | • | . 7 |

| SPV-FCD Lifetime Comparison                 | • | • | . 7 |

| New Projects                                | • | • | . 7 |

| Work in Progress                            | • | • | . 8 |

| Recent Publications                         | • | • | . 9 |

| Publications in Press                       |   |   | 10  |

KEY WORDS - Electronics; integrated circuits; measurement technology; microelectronics; semiconductor devices; semiconductor materials; semiconductor process control; silicon.

#### Preface

This report covers results of work during the thirty-ninth quarter of the NBS Semiconductor Technology Program. This Program serves to focus NBS research on improved measurement. technology for the use of the semiconductor device community in specifying materials, equipment, and devices in national and international commerce and in monitoring and controlling device fabrication and assembly. This research leads to carefully evaluated, well-documented test procedures and associated technology which, when applied by the industry, are expected to contribute to higher yields, lower cost, and higher reliability of semiconductor devices and to provide a basis for controlled improvements in fabrication processes and device performance. By providing a common basis for the purchase specifications of government agencies, improved measurement technology also leads to greater economy in government procurement. Financial support of the Program is provided by a variety of Federal agencies. The sponsor of each technical project is identified at the end of each entry in accordance with the following code: 1. The Defense Advanced Research Projects Agency; 2. The National Bureau of Standards; 3. The Division of Electric Energy Systems, Department of Energy; 4. The Division of Solar Technology, Department of Energy; 5. The Defense Nuclear Agency; 6. The C. S. Draper Laboratory; 7. The Army Electronics R&D Command; and 8. The Air Force Avionics Laboratory.

This report is provided to disseminate results rapidly to the semiconductor community. It is not meant to be complete; in particular, references to prior work either at NBS or elsewhere are omitted. The Program is a continuing one; the results and conclusions reported here are subject to modification and refinement. Further information may be obtained by referring to more formal technical publications or directly from responsible staff members, telephone: (301) 921-listed extension. General information and a list of past publications may be obtained from the Electron Devices Division, National Bureau of Standards, Washington, D.C. 20234, telephone: (301) 921-3786.

Semiconductor Technology Program

**Progress Briefs**

3

## Profiling the Si-SiO<sub>2</sub> Interface

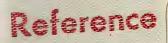

Contract efforts are currently underway to develop and refine the application of X-ray Photoelectron Spectroscopy (XPS) and Auger Electron Spectroscopy (AES) for the examination and control of electron device structures. Papers describing the application of these measurement tools to determine the chemical structure of the interface between silicon and thermally grown silicon dioxide were recently presented at the International Topical Conference on the Physics of SiO<sub>2</sub> and Its Interfaces (Yorktown Heights, NY, 22-24 March 1978).

In the XPS work (performed at JPL), depth profiling was accomplished using a newly developed wet-chemical etching technique which minimizes the perturbation of the remaining oxide due to oxide-solvent reaction. The data from this work indicate that the stoichiometry of  $SiO_2$  as determined by XPS is essentially uniform except for a transitional zone within  $\sim 0.5$  nm of the interface. The data also give evidence for intermediate oxidation states near the interface.

In the AES work (performed at Stanford University), depth profiling was accomplished using a 1-keV argon beam to remove material by sputtering. The data are deconvolved to account for ion beam knock-on and electron escape depth effects in order to improve the depth resolution. The results indicate that there is a transition region between essentially pure

Model of the Si-SiO<sub>2</sub> interface as derived from sputter Auger studies.

SiO<sub>2</sub> and essentially pure Si no greater than 0.8 nm wide which undulates with a period of less than 100  $\mu$ m and a peak-topeak amplitude of about 2 nm. This picture of the interface, illustrated in the accompanying figure, is consistent both with the one emerging from the XPS work and with the results of published transmission electron microscope studies. [Sponsor: 1] (K. F. Galloway,\* x3625)

#### **Detection of Cracks in Solar Cells**

The presence of hairline cracks in a photovoltaic solar cell can significantly degrade both the power output and the reliability of the cell. A technique based on the laser scanner has been developed to detect these tiny cracks, which frequently cannot be observed visually. In this technique the cell is forward biased during laser scanning either electrically with a current source or optically by shining light on the cell, or by a combination of both methods. The crack is revealed by a change in the slope of the photoresponse signal as the laser beam crosses the crack. In some cases, the magnitude of the photoresponse is different on the two sides of the crack so that there is also an abrupt change in magnitude of the signal as the beam crosses the crack. The photoresponse is displayed on a TV screen to permit visual observation of the cracked region. This technique can also be used to observe and identify regions of the grid metallization of a solar cell which are not in good contact with the cell emitter region (that portion of the cell between the p-n junction and the illuminated surface). Analysis of a distributed resistance representation of the solar cell predicts that the photoresponse to a scanning light beam should rise to a common maximum at the edges of the emitter metallization provided that (1) the metallization edge in question is \*NBS Contact.

electrically continuous to the cell leadwire and (2) a good ohmic contact exists between the metallization and the emitter. However, in regions of ineffectual contacting the analysis predicts that the signal should not rise. Observations on cells with known metallization faults confirmed the predictions of the analysis. These results were reported to the 13th IEEE Photovoltaic Specialists Conference in June. [Sponsor: 4](D. E. Sawyer, x3621)

#### Gated Diodes and CCD Dark Current

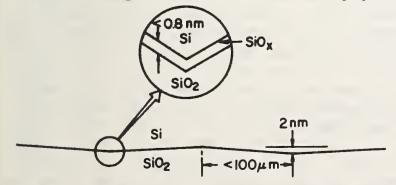

Preliminary measurements on a gated diode test structure suggest that this test structure will be useful in revealing unexpected and undesirable effects which impact directly on the performance of CCD imagers. With the addition of an on-chip MOSFET amplifier, which serves as an electrometer, the combined test structure becomes compatible with high-speed dc data acquisition techniques, and the diode dimensions can be reduced to sizes typical of integrated circuit elements. Initial measurements were made on 'the gated diode test structures on test pattern NBS-12, shown in the figure. These diodes were found to exhibit excess leakage currents

Computer-generated composite drawing of gated diode on bi-MOS test pattern NBS-12. Contact pads: G, gate; B, p<sup>+</sup> base diffusion (source); C; n-collector region (body).

at high gate potentials. Due to a geometrical configuration which maximizes the perimeter of the diode and its gate, surface generation occurring at the edges of the depletion layer, where it intersects the Si-SiO<sub>2</sub> interface, is enhanced. Zener emission and impact ionization may also contribute at edges or corners. Such excess leakage currents were initially unwelcome. However, it appears that their presence has serendipidously uncovered a likely mechanism for unexpected surface leakage in some CCD designs in which such leakage is likely to be manifested as an undesirable component of dark current in the output gates. Experiments are underway to further understand the nature of this surface leakage and how it depends on the design of the gated diode structure, including such parameters as the length of the gate perimeter, the overlap of the gate and the junction and channel stop diffusions, and the properties of the gate oxide. [Sponsor: 6] (G. P. Carver, x3541)

# Silicon Resistivity SRMs

Twenty additional sets of the silicon resistivity standard designated as SRM 1520: Boron-Doped Silicon Slices for Resistivity Measurement have been certified and are now ready for release. This standard reference material consists of two boron-doped silicon single-crystal slices, one with a nominal resistivity of 0.1  $\Omega$  cm, the other with a nominal resistivity of 10  $\Omega$  cm. The slices have a [111] crystallographic orientation and are approximately 42 mm in diameter and 1 mm thick. They are intended for use with four-probe resistivity testers. In addition, twenty more sets of such standards, identical to the above, except that the thickness has been reduced to less than 0.76 mm for use with contactless resistivity gauges in addition to the standard four-probe testers, have also been certified. These sets will be available under the designation, SRM 1521: Boron-Doped Silicon Slices for Resistivity Measurement. The SRM sets may be ordered from the Office of Standard Reference Materials, National Bureau of Standards, Washington,

DC 20234. The cost of each set is \$176. [Sponsor: 2] (J. R. Ehrstein, x3625)

#### Unintentional Ion Channeling Effects

Unintentional channeling during ion implantation can lead to the formation of undesirable deeply penetrating tails in the depth distributions of implanted dopants, especially during low fluence implantations. The magnitude of these dopant tails depends on the angle the ion beam makes with the substrate crystal axes. A joint effort was undertaken with Hughes Research Laboratories to analyze the variation of dopant profiles with the angle of beam incidence. Dopant profiles were dedifferential termined by capacitancevoltage measurements at 1-MHz. The results clearly indicate that the beam must be oriented at an angle with the nearest low-index crystal direction which is at least twice the classical critical angle for channeling in order to minimize unintentional channeling. The critical angles, which were calculated by a simple but accurate procedure, were found to vary from 2 to 7 deg from common industrial implants. Therefore, minimizing the extent of unintentional channeling during implantation requires tilt angles of 4 to 14 deg. These angles can easily exceed the 7to 10-deg tilt angles commonly used in implantation. These results are being written up as an NBS special publication. [Sponsors: 1,2] (D. R. Myers, \* x3625)

#### **Deep Level Measurements**

A comparative study is being initiated so that interested laboratories can assess their ability to accurately measure deep level impurities. In this study, a pair of gold-doped silicon gated diodes is available for measurement of defect energy levels and associated densities and emission rates by each interested laboratory. When sufficient results have been obtained, the measured values and the methods used by the participating laboratories will be compiled. However, the \*NBS-NRC Postdoctoral Research Associate. names of the participating laboratories will not be associated with their data in this compilation. It is hoped that this type of interlaboratory comparison will raise the general level of competence in the field of deep level measurements to a point that they will become more effectively and widely used by the semiconductor industry. Laboratories interested in participating in this comparative study should contact the Electron Devices Division, A353 Technology, NBS, Washington, DC 20234. [Sponsors: 1,2,3]

(D. R. Myers,\* x3625, W. E. Phillips, x3625, and R. Y. Koyama, x3625)

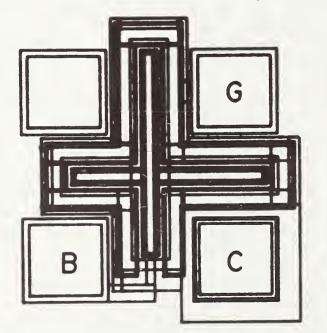

## Transferability of SOA Test Circuit

Safe-operating-area limits of forwardbiased bipolar transistors which exclude operation in the hot-spot, or currentconstricted, mode can be determined with the circuit shown schematically in the figure. The method involves the measurement of the time derivative of the emitter-base voltage, which shows a welldefined peak at the onset of hot-spot formation. The method and associated circuit were described at the 1977 IEEE Power Electronics Specialists Conference and the 1977 Annual Meeting of the IEEE Industrial

Block diagram of circuit used to generate SOA limit based upon the limit of thermal instability (switches in position A). With switches in position B circuit can be used to measure thermal resistance by the standard method. Applications Society. To aid in implementation of this method, NBS can provide detailed diagrams of the circuit. In addition, several different devices in TO-3 packages are available for circulation to groups who have built the NBSdeveloped test circuit so that they may evaluate their circuits. If enough organizations take advantage of this opportunity, the data will be summarized to establish an estimate of the interlaboratory reproducibility of the method. Groups desiring information on the method or to obtain the test devices should contact the Electron Devices Division, A353 Technology, NBS, Washington, DC 20234. [Sponsor: 2] (D. L. Blackburn, x3621)

#### Acoustic Material Signatures

Scanning acoustic micrographs of integrated circuits not only show a large range of contrast between adjacent details in the field of view, but the contrast can be varied or even reversed if the distance from the lens to the specimen is changed. To understand why this occurs, the acoustic reflectance of a variety of materials as a function of lens-to-specimen spacing

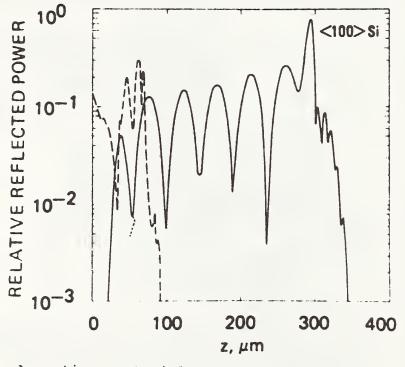

Acoustic material signature (relative reflected power as a function of lens-tospecimen spacing, z) for <100> surface of silicon.

has been measured at Hughes Research Laboratories. Each material so far examined has a unique reflectance characteristic, frequently with a number of strong minima whose depth and spacing differ for each. These minima are believed to arise because surface waves are excited in the material, and at specific lens-to-specimen distances destructive interference occurs between the normal acoustic return from the specimen and energy re-radiated from the surface wave. Since the velocity of propagation of surface waves is characteristic of the material, and also depends on the direction of propagation in the material, the reflected energy versus lens spacing response is material dependent. In specimens such as integrated circuits where several materials may be present, the contrast changes can be understood as superposition of responses of a the different materials. [Sponsor: 1]

(R. I. Scace, \* x3625)

#### Availability of Test Pattern NBS-4

for microelectronic test Documentation pattern NBS-4 is now available as NBS Special Publication 400-32 in the Semiconductor Measurement Technology series. The NBS-4 pattern contains 38 test structures such as planar four-probe resistors, sheet resistors, MOS capacitors, p-n junctions, bipolar and MOS transistors, Hall effect device, and etch control and resolution structures. The overall pattern is а square 200 mil (5.08 mm) on a side and is divided into four quadrants which are separated by scribe lines. This pattern designed principally for use was in measuring resistivity and dopant density of *n*- and *p*-type silicon slices with resistivity from  $10^{14}$  to  $10^{20}$   $\Omega \cdot cm$  at room temperature. It has been used both at NBS and at the University of Florida in studies to relate resistivity, carrier density, and dopant density in silicon. The structures contained on the pattern are, like those on earlier test patterns NBS-2 and NBS-3, also of value for measuring parameters in setting up and controlling processing of semiconductor \*NBS Contact.

6

devices. The earlier mask sets have been released to over 50 government, industrial, or academic laboratories. Requests for releasing the mask set for test pattern NBS-4 from a commercial mask-making company may be addressed to M. G. Buehler. The cost of a mask set is about \$200. [Sponsors: 1,2] (M. G. Buehler, x3541 and W. R. Thurber, x3625)

#### Moisture Measurement Workshop

The fifth in a series of ARPA/NBS workshops concerned with measurement problems in integrated circuit processing and assembly was held at NBS-Gaithersburg on March 22 and 23. The workshop examined present problems with the measurement of moisture in hermetic semiconductor devices, a dangerous and pervasive contaminant. The urgency of these problems is compounded by the recent adoption of moisture measurement test methods in MIL-STD-883. The workshop featured 20 formal talks and several group and panel discussions. The 150 attendees represented a broad spectrum of the semiconductor and related communities concerned with moisture measurement. The measurement approaches addressed in detail were those using mass spectrometers and moisture sensors (aluminum oxide and surface conductivity types). The workshop concluded: 1) for all of the methods used to make measurements in device packages, one can only talk about precision - not accuracy; 2) none of the measurement techniques now available is ready for use by inexperienced personnel; and 3) the precision or repeatability of moisture measurement will not really be satisfactory until much more is done to characterize mass spectrometers and moisture sensors in terms of all the variables, conditions, and applications that can affect the measurement. During the workshop, about 60 workshop attendees signed a formal request to NBS for assistance in moisture measurements, especially with respect to traceable standards. In addition, there were numerous expressions of interest in subsequent workshops on moisture measurement. [Spon-(H. A. Schafft, x3625) sor: 1]

#### SPV-PCD Lifetime Comparison

An investigation showed that bulk crystal damage near the semiconductor surface can lead to the often observed discrepancy between the bulk carrier lifetimes measured by the surface photovoltage (SPV) and photoconductive decay (PCD) methods. Both PCD and SPV measurements were made on high resistivity ( $\sim 100 \ \Omega \cdot cm$ ), high lifetime (0.1-1.0 ms) silicon slices. The lifetimes as measured by the PCD method on and chem-mechanically polished lapped specimens were consistently one to two orders of magnitude longer than those measured by the SPV method. Also, the SPV plot (intensity, I, versus reciprocal absorption coefficient,  $\alpha^{-1}$ ) was not linear as required by theory but was concave downward for  $a^{-1}$  greater than about 100 um. All of the assumptions of the SPV theory concerning specimen thickness with respect to  $a^{-1}$  and diffusion length were met. A theoretical analysis showed that the I versus  $a^{-1}$  data could be qualitatively explained by a two-lifetime model: a short lifetime near the surface and a long lifetime deeper within the bulk. It was found that after removal of the short-lifetime surface region by etching in a solution of 10 parts hydrofluoric acid, 6 parts of nitric acid, and 4 parts hydrochloric acid the SPV data showed the expected linear relationship, and the value of lifetime measured by the SPV method approached that measured by the PCD method. [Sponsor: 2]

(D. L. Blackburn, x3621)

## New Projects . . .

Photoresist Adhesion - A study of photoresist-substrate adhesion mechanisms has been initiated. Experiments are being conducted to determine the effect of a silica surface on the chemistry of the photoactive component of negative resist. In addition, model polymers are being synthesized. These will be used to determine the relationship between polymer adsorption and film adherence. [Sponsor: (J. A. Hinkley, \* x3621) 2] \*NBS-NRC Postdoctoral Research Associate.

Hydrogen Contamination in Thermal Oxides -Work has been initiated on analyzing the mechanisms through which hydrogen and hydroxyl impurities become incorporated into thin, thermally grown silicon dioxide films prepared in "dry" oxidation atmospheres enclosed in resistance-heated fused silica or silicon furnace tubes. Calculations of the hydrogen content in silicon dioxide films suitable for producing radiation-hardened MOS devices will be made in comparison with the available experimental results. Previous work indicates that environmental conditions such as the substrate, the purity of the oxidation atmosphere, and the furnace tube quality directly affect film composition and properties. The amount of water contamination in a typically nominally "dry" oxidation atmosphere, using electronic grade oxygen with no special preoxidation treatment, enclosed in a fused silicon tube at 1000°C is about 20 ppm. Consequently, the hydrogen and hydroxyl impurities in thin silicon dioxide films can probably be explained in terms of the water introduced into the oxidation atmosphere with the "dry" oxygen. This and other possible mechanisms will be examined quantitatively. [Sponsor: 5]

(S. Mayo, x3625)

Standard Reference Materials - A third standard reference material for four-probe resistivity measurements is being produced in order to provide the high-power semiconductor device industry with silicon slices of calibrated resistivity. The set will consist of three slices of neutron transmutation doped silicon with nominal room temperature resistivities of 25, 75, and 180  $\Omega$  cm. The slices are 51 mm in diameter and 0.64 mm thick.

In addition, a study has been undertaken to determine the effect of storage on the stability of the calibration value of thermally grown oxide on silicon to serve as standard reference materials for measurement of oxide film thickness. Silicon slices were thermally oxidized to form a silicon dioxide layer about 50 nm thick. Groups of four slices each are being stored under one of seven test conditions. The thickness of each oxide film is being measured ellipsometrically on a periodic basis to establish the short-term ( $\sim 2$ weeks) and long-term ( $\sim 6$  months) stability of the thickness. A similar set of tests is also to be run on 100-nm thick oxides. [Sponsor: 2] (J. R. Ehrstein, x3625)

Hall Measurements in Two-Layer Structures - In many cases it is desired to characterize by means of Hall effect and resistivity measurements two-layer structures in which there is a p-n junction at the interface. In general, the junction must be considered to have a finite, nonzero impedance which couples the two layers together and thus interferes with conventional Hall measurements. To meet the need for nondestructively characterizing such structures, a modification of the conventional Hall technique is being studied. In this modification which requires ohmic contacts to both layers, Hall measurements are made simultaneously on both layers, and the interface impedance is measured and taken into account. The equations necessary for analyzing the results of the measurements have been developed, and experimental tests of the method are being initiated. [Sponsor: 7]

(R. D. Larrabee, x3625)

<u>CMOS/SOS Test Pattern</u> - Work has begun on designing a test pattern (NBS-16) to develop process assessment methods which can be used by an independent source to evaluate the electrical performance, radiation tolerance, and yield potential of LSI circuits fabricated with a radiationhardened, silicon-gate CMOS/SOS process. The project is being carried out in collaboration with the Jet Propulsion Laboratories and RCA. NBS and JPL are designing the test pattern. After fabrication of the pattern by RCA under an AFAL contract, NBS and JPL will measure and evaluate the pattern. [Sponsor: 8]

(L. W. Linholm, x3541)

#### Work in Progress . . .

Hall effect and resistivity measurements on silicon specimens with phosphorus dopant densities in the range  $10^{19}$  to  $10^{20}$ cm<sup>-3</sup>, being made as part of the reevaluation of the resistivity-dopant density relations in silicon now nearing completion, suggest that for a given dopant density the resistivity is 5 to 10 percent lower than that given by the Irvin curve. [Sponsor: 1] (W. R. Thurber,x3625)

The feasibility of using plasma etching to form mesa diode structures for deep-level measurements on partially or fully fabricated thyristor wafers was demonstrated. With an available etch rate of about 40 um/h. mesa structures were routinely fabricated with a moat-etch as deep as 80 to 90 µm, which is compatible with junction depths in commercial thyristor structures. Studies have been initiated to determine the optimum technique for making contact to the high resistivity n-type region and for optimizing the size of the mesa diodes to compensate for lateral etching during mesa formation. [Sponsor: 3] (R. Y. Koyama, x3625, and J. Krawczyk, x3541)

Calibration of ten artifacts to be used in the interlaboratory evaluation of the line-width measurement procedure was completed. Following revision of the test instructions to incorporate calibration procedures for direct-reading TV-type microscope measuring instruments, the artifacts were distributed to the ten participants. [Sponsors: 1,2](J. M. Jerke, x2185)

Various limitations of the dc MOSFET method for measuring dopant profiles were analyzed. It was found that the principal limitations were those associated with the high-frequency fact that, as in capacitance-voltage methods, the dopant density is measured within the depletion layer so that profiles can be measured only where the material can be depleted of holes and electrons. Thus, the region from about three Debye lengths from the oxidesilicon interface to a depth limited by avalanche breakdown in the silicon can be profiled by these methods. [Sponsors: 1,5] (M. G. Buehler, x3541)

The ultraviolet reflectance technique, developed at RCA Laboratories to evaluate silicon films epitaxially grown on sapphire, has also been shown to be sensitive to surface damage on polished silicon wafers cut from single-crystal boules. [Sponsor: 1] (K. F. Galloway,\* x3625)

#### Recent Publications . . .

- Buehler, M. G., Microelectronic Test Patterns for Use in Procuring Custom and Highly Reproducible Integrated Circuits, Proc. Symposium on Utilization of LSICs in Military Systems, Arlington, Virginia, August 9-11, 1977, pp. III 102-III 117.

- Bullis, W. M., The NBS Semiconductor Technology Program, Proc. Symposium on Utilization of LSICs in Military Systems, Arlington, Virginia, August 9-11, 1977, pp. III 87-III 101.

- Sawyer, D. E., Solar Cell Measurement Technique Development and Other Services, Proc. Photovoltaics Program Semi-Annual Review, Advanced Materials R&D Branch, Golden, Colorado, October 4-6, 1977, pp. 708-713.

- Swyt, D. A., Rosberry, F. W., and Nyyssonen, D., Calibration of Optical Microscopes for Photomask Linewidth Measurements, *Proc. Microelectronics Seminar* - Interface '77, Monterey, California, October 5-7, 1977, pp. 131-144.

- Swyt, D. A., An NBS Physical Standard for the Calibration of Photomask Linewidth Measuring Systems, SPIE, Vol. 129, Effective Utilization of Optics in Quality Assurance, 98-105 (1977).

- Zanzucchi, P. J., Duffy, M. T., and Alig, R. C., Optical Reflectance Method for Determining Surface Quality of Sapphire, J. Electrochem. Soc. <u>125</u>, 299-305 (February 1978).

- Helms, C. R., Spicer, W. E., and Johnson, N. M., New Studies of the Si-SiO<sub>2</sub> Interface Using Auger Sputter Profiling, Solid State Comm. 25, 673-676 (March 1978).

- Koyama, R. Y., Blackburn, D. L., and Oettinger, F. F., Measurement Techniques for High Power Semiconductor Materials and Devices, Proc.: Light-Fired Thyristor Workshop, EPRI Report WS-77-049, unpaged (March 1978).

Buehler, M. G., and Thurber, W. R., An Experimental Study of Various Cross Sheet Resistor Test Structures, J. Electrochem. Soc. 125, 645-650 (April 1978).

<sup>\*</sup> NBS Contact.

<sup>+</sup> Reports of Contract Research.

Buehler, M. G., Grant, S. D., and Thurber, W. R., Bridge and van der Pauw Sheet Resistors for Characterizing the Line Width of Conducting Layers, J. Electrochem. Soc. 125, 650-654 (April 1978).

- \*Christou, A., Semiconductor Measurement Technology: Automated Scanning Low-Energy Electron Probe (ASLEEP) for Semiconductor Wafer Diagnostics, NBS Spec. Publ 400-30 (April 1978).

- Galloway, K. F., and Mayo, S., Radiation Dose at the Silicon-Sapphire Interface Due to Electron-Beam Metallization, J. Appl. Phys. 49, 2586-2588 (April 1978).

- Novotny, D. B., and Ciarlo, D. R., Semiconductor Measurement Technology: Automated Photomask Inspection, NBS Spec. Publ. 400-46 (April 1978).

- Thurber, W. R., and Carpenter, B. S., Boron Determination in Silicon by the Nuclear Track Technique, J. Electrochem. Soc. 125, 654-657 (April 1978).

- Thurber, W. R., and Buehler, M. G., Semiconductor Measurement Technology: Microelectronic Test Pattern NBS-4, NBS Spec. Publ. 400-32 (April 1978).

Publications in Press . . .

- \*Atalar, A., An Angular Spectrum Approach to Contrast in Reflection Acoustic Microscopy, J. Appl. Phys.

- Blackburn, D. L., Photovoltaic Technique for Measuring Resistivity Variations of High Resistivity Silicon Slices, NBS J. Res.

- Blackburn, D. L., and Larrabee, R. D., Automated Photovoltaic Technique for Nondestructively Measuring Resistivity Variations of High-Resistivity Silicon Wafers, Proc. Topical Conf. on Characterization Techniques for Semiconductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- Buehler, M. G., Microelectronic Test Patterns for Use in Procuring LSICs, Proc. Industry/Joint Services Automatic Test Conf. and Workshop, San Diego, California, April 4-6, 1978.

- Buehler, M. G., Limitations and Applications of the D-C MOSFET Profile Method, *Proc. Topical Conf. on Characterization* \* Reports of Contract Research.

Techniques for Semiconductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- Bullis, W. M., Government Programs on Advanced Technology and Manufacturing Techniques: Comments on USA, Japan, and Europe, NBSIR 78-1482.

- Bullis, W. M., and Mayo-Wells, J. F., Eds, Semiconductor Measurement Technology, Progress Report, July 1 to September 30, 1976, NBS Spec. Publ. 400-36.

- Galloway, K. F., and Mayo, S., On The Compatibility of X-Ray Lithography and SOS Device Fabrication, *IEEE Trans. Electron Devices*.

- \*Grunthaner, F. J., and Maserjian, J., Chemical Structure of the Transition Region of the SiO<sub>2</sub>/Si Interface, Proc. Internat. Topical Conf. on Physics of SiO<sub>2</sub> and Its Interfaces, Yorktown Heights, New York, March 22-24, 1978.

- Harman, G. G., and Cannon, C. A., The Microelectronic Wire Bond Pull Test - How to Use It, How to Abuse It, Proc. 28th Electronic Components Conf., Anaheim, California, April 24-26, 1978.

- \*Helms, C. R., Johnson, N. M., Schwarz, S. A., and Spicer, W. E., Auger Sputter Profiling Studies of the Si-SiO<sub>2</sub> Interface, *Proc. Internat. Topical Conf. on Physics of SiO<sub>2</sub> and Its Interfaces*, Yorktown Heights, New York, March 22-24, 1978.

- \*Helms, C. R., Johnson, N. M., Schwarz, S. A., and Spicer, W. E., Auger Sputter Profiling Studies of the Si-SiO<sub>2</sub> Interface, Proc. Topical Conf. on Characterization Techniques for Semiconductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- \*Jamba, D. M., Secondary Particle Collection in Ion Implantation Dose Measurement, *Rev. Sci. Instrum*.

- Koyama, R. Y., Detection of Deep Levels in High Power Semiconductor Materials and Devices, NBS J. Res.

- Koyama, R. Y., Phillips, W. E., Myers, D. R., Liu, Y. M., and Dietrich, H. B., The Energy Levels and the Defect Signature of Sulfur-Implanted Silicon by ITCAP and TSC Measurements, Solid-State Electronics.

- Koyama, R. Y., Wafer Mapping of Electrically Active Devices, Proc. Topical Conf. on Characterization Techniques for Semi-(Continued on Back Cover)

NBS-114A (REV. 7-73) U.S. DEPT. OF COMM. 1. PUBLICATION OR REPORT NO. 2. Gov't Accession 3. Recipient's Accession No. BIBLIOGRAPHIC DATA No. NBSIR 78-1444-2 SHEET 4. TITLE AND SUBTITLE 5. Publication Date July 1978 Semiconductor Technology Program - Progress Briefs 6. Performing Organization Code 7. AUTHOR(S) W. M. Bullis 8. Performing Organ. Report No. 9. PERFORMING ORGANIZATION NAME AND ADDRESS 10. Project/Task/Work Unit No. NATIONAL BUREAU OF STANDARDS 11. Contract/Grant No. DEPARTMENT OF COMMERCE WASHINGTON, D.C. 20234 and various contractor facilities (as noted) See item 15 13. Type of Report & Period Covered Interim 12. Sponsoring Organization Name and Complete Address (Street, City, State, ZIP) NBS, Washington, DC 20234; APPA, Arlington, VA 22209; DNA, Washington, January - March 1978 DC 20305; Dept. of Energy, Washington, DC 20545; C. S. Draper Laboratory, Cambridge, MA 02139; AFAL, Wright-Patterson AFB, OH 45433; Army 14. Sponsoring Agency Code Electronics R&D Command, Ft. Belvoir, VA 22060. **15. SUPPLEMENTARY NOTES** ARPA Order 2397; Program Code 8Y10; DNA IACRO 78-807; Dept. of Energy, Interagency Agreement EX-77-A01-6010, Task Orders A021-EES and A054-SE; C. S. Draper Laboratory, P. O. DL-H-139485 (Navy contract N 00030-78-C-0100); AFAL, MIPR FY117578N2026; Army Electronics, MERADCOM, P. 0. 28052. 16. ABSTRACT (A 200-word or less factual summary of most significant information. If document includes a significant bibliography or literature survey, mention it here.) This report provides information on the current status of NBS work in measurement technology for semiconductor materials, process control, and devices. Results of both inhouse and contract research are covered. Highlighted activities include: profiling of the Si-SiO<sub>2</sub> interface by Auger electron and x-ray photoelectron spectroscopies; use of the laser scanner to detect hairline cracks in solar cells; use of gated diodes in evaluation of CCD imager wafers; availability of silicon resistivity standard reference materials; observation of unintentional channeling effects in low-fluence random equivalent ion implantations; initiation of a comparative study of deep level measurements; implementation of the NBS-designed circuit for determining safe-operating-area limits of forward-biased transistors; observation of acoustic material signatures; availability of test pattern NBS-4; conduct of a workshop on moisture measurements; and comparison of carrier lifetimes as measured by the surface photovoltage and photoconductive decay methods. In addition, brief descriptions of new and selected on-going projects are given. The report is not meant to be exhaustive; contacts for obtaining further information are listed. Compilations of recent publications and publications in press are also included. 2000 17. KEY WORDS (six to twelve entries; alphabetical order; capitalize only the first letter of the first key word unless a proper name; separated by semicolons) Electronics; integrated circuits; measurement technology; microelectronics; semiconductor devices; semiconductor materials; semiconductor process control; silicon. 21. NO. OF PAGES 19. SECURITY CLASS 18. AVAILABILITY X Unlimited (THIS REPORT) 12 For Official Distribution. Do Not Release to NTIS UNCL ASSIFIED Order From Sup. of Doc., U.S. Government Printing Office Washington, D.C. 20402, <u>SD Cat. No. C13</u> 22. Price 20. SECURITY CLASS (THIS PAGE) \$4.00 X Order From National Technical Information Service (NTIS) UNCLASSIFIED Springfield, Virginia 22151

USCOMM-DC 29042-P74

(Continued from Page 10)

conductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- Koyama, R. Y., Techniques for Characterizing Defects in Starting Silicon Wafers Using TSM, Proc. Topical Conf. on Characterization Techniques for Semiconductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- Larrabee, R. D., Interpretation of Hall Measurements, Proc. Topical Conf. on Characterization Techniques for Semiconductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- Larrabee, R. D., "X" Levels in Indium-Doped Silicon, Proc. IRIS Specialty Group Meeting, Annapolis, Maryland, June 13-15, 1978.

- \*Li, S. S., The Dopant Density and Temperature Dependence of Hole Mobility and Resistivity in Boron-Doped Silicon, Solid-State Electronics.

- Myers, D. R., and Phillips, W. E., Existence of an Isotope Shift for the Sulfur Deep Level in Silicon, Appl. Phys. Letters.

- Novotny, D. B., and Ciarlo, D. R., Automated Photomask Inspection, Solid State Technology.

- Nyyssonen, D., Optical Linewidth Measurements on Wafers, SPIE, Vol. 135, Developments in Semiconductor Microlithography III.

- \* Reports of Contract Research.

- Oettinger, F. F., Ed, Measurement Techniques for High Power Semiconductor Materials and Devices, NBSIR 78-1474.

- Sawyer, D. E., A Technique for Using an Optical Scanner to Reveal Solar Cell Defects, Proc. 13th IEEE Photovoltaic Specialists Conference.

- \*Schwarz, S. A., Helms, C. R., and Spicer, W. E., Auger Sputter Profiling Studies of Dopant Pileup at the Si-SiO<sub>2</sub> Interface, J. Vac. Sci. Technol.

- \*Strausser, Y. E., Scheibner, E. J., and Johannessen, J. S., Observations of Al<sub>2</sub>O<sub>3</sub> and Free Si in the Interface Between Al Films and SiO<sub>2</sub>, Thin Solid Films.

- \*Strausser, Y. E., and Majumder, K. S., The Chemical Structure of the Al/SiO<sub>2</sub> Interface, J. Vac. Sci. Tech.

- Thurber, W. R., Mattis, R. L., and Liu, Y. M., Resistivity-Dopant Density Relationship for Silicon, Proc. Topical Conf. on Characterization Techniques for Semiconductor Materials and Devices, Seattle, Washington, May 21-26, 1978.

- \*Weglein, R. D., and Wilson, R. G., An Acoustic Gray Scale for Scanning Acoustic Microscopy and Diagnostic Ultrasound, *Ultrasound Imaging*.

- \*Wilson, R. G., and Weglein, R. D., Acoustic Material Signatures Using the Reflection Acoustic Microscope, Proc. 1st Internat. Symp. Ultrasonics Matls. Characterization, Washington, D.C., June 8-10, 1978.

U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary

Dr. Sidney Harman, Under Secretary

Jordan J. Baruch, Assistant Secretary for Science and Technology

NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director