NBS SPECIAL PUBLICATION 400-14

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

Semiconductor Measurement Technology.

Thermal Resistance Measurements on Power Transistors

### NATIONAL BUREAU OF STANDARDS

The National Bureau of Standards¹ was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau's technical work is performed by the National Measurement Laboratory, the National Engineering Laboratory, and the Institute for Computer Sciences and Technology.

THE NATIONAL MEASUREMENT LABORATORY provides the national system of physical and chemical and materials measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; conducts materials research leading to improved methods of measurement, standards, and data on the properties of materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government Agencies; develops, produces, and distributes Standard Reference Materials; and provides calibration services. The Laboratory consists of the following centers:

Absolute Physical Quantities<sup>2</sup> — Radiation Research — Thermodynamics and Molecular Science — Analytical Chemistry — Materials Science.

THE NATIONAL ENGINEERING LABORATORY provides technology and technical services to users in the public and private sectors to address national needs and to solve national problems in the public interest; conducts research in engineering and applied science in support of objectives in these efforts; builds and maintains competence in the necessary disciplines required to carry out this research and technical service; develops engineering data and measurement capabilities; provides engineering measurement traceability services; develops test methods and proposes engineering standards and code changes; develops and proposes new engineering practices; and develops and improves mechanisms to transfer results of its research to the utlimate user. The Laboratory consists of the following centers:

Applied Mathematics — Electronics and Electrical Engineering<sup>2</sup> — Mechanical Engineering and Process Technology<sup>2</sup> — Building Technology — Fire Research — Consumer Product Technology — Field Methods.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides scientific and technical services to aid Federal Agencies in the selection, acquisition, application, and use of computer technology to improve effectiveness and economy in Government operations in accordance with Public Law 89-306 (40 U.S.C. 759), relevant Executive Orders, and other directives; carries out this mission by managing the Federal Information Processing Standards Program, developing Federal ADP standards guidelines, and managing Federal participation in ADP voluntary standardization activities; provides scientific and technological advisory services and assistance to Federal Agencies; and provides the technical foundation for computer-related policies of the Federal Government. The Institute consists of the following divisions:

Systems and Software — Computer Systems Engineering — Information Technology.

<sup>2</sup>Some divisions within the center are located at Boulder, Colorado, 80303.

Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

Semiconductor Measurement Technology:

# Thermal Resistance Measurements on Power Transistors

Sherwin Rubin and Frank F. Oettinger

Electron Devices Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Washington, DC 20234

U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary

Jordan J. Baruch, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director

Issued April 1979

# Library of Congress Cataloging in Publication Data

Rubin, Sherwin.

Thermal resistance measurements on power transistors.

(Semiconductor measurement technology) (NBS special publication , 400-14)

Supt. of Docs. no.: C 13.10:400-14

1. Power transistors—Thermal properties. 2. Semiconductors—Junctions. I. Oettinger, Frank F., jointauthor. II. Title. III. Series. IV. Series: United States. National Bureau of Standards. Special publication; 400-14.

QC100.U57 no. 400-14 [TK7871.92] 602'.1s [621.3815'2] 79-9984

National Bureau of Standards Special Publication 400-14

Nat. Bur. Stand. (U.S.), Spec. Publ. 400-14, 69 pages (Apr. 1979) CODEN: XNBSAV

U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1979

# TABLE OF CONTENTS

|      |                   |                                                   |                        |                |                  |                                 |                 |                        |                |                        |                |                         |                       |                   |                   |                   |            |                 |                                |          |     |     |    |    |     |        |     |   |   | Page                           |

|------|-------------------|---------------------------------------------------|------------------------|----------------|------------------|---------------------------------|-----------------|------------------------|----------------|------------------------|----------------|-------------------------|-----------------------|-------------------|-------------------|-------------------|------------|-----------------|--------------------------------|----------|-----|-----|----|----|-----|--------|-----|---|---|--------------------------------|

| Abs  | tract             |                                                   |                        |                |                  |                                 |                 |                        | •              | •                      |                | •                       | •                     |                   | •                 |                   | •          |                 |                                |          |     |     |    | •  |     |        |     |   |   | 1                              |

| 1.   | Intro             | oduc                                              | tic                    | n              |                  |                                 |                 |                        |                |                        |                | •                       |                       |                   | •                 | •                 |            | •               |                                |          |     |     |    |    |     |        |     |   | • | 1                              |

| 2.   | The (             | Conc                                              | ept                    | : c            | f                | Τŀ                              | ıeı             | ma                     | 1              | Re                     | si             | ist                     | tai                   | nce               | 9                 |                   |            | •               |                                |          |     | •   |    |    | •   |        | •   |   |   | 2                              |

| 3.   | Elect             | trica                                             | al                     | Μe             | as               | sui                             | en              | ner                    | ıt             | of                     |                | Γhe                     | eri                   | na]               | L I               | \es               | sis        | sta             | ano                            | ce       |     |     |    |    |     | •      |     |   |   | 3                              |

|      | 3.1<br>3.2        | Con                                               |                        |                |                  |                                 |                 |                        |                |                        |                |                         |                       |                   |                   |                   |            |                 |                                |          |     |     |    |    |     |        |     |   |   | 3<br>4                         |

| 4.   | Prefe             | erre                                              | 1 E                    | Ξ1ε            | ect              | ri                              | ca              | 1                      | Мє             | eas                    | uı             | cen                     | ner                   | ıt                | Ме                | etł               | 100        | 1               |                                | •        |     | •   |    |    |     |        |     | • |   | 7                              |

|      | 4.1<br>4.2<br>4.3 | Meas<br>Test<br>Spec<br>4.3<br>4.3<br>4.3<br>Simp | t (<br>cia<br>.1<br>.2 | Cir<br>al<br>M | Pr<br>fea<br>)so | iit<br>cec<br>asu<br>cil<br>era | au<br>iri<br>la | es<br>iti<br>ng<br>iti | or<br>or<br>or | ip<br>Cur<br>ns<br>Cor | ar<br>re<br>ir | ior<br>nd<br>ent<br>n t | Co<br>Co<br>he<br>Lor | ons<br>Cor<br>E I | sid<br>nsi<br>Dev | lei<br>lde<br>vic | ratera     | ic<br>at:<br>Ur | ons<br>ion<br>ion<br>de<br>Dev | ns<br>er | Te  | est |    |    | Te  | ·<br>· | •   | • | • | 7<br>8<br>11<br>11<br>12<br>12 |

|      |                   | Use<br>4.4<br>4.4                                 | . 1                    | S              | in               | ıp]                             | if              | ie                     | d              | Ca                     | 11             | Ĺbı                     | cat                   | ic                | n                 | Pı                | 00         | cec             | luı                            | e:       |     |     |    |    |     |        |     |   |   | 18<br>18<br>18                 |

| 5.   | Ther              | nal !                                             | Res                    | spc            | ns               | e                               | Μe              | as                     | ur             | en                     | er             | nts                     | s f                   | or                | : I               | ì∈                | 2 <i>A</i> | \t t            | ac                             | hr       | ner | ıt  | Ev | a1 | lua | ıti    | Lor | 1 | • | 20                             |

| 6.   | Conc              | lusio                                             | ons                    | 3              | •                |                                 |                 |                        |                |                        |                |                         |                       | •                 |                   | •                 |            | •               | •                              |          |     | •   |    | •  |     |        |     | • | • | 21                             |

| 7.   | Refe              | cence                                             | es                     |                |                  | •                               |                 | •                      |                |                        |                |                         |                       |                   |                   |                   |            |                 |                                |          |     |     |    |    |     | •      |     |   |   | 23                             |

| Арре | endix             | ı.                                                |                        |                | •                |                                 |                 |                        |                |                        |                |                         |                       |                   |                   |                   |            |                 |                                |          |     |     |    |    |     |        |     |   |   | 25                             |

| Арре | endix             | II                                                | •                      | •              |                  | •                               |                 |                        | •              |                        |                |                         |                       |                   |                   | •                 |            |                 |                                |          |     |     |    |    |     |        |     |   |   | 39                             |

| Арре | endix             | III                                               |                        |                |                  | •                               |                 |                        |                |                        |                |                         |                       | •                 |                   |                   |            |                 |                                |          |     |     |    |    |     |        |     | • |   | 45                             |

| Appe | endix             | IV                                                | •                      | •              | •                | •                               | •               | •                      |                | •                      |                |                         |                       |                   |                   |                   |            |                 |                                |          |     |     |    |    |     |        |     |   |   | 59                             |

| Арре | endix             | v .                                               | •                      |                |                  |                                 |                 |                        |                |                        |                |                         |                       |                   |                   |                   |            |                 |                                |          |     |     |    |    |     |        |     |   |   | 61                             |

# LIST OF FIGURES

|    |                                                                                                                                   |   | Page |

|----|-----------------------------------------------------------------------------------------------------------------------------------|---|------|

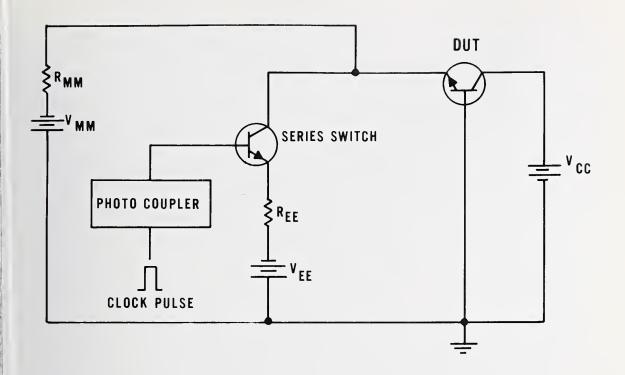

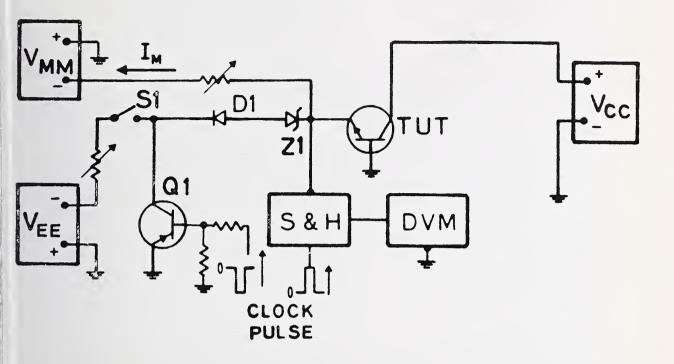

| 1. | Basic circuits for measuring thermal resistance by the emitter-only switching technique                                           | • | 9    |

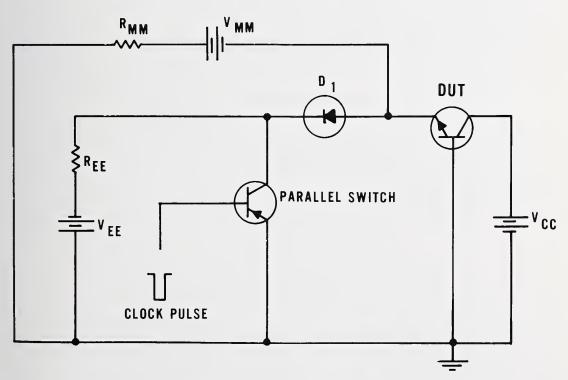

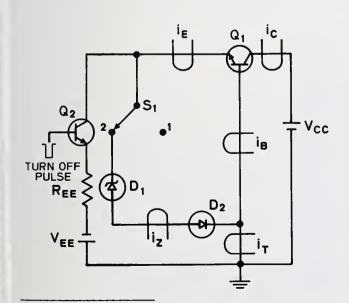

| 2. | Block diagram for the emitter-only switching circuit used to measure $npn$ transistor thermal resistance                          | • | 10   |

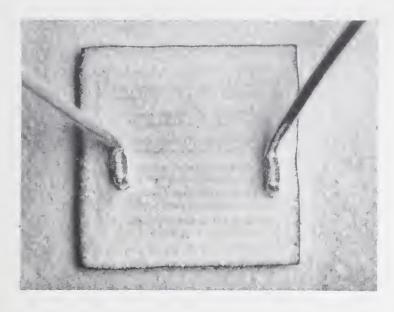

| 3. | A 125-W power transistor coated with a thermographic phosphor shown for two different operating conditions, each dissipating 50 W |   | 13   |

| 4. | Measured thermal resistance as a function of collector current at a constant power of 20 W for a 35-W triple-diffused transistor  |   | 15   |

| 5. | Cooling curves for a transistor operated with a collector current of 4 A and various emitter-collector voltages                   | • | 17   |

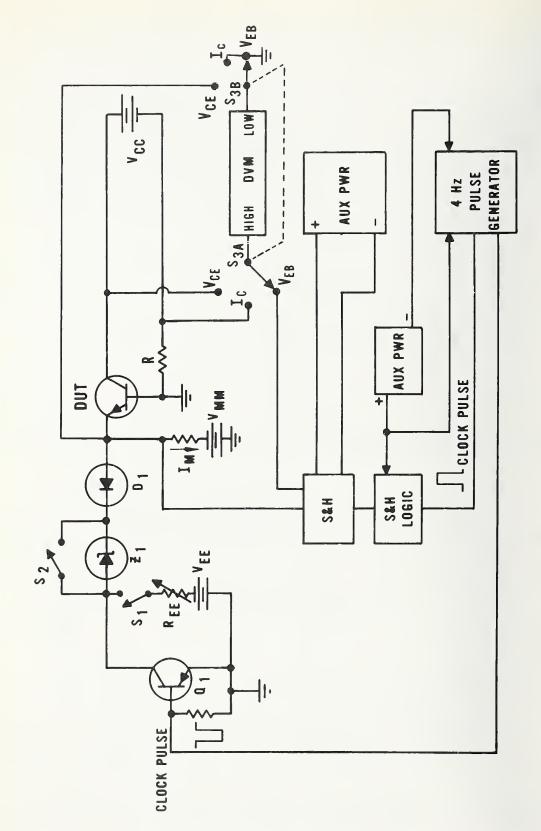

| 6. | Block diagram for thermal response measuring system for npn transistors                                                           |   | 22   |

### **PREFACE**

This study, which resulted in a recommended procedure for measuring the thermal resistance of power transistors, was conducted as part of the Semiconductor Technology Program in the Electron Devices Division of the National Bureau of Standards (NBS). This Program serves to focus NBS research to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in specifying materials and devices in national and international commerce and for use by industry in controlling device fabrication processes. This research leads to the development of carefully evaluated and well-documented test procedures and associated technology. Special emphasis is placed on the dissemination of the results of the research to the electronics community. Application of these results by industry will contribute to higher yields, lower cost, and higher reliability of semiconductor devices. Improved measurement technology provides a common basis for the purchase specifications of government agencies which will lead to greater economy in government procurement and, in addition, provides a basis for controlled improvements in fabrication processes and in essential device characteristics. The Semiconductor Technology Program is carried out with funds from a multiplicity of sponsoring agencies; the specific work reported herein was funded by NBS.

The authors are indebted to several persons who assisted in the editing and preparation of this report. David L. Blackburn performed a critical and constructive reading of the text. The figures were prepared by William A. Cullins and Leo R. Williams. The typing of the final draft was done by E. Jane Walters.

### DISCLAIMER

Certain commercial equipment, instruments, or materials are identified in this report in order to adequately specify the experimental procedure. In no case does such identification imply recommendation or endorsement by the National Bureau of Standards, nor does it imply that the material or equipment identified is necessarily the best available for the purpose.

# Semiconductor Measurement Technology:

Thermal Resistance Measurements on Power Transistors

bу

Sherwin Rubin and Frank F. Oettinger

Abstract: A brief description of the idealized concept of thermal resistance is given along with the problems and pitfalls encountered in applying the concept to power transistors. In addition, the advantages and disadvantages of various electrical techniques for measuring junction temperature (thermal resistance) are described, and a preferred, standard technique is discussed in detail. This preferred technique, in which the forward-biased emitter-base junction is used as the temperature-sensitive parameter, is usable on all types of bipolar transistors. The measurement procedure is relatively simple and lends itself to industrial measurements as well as for referee purposes. The power interruption circuitry is also relatively fast and simple since only one device terminal is switched. The preferred technique that was developed for measuring the thermal resistance of power transistors has been adopted as EIA Recommended Standard RS-313-B on Thermal Resistance Measurements of Conduction Cooled Power Transistors, dated October 1975.

Key Words: Current crowding; die attachment evaluation; junction temperature; measurement technology; power transistors; semiconductor devices; thermal characterization; thermal resistance; transistors.

### 1. Introduction

The thermal characterization of power semiconductor devices is important for predicting the reliability and performance of these devices and for ensuring their safe operation. Manufacturers usually specify a thermal resistance,  $R_{\theta}$ , and a maximum safe junction temperature,  $T_{J(\max)}$ . The specified thermal resistance is assumed to be constant for each device and is used to calculate the device junction temperature as a function of power dissipation for a given mounting arrangement and case or ambient temperature. Ultimately,  $R_{\theta}$  is used to ensure that  $T_{J(\max)}$  is not exceeded during operation. The effect of exceeding the rated maximum safe junction temperature can range from a change in the electrical characteristics of the device to catastrophic failure. Thus, a knowledge of the operating junction temperature is critical for predicting device quality, reliability, and performance. For speed and simplicity of production line screening and to enable device users to duplicate the measurements, electrical measurement methods are usually used for determining device thermal resistance. However, there are problems with this ap-

proach that had been brought to our attention by industrial standards organizations, manufacturers and users of devices, and military and space agencies. Measurements were not repeatable within the desired precision due to the use of different test procedures and device operating conditions. The effect of current crowding on the accuracy of the electrical measurement of thermal resistance was not widely understood. This led to buyer-seller disagreements and in some cases to failure through misuse.

On the recommendation of these semiconductor manufacturers and users and of other government agencies, the National Bureau of Standards initiated a study of methods for nondestructively measuring the thermal resistance of power transistors in order to develop a satisfactory referee test method. Based on the criteria that the method must be easy to perform, precise, nondestructive, as accurate as possible, and usable at the working level, the emitter-only switching technique (in which the forward-biased emitter-base junction is used as the temperature-sensitive parameter) was found to be the preferred procedure for measuring the thermal resistance of power transistors.

This paper discusses the concept of thermal resistance, its short-comings, and the care that must be exercised when it is used for specifying or checking the thermal characteristics of a device. Electrical techniques for measuring junction temperature (thermal resistance) of power transistors are discussed in some detail with the emphasis on the preferred method, now adopted as a standard technique [1] (reprinted with permission of EIA in Appendix I).

# 2. The Concept of Thermal Resistance

Thermal resistance has been used over the years as an aid to device manufacturers and users for calculating the junction temperature of operating devices. The concept of thermal resistance is based upon an analogy between the electrical and thermal properties of materials, with temperature, power dissipation, and thermal resistance being analogous to voltage, current, and electrical resistance, respectively. The thermal resistance ( $R_{\rm A,IR}$ ) is defined as follows:

$$R_{\theta JR} = \frac{T_J - T_R}{P} \tag{1}$$

where:

- $R_{\theta JR}$  = thermal resistance between the junction and the reference point, in degrees Celsius/watt,

- $\mathbf{T}_{\mathbf{J}},~\mathbf{T}_{\mathbf{R}}$  = temperatures of the junction and the reference point, respectively, in degrees Celsius, and

- P = power dissipated in the device, in watts.

In applying the electrical analogy to the thermal problem and in using eq (1), it is implicitly assumed that uniform current and temperature distributions exist across the junction of the device under test and that one-dimensional heat flow occurs from a planar heat source. These assumptions imply a unique value of thermal resistance for devices of a given design and construction. Since these assumptions are not completely valid for actual power transistors, care is needed in applying the results of eq (1) to real devices [2].

# 3. Electrical Measurement of Thermal Resistance

Because a power transistor cannot always be characterized by a unique value of thermal resistance for all operating conditions due to such effects as current crowding, it is very important to be able to measure the critical junction temperature for a variety of operating conditions. Ideally, the measurement method chosen should 1) yield a temperature as close to the peak junction temperature as possible, 2) be easy to perform, 3) be precise, and 4) be nondestructive. The most commonly used methods for measuring the junction temperature of a semiconductor device utilize a temperature-sensitive electrical parameter (TSP) of the device as the temperature indicator. Although electrical techniques do not always directly yield the peak junction temperature, they are non-destructive, are generally simple to perform, and can be precise.

A number of electrical parameters, such as the forward-biased collector-base voltage ( $V_{CR}$ ), the d-c forward current gain ( $h_{FR}$ ), the collector-base leakage current ( $I_{CBO}$ ), and the forward-biased emitter-base voltage ( $V_{EB}$ ) have been used as temperature indicators. In addition, various techniques have been used for monitoring each of these parameters; all these techniques can generally be put into one of two generic classes: 1) continuous methods and 2) switched or pulsed methods. Each of the techniques relies on the ability to simply and uniquely relate the TSP to junction temperature. The degree that this is possible is a major factor in assessing the worth of a particular technique. A brief description of the use of the various electrical parameters as TSPs is given below followed by a detailed description of a preferred technique which most closely meets the requirements of the ideal measurement method. With minor modifications, the circuit used for the preferred method for measuring thermal resistance can also be used to measure the transient thermal response of devices [3], the thermal resistance of integrated Darlington power transistors [4], and the quality of the die attach of devices (using the transient thermal response) [5].

### 3.1 Continuous Electrical Methods

In these methods, the TSP is monitored while the device is operating in an active, power-dissipating mode. In one version [6], the case, ambient, or other reference point is elevated to a high temperature  $(T_2)$ , not exceeding the maximum junction temperature. The collector current  $(I_C)$  is set and a collector-base voltage  $(V_2)$  applied to the

device. The TSP is measured under these conditions and then the reference temperature is reduced to a lower temperature  $(T_1)$  and the collector-base voltage increased to a value  $V_1$  until the same value of the TSP is measured as was measured above. The thermal resistance is then

$$R_{\theta} = \frac{T_2 - T_1}{I_C(V_1 - V_2)}.$$

(2)

The dc current gain  $(h_{FE})$  [6] and the base-emitter voltage  $(V_{BE})$  [7] have been used as transistor TSPs for measuring temperature by the continuous method.

It is generally assumed with continuous methods that the TSP (h\_FE or V\_BE) varies monotonically with temperature and that variations in the TSP as a result of the changes in the temperature are much greater than variations as a result of changes in the collector-base voltage (V\_CB).\* Unfortunately, both h\_FE and V\_BE may be strong functions of V\_CB, and it is often difficult to separate these electrical effects from the desired thermal effects. For example, in the continuous V\_BE method, a correction for the Early effect [8] may have to be included [9]. The added complexity required for this correction negates the apparent simplicity of the continuous  $V_{BE}$  method. In addition, it has been found that  $h_{FE}$  may not vary monotonically with  $V_{CB}$  because of changes in the device current density as the collector voltage is varied [10]. Thus, although the continuous methods appear at first glance to be simple, they are not recommended for use in making temperature measurements of semiconductor devices because of the difficulties mentioned.

# 3.2 Switched or Pulsed Methods

Switched or pulsed electrical methods require that the device be rapidly switched between a condition of high power dissipation and a condition of very low or zero power dissipation. In switched methods, the TSP is monitored during the low power dissipation condition immediately after the removal of a high power dissipation d-c operating condition. The calibration of the TSP against junction temperature is performed at the low power condition. In pulsed methods, the TSP is monitored during the high power dissipation d-c condition, while calibration of the TSP against junction temperature is performed by monitoring the TSP during a very short pulse at the same high power level. In both techniques, it is assumed that the junction temperature rise above the reference is negligible during the calibration procedure. The switched methods achieve this by a very low power dissipation, while the pulsed methods achieve this by a very short pulse of high power. Thus, the ref-

<sup>\*</sup> An example of the use of this assumption can be found in Method 3132, Thermal Resistance (DC Forward Voltage Drop, Emitter Base, Continuous Method) of MIL-STD-750B, February 27, 1970.

erence point temperature is indicative of the junction temperature under these conditions. The transistor TSPs that have been used in measuring thermal resistance by switched or pulsed methods are the collector-base current ( $I_{CBO}$ ) [11], the d-c forward current gain ( $h_{FE}$ ) [12], the collector-base forward voltage ( $V_{CB}$ ) [13], and the emitter-base forward voltage ( $V_{EB}$ ) [14].

Since  $h_{FE}$  can be a double-valued function of temperature, it is not recommended for use as the TSP. The switched method using  $I_{CBO}$  as the TSP is generally limited to measurements on germanium devices having relatively large bulk leakage currents and is of no real interest for the majority of modern silicon devices where surface and bulk leakage current effects may be of the same order.

The switched methods which use  $V_{EB}$  or  $V_{CB}$  as the TSP are generally equally precise. However, it has been found that  $V_{EB}$  when used as the TSP tends to indicate a junction temperature nearer the peak temperature than does  $V_{CB}$ , and, in addition, the switching techniques are simpler for the  $V_{EB}$  methods. In contrast to the other methods discussed, the circuit variations used to implement the switched  $V_{EB}$  techniques are numerous [14,15,16]. It can also be shown that switched  $V_{EB}$  methods are simpler to perform than the pulsed  $V_{EB}$  methods and under conditions of current crowding tend to indicate a junction temperature nearer to the peak temperature due to differences in calibration operating conditions. The switched  $V_{EB}$  technique that has been found to be the easiest to perform and to generally yield a temperature closest to the peak junction temperature is one in which the device under test operates as a transistor both during the heating and TSP monitoring or calibration procedures. This approach has come to be known as the  $V_{EB}$  emitter-only switching technique and is the preferred method for measuring the junction-to-case thermal resistance  $(R_{\theta,IC})$ .

Table 1 presents a comparison of measurements of  $R_{\theta JC}$  using the preferred  $V_{EB}$  emitter-only switching technique with other switching techniques. The data were extracted from measurements made by the National Bureau of Standards for use in a preliminary round-robin experiment on thermal resistance conducted in cooperation with EIA-JEDEC Committee JC-25 on Power Transistors. These data illustrate the apparent differences in thermal resistance when measured using a variety of electrical techniques. Eleven devices were measured. Three were encased in T0-66 cans and eight in T0-3 cans. As expected, the  $V_{CB}$  technique gave lower values of thermal resistance than the  $V_{BE}$  base-and-collector switching technique, which in turn was lower than the  $V_{EB}$  emitter-only switching technique. It is this latter method that has been adopted as a standard technique for measuring the junction temperature of power transistors [1].

<sup>\*</sup> This round robin was conducted under the auspices of Committee JC-25 on Power Transistors of the Solid State Products Division, Joint Electron Devices Engineering Council, Electronic Industries Association.

Table 1

Comparison of Different Electrical Techniques for Measuring the Thermal Resistance of Power Transistors

| Device | Case  | Measured Thermal Resistance<br>(°C/W) |                             |                     |  |  |  |  |  |  |

|--------|-------|---------------------------------------|-----------------------------|---------------------|--|--|--|--|--|--|

| Number | Туре  | V <sub>CB</sub><br>as TSP             | V <sub>BE</sub> †<br>as TSP | V *<br>EB<br>as TSP |  |  |  |  |  |  |

| A-2    | то-3  | 1.00                                  | 1.09                        | 1.41                |  |  |  |  |  |  |

| B-1    | то-3  | 0.74                                  | 0.90                        | 1.06                |  |  |  |  |  |  |

| B-2    | то-3  | 0.96                                  | 0.99                        | 1.24                |  |  |  |  |  |  |

| B-41   | то-3  | 0.48                                  | 0.53                        | 0.71                |  |  |  |  |  |  |

| B-42   | то-3  | 0.46                                  | 0.50                        | 0.71                |  |  |  |  |  |  |

| D-2    | то-3  | 0.41                                  | 0.48                        | 0.56                |  |  |  |  |  |  |

| D-3    | то-3  | 0.41                                  | 0.46                        | 0.55                |  |  |  |  |  |  |

| W-2    | то-3  | 0.38                                  | 0.40                        | 0.61                |  |  |  |  |  |  |

| W-3    | то-66 | 1.69                                  | 1.79                        | 2.34                |  |  |  |  |  |  |

| W-4    | то-66 | 1.69                                  | 1.79                        | 2.40                |  |  |  |  |  |  |

| D-4    | то-66 | 1.47                                  | 1.52                        | 1.74                |  |  |  |  |  |  |

$<sup>^{\</sup>dagger}$ Base and collector switching (device under test is operated as a diode during TSP monitoring or calibration).

<sup>\*</sup>Emitter-only switching.

## 4. Preferred Electrical Measurement Method

The emitter-only switching technique in which the forward-biased emitter-base junction is used as the temperature-sensitive parameter is usable on all types of bipolar power transistors. The measurement procedure is relatively simple and lends itself to industrial measurements as well as for referee purposes. The power interruption circuitry is also relatively fast and simple since only one device terminal is switched. The technique also gives unambiguous results when current crowding occurs.

# 4.1 Measurement Procedure

In this method the emitter-base forward voltage ( $V_{EB}$ ) is used as the TSP to indicate the junction temperature. The test procedure involves the measurement of the TSP as part of two steps, the power application and the calibration steps. In the power application step,  $V_{EB}$  is measured to determine the increase in the junction temperature due to power dissipation in the device under test. During the calibration step,  $V_{EB}$  is measured to determine the temperature coefficient of the device under test. A more detailed description of the measurement procedure is given in Appendix I where EIA Recommended Standard RS-313-B on Thermal Resistance of Conduction Cooled Power Transistors is reproduced by permission of the EIA. In this standard, the thermal resistance is given as:

$$R_{\theta JR} = \frac{T_J - T_R}{P_{(AVG)}} = \frac{V_{M2} - V_{MC} \text{ (for } T_{MC} = T_R)}{DP_2} \cdot \left[\frac{\Delta V_{MC}}{\Delta T_{MC}}\right]^{-1}$$

(3)

where:

$R_{\theta JR}$  = thermal resistance, junction-to-reference point, in degrees Celsius/watt,

$T_{\tau}$  = junction temperature, in degrees Celsius,

$T_{p}$  = reference point temperature, in degrees Celsius,

$^{P}(AVG)$  = average heating power applied to transistor causing temperature difference  $T_{J}$  -  $T_{R}$ , in watts,

P<sub>2</sub> = magnitude of heating power applied to transistor, in watts,

$V_{M2}$  = value of TSP corresponding to the temperature of the junction heated by  $P_2$  and measured at the measuring current  $(I_M)$ , in millivolts,

D = heating power duty factor (%1),

$(\Delta V_{MC}/\Delta T_{MC})$  = TSP temperature coefficient measured at  $I_{M}$ , in millivolts/degrees Celsius,

T<sub>MC</sub> = calibration temperature measured at reference point, in degrees Celsius, and

$V_{MC}$  = values of TSP during calibration at  $I_{M}$  and specific values of  $T_{MC}$  in millivolts.

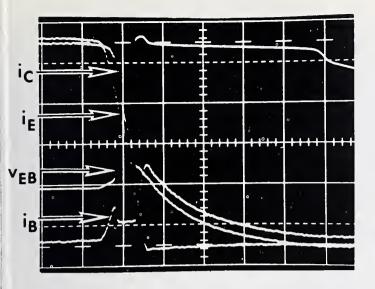

# 4.2 Test Circuit Description

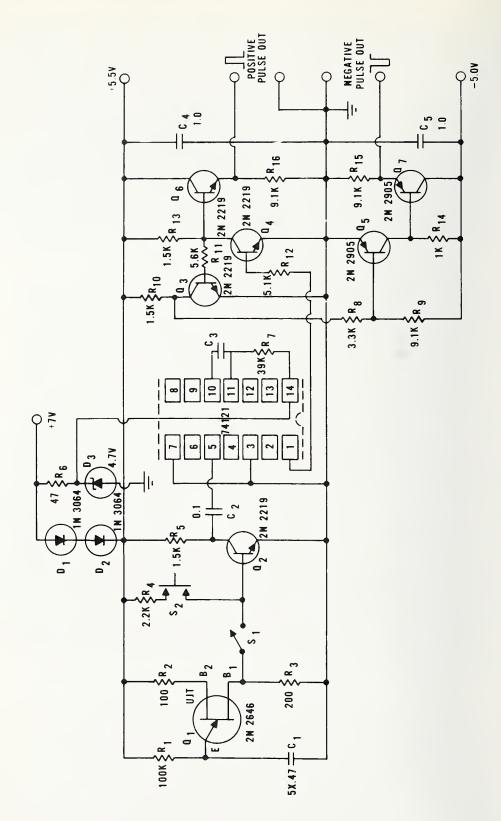

There are two basic test circuits used for the emitter-only thermal resistance measuring procedure. As can be seen in figure 1, the emitter has two current sources, one attached permanently which provides the constant measuring current and the other active only during the heating portion of the test cycle. The switching action is provided by a switch that either interrupts the emitter current by opening the line (series switching) or by shunting the emitter supply current to another path (parallel switching) as indicated in figure la and lb, respectively.

The circuit in figure la offers no protection against reverse-biased emitter-base breakdown which can occur during switching. It was found that the process of rapidly reducing the emitter current from a very high value during heating to a very low value during measurement while the collector remained connected to its voltage supply could result in reverse-bias breakdown of the emitter-base junction of some transistors. Since the transistor may be damaged by reverse-biased breakdown of the emitter-base junction [17], fast switching circuits such as those needed for measurement of thermal resistance must be designed to avoid the possibility of such breakdown. A detailed explanation of the characteristics of the emitter-base voltage and current transients which occur when switching the emitter with a series transistor during measurement of thermal resistance is given in Appendix II together with a description of a proposed model.

Although the emitter-base voltage can be limited to a value below the breakdown voltage with a protective circuit based on the use of a regulator (zener) diode, a better solution is to use the parallel switching scheme. In this method, the emitter-base voltage is limited to the drop across the series diode Dl during switching. This method has the added advantage that parallel switching is a far superior procedure for high currents. For this reason, the preferred circuit for measuring the thermal resistance of power transistors utilizes parallel switching in the emitter lead to interrupt the heating current to the device under test (DUT).

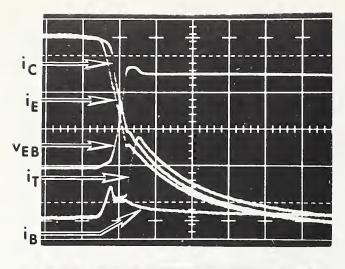

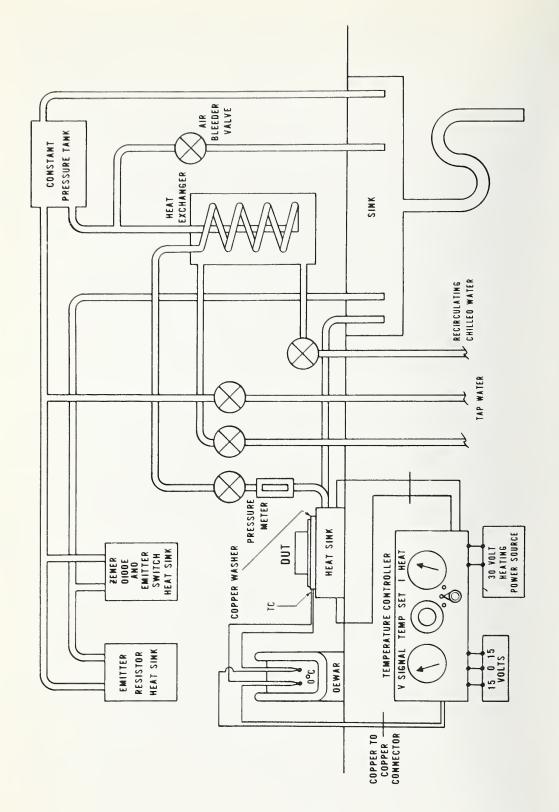

The block diagram for the emitter-only switching circuit used to measure the thermal resistance of npn transistors, utilizing parallel switching in the emitter of the DUT, is given in figure 2.\* The circuit is controlled by a clock pulse with a pulse width of approximately 300  $\mu$ s and a repetition rate of approximately 4 Hz. When the voltage level of the clock pulse is zero, the transistor Q<sub>1</sub> is off and the current through the DUT is the sum of the heating current (switch S<sub>1</sub> closed) and

<sup>\*</sup> This test method can also be applied to pnp devices by appropriate polarity charges in the test circuit elements.

Figure 1. Basic circuits for measuring thermal resistance by the emitter-only switching technique. (a) series switching, (b) parallel switching.

Figure 2. Block diagram for the emitter-only switching circuit used to measure npn transistor thermal resistance.

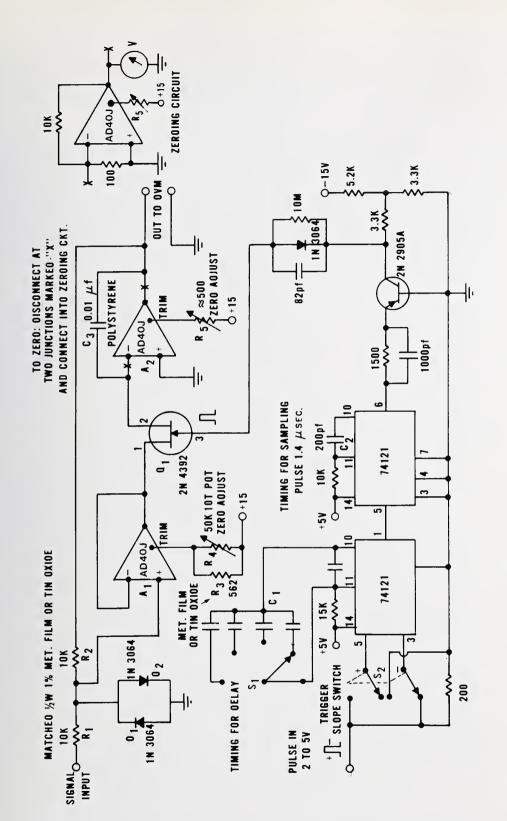

the measuring current  $I_M$ . The constant heating current is furnished by the  $V_{\rm EE}$  supply, and the constant measuring current by the  $V_{\rm MM}$  supply. At the end of each heating power pulse, the clock assumes a specified nonzero level for a period of time ( $\sim 300~\mu s$ ) that is short compared with the heating interval ( $\sim 250~m s$ ). This is sufficient to bias the transistor  $Q_1$  on, which reverse biases the diode D1 so that the heating current no longer passes through the DUT. The function of the optional regulator (zener) diode  $Z_1$  is to decrease the switching time of the DUT. The regulator voltage,  $V_Z$ , of the diode  $Z_1$  should be equal to or less than the maximum rated  $V_{EBO}$  of the DUT. The sample-and-hold unit (S&H) is triggered when the heating current is removed and after a delay, usually 5 to  $100~\mu s$ , senses the TSP,  $V_{M2}$ , for a  $1.5-\mu s$  period and displays its value on the digital voltmeter (DVM). The temperature coefficient of the TSP and the calibration correlation voltage  $V_{MC}$  (for  $T_{MC} = T_R$ ) are obtained by making the required measurements with the heating current supply disconnected (switch  $S_1$  open). The digital voltmeter used to measure the TSP is also used to measure the power dissipation of the DUT as indicated by the DVM switch  $S_3$ . A noninductive current-sensing resistor R is used to measure the collector current  $I_C$ .

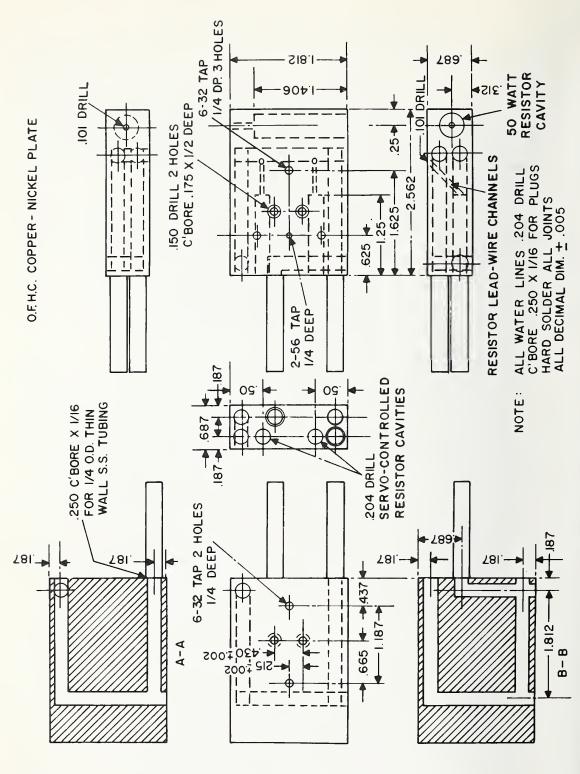

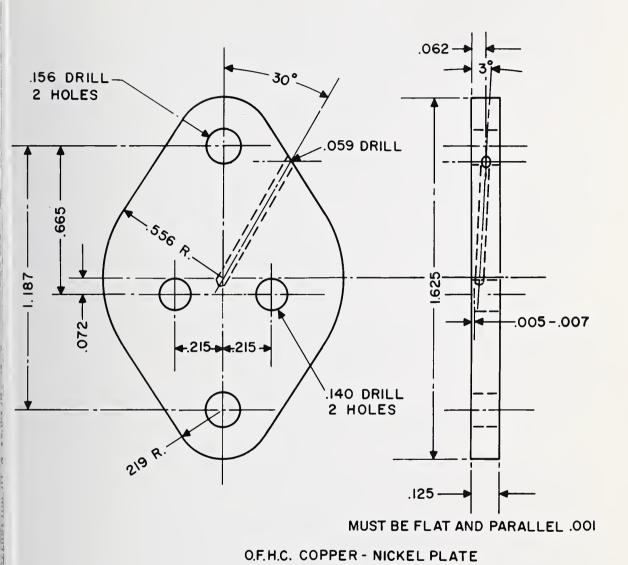

Details of the instrumentation to implement the  $V_{EB}$  emitter-only switching method for measuring the thermal resistance of power transistors are given in Appendix III. This appendix includes a description of the basic circuit itself as well as a description of the clock pulse generator, the sample-and-hold circuit, the temperature controller, and the temperature-controlled, water-cooled heat sink. Appendix IV describes the results of long-term, single-operator measurements to check the repeatability of the equipment for measuring thermal resistance described in Appendix III.

# 4.3 Special Precautions and Considerations

There are several special precautions and considerations that must be taken into account when measuring the thermal resistance of power transistors. They generally relate to the nonideal characteristics of semiconductor devices and interactions of the device under test with the measuring system. They range from such questions as to how to pick the measuring current to how to prevent oscillations in the device under test.

# 4.3.1 Measuring Current Considerations

As indicated previously, the measuring current is generally selected such that the TSP varies linearly with temperature over the range of interest and that negligible internal heating occurs during the calibration procedure and measuring interval. A measuring current equal to 0.1 percent of the maximum rated collector current ( $I_{\text{C}(\max)}$ ) of the device under test will generally meet this criterion. Generally, a measuring current of a few milliamperes is acceptable for the large majority of medium power transistors.

It has also been found that, for some devices, the calibration curve deviates from its normally linear slope for junction temperatures above 150 to 175°C due to high leakage current effects. When this happens, a best fit linear line to the actual curve, over the temperature range of interest, generally gives the required accuracy of measurement. If this is not the case for the particular temperature range of interest, the actual calibration curve should be plotted and the junction temperature due to internal power dissipation read off the curve.

# 4.3.2 Oscillations in the Device Under Test

The occurrence of oscillations in the device under test can make it impossible to determine the actual power dissipation for calculations of thermal resistance. Also, the measurement of the TSP within the required time after the heating power is terminated becomes difficult, if not impossible, if oscillations occur.

The use of lossy ferrite beads on the emitter and base leads of the device under test has been found to be an effective means of attenuating unwanted high frequency oscillations. Lossy ferrite beads selectively absorb rf energy, being most effective at the higher frequencies where feedback energy causes oscillation. The effectiveness of the beads depends on the relative magnitude and frequency distribution of the source, the ferrite bead, and the load impedances.

It has also been found that a capacitor may be required between the collector and base (ground) of the device under test to prevent oscillations. The value of the capacitor has to be large enough to damp the oscillations and may require parallel capacitors so as not to become series resonant within the frequency range of the test equipment.

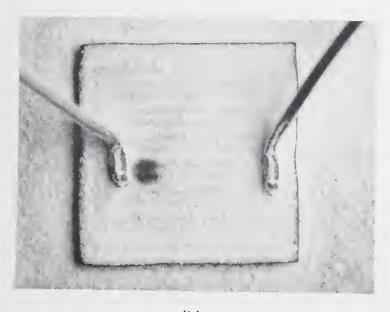

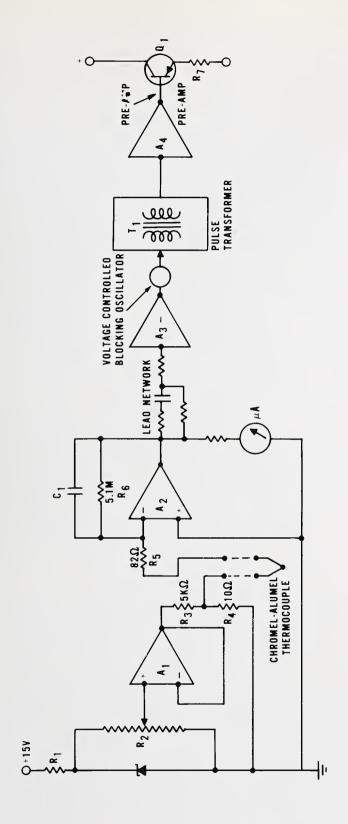

# 4.3.3 Operating Conditions of the Device Under Test

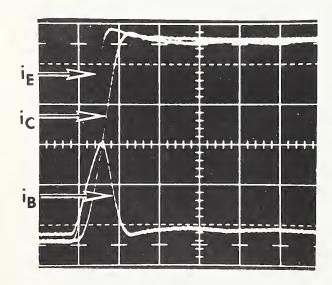

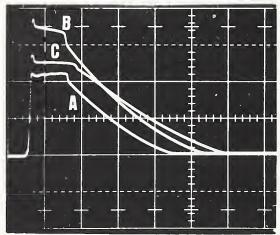

The ability of the  $V_{EB}$  emitter-only technique to accurately measure the peak junction temperature is greatly dependent on the degree of heating current nonuniformity that exists within the active region of the semiconductor chip. The degree of current crowding is dependent on the device operating conditions even under constant heating power situations where  $P_2 ~ ^{\circ} I_C V_{CE}$  [10,18]. An example of this can be seen in figure 3 for a 125-W triple-diffused power transistor which is dissipating 50 W of power for two different operating conditions. The device is coated with a thermographic phosphor [19] which appears darkest at the hottest areas of the device in this figure. For the low-current, high-voltage condition ( $I_C = 0.25$  A,  $V_C = 200$  V), the power density is much more localized (as evidenced by the very dark "hot spot") than for the other operating condition. Even though the power dissipation in the transistor was held constant, the peak junction temperatures are dramatically different. In this case, the difference is approximately 150°C.

(a)

(b)

Figure 3. A 125-W power transistor coated with a thermographic phosphor shown for two different operating conditions, each dissipating 50 W. The phosphor when illuminated with ultraviolet radiation as done here is brightest at the cooler areas and darkest at the hotter areas. (a) I  $_{\rm C}$  = 1.0 A, V  $_{\rm CE}$  = 50 V; (b) I  $_{\rm C}$  = 0.25 A, V  $_{\rm CE}$  = 200 V.

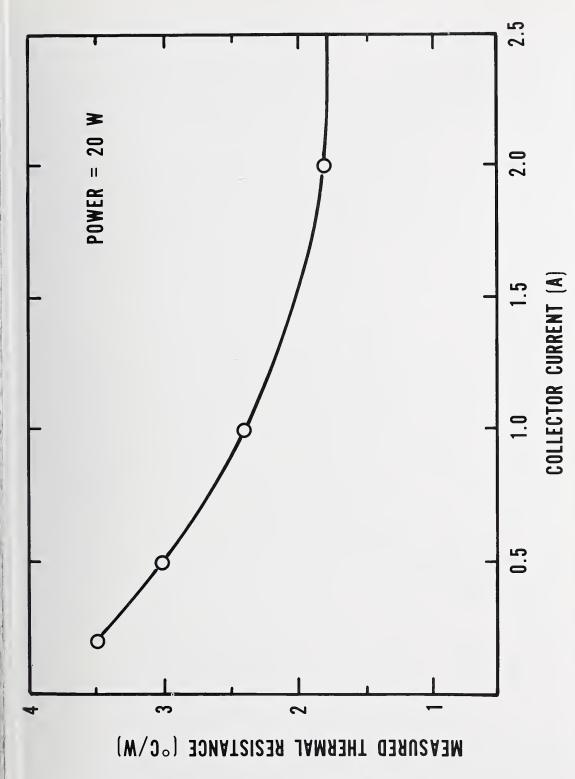

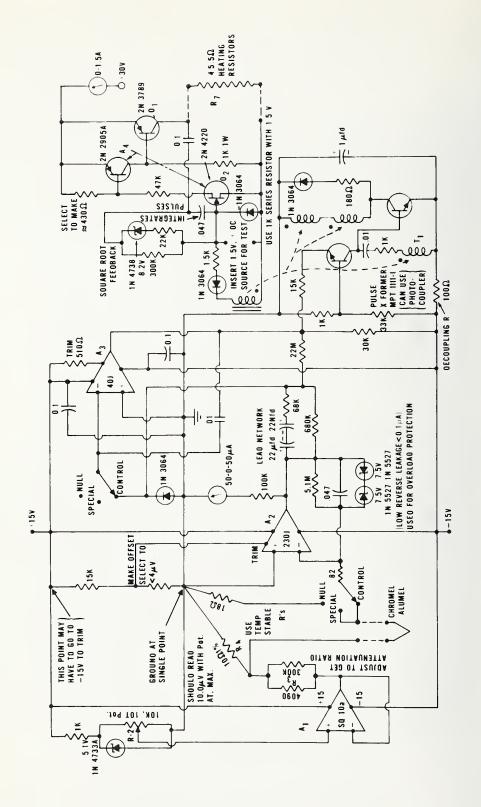

In general, for low-current, high-voltage operation, the measured thermal resistance is a strong function of operating conditions. At the other extreme, high current and low voltage, it is not as strong a function of the operating conditions. This can be seen in figure 4, which shows a plot of measured thermal resistance versus collector current at constant power for a 35-W power transistor. Data taken on three power transistors at various operating conditions, comparing indirect and direct measurements of thermal resistance, are summarized in table 2. It can be seen from the data that, as the degree of current crowding increases, the electrically measured thermal resistance deviates further from the actual peak thermal resistance as determined from direct measurements with an infrared microradiometer.

The reason for the large values of R $_{\theta JR}$  at low values of I $_{C}$  is that the thermal-electrical feedback mechanisms that initiate current crowding and eventually second breakdown [20] are stronger at small values of I $_{C}$  than at large values. Thus, the current tends to be more constricted and the peak temperature higher for these conditions.

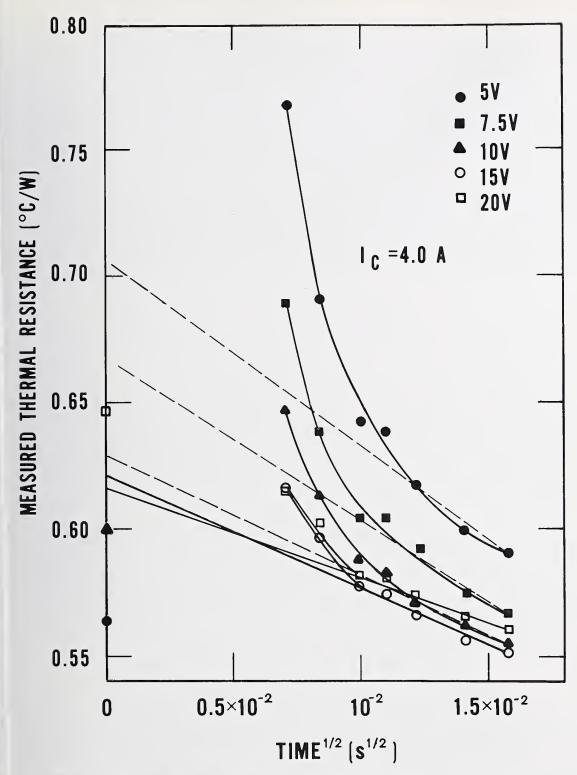

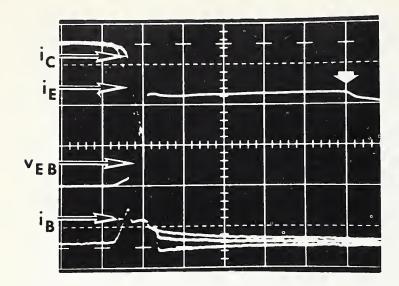

The fact that for high-current, low-voltage operation the thermal resistance is generally not a strong function of device operating conditions does not mean that measurements at low collector voltage and high collector current are without difficulties. For example, the extremely long switching times of devices operating in the quasi-saturation region [21] make thermal resistance measurements using a switching technique in this region of operation essentially meaningless. cause the part of the measured  $V_{pp}$  which arises from a long-lived nonthermal transient, which is due to the large density of stored charge, cannot be separated out from the desired thermal part. The problems encountered are illustrated in figure 5, which shows the measured thermal resistance of a 35-W power transistor plotted against the square root of the time after cessation of power for a transistor with collector current of 4 A and a range of values of collector-emitter voltage, VCE.\* The device is operating in the quasi-saturation mode at 5 and 7.5 V and is just beginning to come out at 10 V. Note that for 5, 7.5, and 10 V there is almost no linear portion of the curve as would be predicted by the extrapolation procedures based on one-dimensional cooling [3]; the nonlinearity indicates that nonthermal switching transients are present.

The thermal resistance at 5, 10, and 20 V as calculated from measurements of the peak junction temperature with an infrared microradiometer are also indicated in the figure at zero time. Because the electrical method is known to average the junction temperature, it should always indicate a temperature less than the peak temperature. Only at 20 V is this the case; at 5 V, the electrically measured temperature is greater than the peak temperature even after the device has cooled for 250  $\mu s$ . This arises because the nonthermal switching transients completely obscure the temperature dependence of the junction voltage. Thus, operat-

<sup>\*</sup>This extrapolation procedure is discussed in Appendix C of Appendix I of this report; also see 4.4.2.

Figure 4. Measured thermal resistance as a function of collector current at a constant power of 20 W for a 35-W triple-diffused transistor.

Table 2

Comparison of Electrical and Infrared Techniques for Measuring the Thermal Resistance of Power Transistors under Various Device Operating Conditions

| Device | Specified R <sub>θ</sub> JC | Operating Condition                    | Power | Measured Thermal Resistance (°C/W) |                             |  |  |  |  |

|--------|-----------------------------|----------------------------------------|-------|------------------------------------|-----------------------------|--|--|--|--|

| Number | (°C/W)                      | I <sub>C</sub> (A)/V <sub>CE</sub> (V) | (W)   | Standard<br>Electrical             | Infrared<br>Microradiometer |  |  |  |  |

|        |                             | 0.1/170                                | 17    | 8.5                                | 14.6                        |  |  |  |  |

|        |                             | 0.2/105                                | 21    | 5.5                                | 9.0                         |  |  |  |  |

| 1      | 5                           | 0.4/80                                 | 32    | 4.2                                | 5.5                         |  |  |  |  |

|        |                             | 1.0/54                                 | 54    | 3.0                                | 3.4                         |  |  |  |  |

|        |                             | 2.0/33                                 | 66    | 2.5                                | 2.7                         |  |  |  |  |

|        |                             | 0.2/140                                | 28    | 2.9                                | 4.6                         |  |  |  |  |

|        |                             | 0.3/106                                | 32    | 2.8                                | 4.0                         |  |  |  |  |

| 2      | 1.5                         | 1.0/44                                 | 44    | 2.4                                | 2.9                         |  |  |  |  |

|        |                             | 2.0/38                                 | 76    | 1.9                                | 2.1                         |  |  |  |  |

|        |                             | 0.6/76                                 | 46    | 3.3                                | 3.8                         |  |  |  |  |

| 2      | 7                           | 1.0/50                                 | 50    | 3.0                                | 3.4                         |  |  |  |  |

| 3      | 7                           | 2.0/28                                 | 56    | 3.0                                | 3.2                         |  |  |  |  |

| 100    |                             | 3.0/20                                 | 60    | 2.8                                | 2.9                         |  |  |  |  |

Figure 5. Cooling curves for a transistor operated with a collector current of 4 A and various emitter-collector voltages. Data points at zero time are derived from measurements of the peak junction temperature with an infrared microradiometer.

ing conditions that place the device under test in the quasi-saturation region should be avoided when making thermal resistance measurements.

# 4.4 Simplification of Measurement Procedure for Industrial Use

The basic procedure for measuring the thermal resistance of power transistors using the  $V_{\rm FB}$  emitter-only switching technique was developed as a referee test method, although the ability to use the technique in the industrial environment was a major criterion involved in its selection. This section deals with modifications to the basic procedure to allow measurements to be made in an industrial environment with greater speed and without significant loss in precision and accuracy. Discussed are simplifications to the measurement procedure that allow testing of devices of a given design and construction to be accomplished without determining the calibration coefficient and extrapolated value of the TSP for each device being measured.

# 4.4.1 Simplified Calibration Procedure

When thermal resistance measurements are being made on a large number of devices of a given design and construction, the use of a simplified calibration procedure is often acceptable. It can generally be assumed that under these conditions the slope of the calibration curve (the temperature coefficient of the TSP) is relatively constant. Data, extracted from a study on the use of thermal response for die attachment evaluation [5] taken on 42 transistors mounted on TO-5 headers, indicated that the relative sample standard deviation of the calibration slope was 1.2 percent. Thus, if the processing for a particular device type does not change, then the slope of the calibration curve should not vary by more than a few percent.

The validity of the assumption that the temperature coefficient of the TSP is relatively constant can be verified in the following manner. The temperature coefficient should be measured on 10 devices of the same design and construction as those to be tested. If the relative sample standard deviation of these measurements is less than or equal to  $\pm 3$  percent, the average of the measured temperature coefficients can be used in the calculation of thermal resistance for all other devices of that design and construction.\*

# 4.4.2 Simplified Extrapolation Procedure

In measuring thermal resistance using the switched method, it would seem desirable to measure the TSP at the exact instant that the heating

<sup>\*</sup> This validation procedure was developed in conjunction with EIA-JEDEC Committee JC-13.1 on Government Liaison for Discrete Semiconductor Devices for use in a revision of Method 3131 on Thermal Resistance of MIL-STD-750. The revised test method for measuring the thermal resistance of transistors is designated Method 3131.1 and can be found in MIL-STD-750B, Notice 9, dated September 19, 1978.

power is removed, since the junction temperature is maximum at that time. However, this is not possible because 1) it takes a finite time for the transistor current to decay from the heating value to the measuring value and 2) transients exist in the measuring voltage waveform for some time after the measuring current value is reached due primarily to charge storage effects in the device under test (as discussed in 4.3.3). Because some semiconductor element cooling occurs during this delay period, the TSP may have to be extrapolated back to the time when the heating power was terminated (see Appendix C of Appendix I for details).

The extrapolation procedure is based on the assumption that the heat source thickness is small compared to the total chip thickness and that for approximately the first 250  $\mu s$  of cooling one-dimensional heat flow occurs [3]. During this period, a proportionality factor, K, which relates the change in T<sub>J</sub> during cooling to  $t^{1/2}$  [see eq (1) of Appendix C of Appendix I] can be defined as follows:

$$K = \frac{T_{J2} - T_{J1}}{t_1^{1/2} - t_2^{1/2}}$$

(4)

where:

t = delay time after heating power is terminated, in microseconds,

$T_{11}$  = junction temperature at time t =  $t_1$ , in degrees Celsius, and

$T_{J2}$  = junction temperature at time t =  $t_2 < t_1$ , in degrees Celsius.

When thermal resistance measurements are being made on a large number of devices of a given design and construction, the use of a simplified extrapolation procedure is often acceptable. Under these conditions and for a given set of device operating conditions ( $V_{CE}$ ,  $I_{C}$ , and  $I_{M}$ ), the proportionality factor, K, is relatively constant. It was also shown in section 4.4.1 that a single value of the temperature coefficient of the TSP is also appropriate for devices of a given design and construction. Then the extrapolation correction factor (K') is given by:

$$K' = \frac{V_{M2(1)} - V_{M2(2)}}{t_1^{1/2} - t_2^{1/2}} = K \left[ \frac{\Delta V_{MC}}{\Delta T_{MC}} \right]$$

Calibration (5)

where K' is the slope of the  $V_{M2}$  versus  $t^{1/2}$  cooling curve for the first 250  $\mu$ s of device cooling and  $V_{M2}$  (1) and  $V_{M2}$  (2) are measured at t<sub>1</sub> and t<sub>2</sub>, respectively.

The basic relationship used to calculate the thermal resistance [see eq (3)] can be modified as follows to take into account the use of the constant extrapolation correction factor (K'):

$$R_{\theta JR} = \frac{V_{M2} - V_{MC} - K't^{1/2}}{DP_2} \cdot \left[\frac{\Delta V_{MC}}{\Delta T_{MC}}\right]^{-1}$$

(6)

where  $V_{M2}$  is measured at time t. (For greatest precision, t should be as small as possible, consistent with  $t_2 \le t \le t_1$ .)

To validate the assumption that a single extrapolation correction factor (K') can be used, the extrapolated slope of the cooling curve should be measured for 10 devices of the same design, construction, and operating conditions as those to be tested. If the relative sample standard deviation of these measurements is less than or equal to  $\pm 3$  percent, the average extrapolation correction factor can be used in the calculation of thermal resistance for all other devices of that design and construction.\* Since the cooling curve during the first 250  $\mu s$  of cooling is proportional to the area of conduction of the transistor, the use of this simplified extrapolation procedure is not recommended for operating conditions at which current crowding occurs.

# 5. Thermal Response Measurements for Die Attachment Evaluation\*\*

Both the steady-state thermal response (or thermal resistance) and the transient thermal response of semiconductor devices are sensitive to the presence of voids in the die attachment material between the semiconductor chip and header since these voids impede the flow of heat from the chip to the case (header). Due to the difference in the thermal time constants of the chip and case, the measurement of transient thermal response can be made more sensitive to the presence of voids than can the measurement of steady-state thermal response. This is because the chip thermal time constant is generally several orders of magnitude shorter than that of the case. Thus, the heating power pulse width can be selected so that only the chip and the chip-to-case interface are heated during the pulse by using a pulse width somewhat greater than the chip thermal time constant, but less than that of the case. Heating power pulse widths ranging from 5 to 10 ms have been found to satisfy this criterion. This enables the detection of voids to be greatly enhanced, with

<sup>\*</sup> This validation procedure was developed in conjunction with EIA-JEDEC Committee JC-13.1 on Government Liaison for Discrete Semiconductor Devices for use in a revision of Method 3131 on Thermal Resistance of MIL-STD-750. The revised test method for measuring the thermal resistance of transistors is designated Method 3131.1 and can be found in MIL-STD-750B, Notice 9, dated September 19, 1978. In Method 3131.1, the extrapolation correction factor, K', is labeled K. [See Appendix V of this report for information on the equivalency of symbols used in the commercial and military thermal resistance test methods for transistors.]

<sup>\*\*</sup> This procedure is incorporated in EIA Recommended Standard RS-313-B, Thermal Resistance of Conduction Cooled Power Transistors, dated October 1975 as Appendix A. (See Appendix I of this report).

the added advantage of not having to mount the device under test on a heat sink [5].

To compare relative quality of the die bond, it is assumed that the temperature coefficient of the TSP is the same for all members of a given group of devices of the same design and construction (see section 4.4.1). It is therefore necessary only to measure the TSP first under conditions of no internal power dissipation  $(\mathbf{V}_{\text{MC}})$  and then at some specified time after the termination of the constant heating power pulse  $(\mathbf{V}_{\text{M2}})$ . A quantity proportional to the junction-to-reference point temperature difference is obtained by subtracting  $\mathbf{V}_{\text{M2}}$  from  $\mathbf{V}_{\text{MC}}$ . This allows the transient thermal response technique to be made less time-consuming for use as a manufacturing screen or process control measurement for die attachment evaluation.

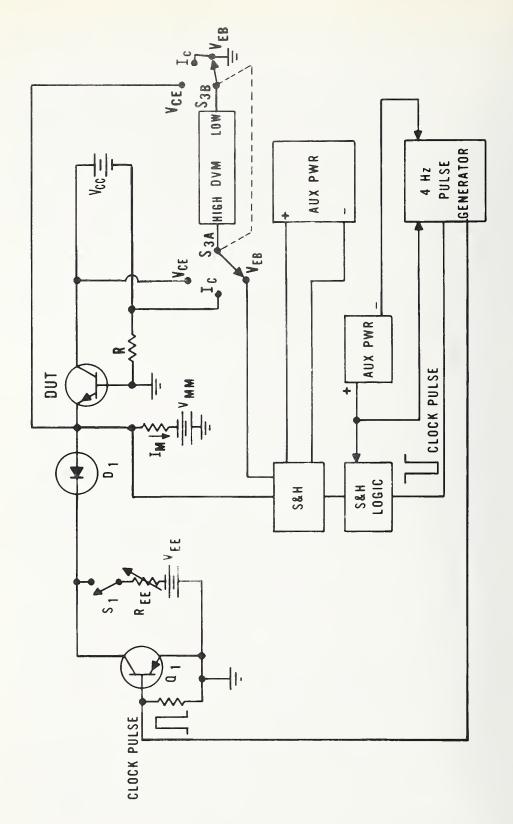

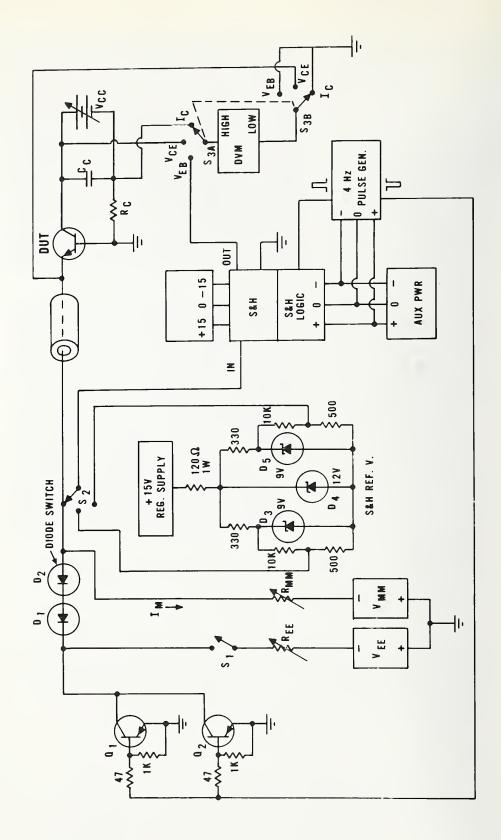

A typical circuit for measuring  $V_{MC}$  and  $V_{M2}$  is shown in figure 6. It should be noted that the power interruption circuitry is similar to that used in the measurement of thermal resistance utilizing the emitter-only switching procedure, although for transient thermal response measurements, the power-off interval is long compared to the power-on interval.

The circuit is controlled by a clock pulse with adjustable width and repetition rate. When the voltage level of the clock pulse is zero, transistor  $\mathbf{Q}_1$  is off, and the current through the DUT is the sum of the heating current (switch  $\mathbf{S}_1$  closed) and  $\mathbf{I}_{\mathbf{M}}$ . The heating power pulse ends when the clock goes negative. This turns  $\mathbf{Q}_1$  on, causing the heating current from  $\mathbf{V}_{\mathrm{EE}}$  to now flow through  $\mathbf{Q}_1$  instead of the DUT. After a delay to allow electrical transients to subside (usually 10 to 50  $\mu \mathrm{s}$ ), the sample-and-hold unit (S&H) senses  $\mathbf{V}_{\mathrm{M2}}$  and displays its value on the digital voltmeter (DVM) (switch  $\mathbf{S}_3$  as indicated). The voltage  $\mathbf{V}_{\mathrm{MC}}$  is obtained by making the measurement, with the heating current supply disconnected (switch  $\mathbf{S}_1$  open) or with transistor  $\mathbf{Q}_1$  turned on, prior to the application of the heating power pulse.

### 6. Conclusions

A brief description of the idealized concept of thermal resistance has been given along with the problems and pitfalls encountered in applying the concept to power transistors. It was shown that for high-current low-voltage operating conditions, a unique and meaningful thermal resistance based on the peak junction temperature can usually be defined, but for low-current, high-voltage conditions, no unique value, independent of operating conditions, can be defined.

In addition, the advantages and disadvantages of various electrical techniques for measuring thermal resistance were described, and a preferred standard technique was discussed in detail. This preferred technique, in which the forward-biased emitter-base junction is used as the temperature-sensitive parameter, is usable on all types of bipolar transistors. The measurement procedure is relatively simple and, because the temperature-sensitive parameter is sensed under conditions that simulate normal device operation, it is relatively accurate. The power interrup-

Figure 6. Block diagram for thermal response measuring system for npn transistors.

tion circuitry is also relatively fast and simple since only the emitter terminal of the device under test is switched. Detailed circuit diagrams and mounting and cooling arrangements to enable the building of a completed test system for measuring the thermal resistance of power transistors using the  $V_{EB}$  emitter-only switching technique are also presented. Simplifications in the temperature-sensitive parameter calibration and extrapolation procedures to make the technique usable in a production environment are valid under a variety of device operating conditions as long as the device design and construction is not changed. The basic approach and test circuitry is also usable for semiconductor device die attachment evaluation.

## 7. References

- Thermal Resistance Measurements of Conduction Cooled Power Transistors, EIA Recommended Standard RS-313-B (Revision of RS-313-A), October 1975. (Available from Electronics Industries Association, 2001 Eye Street, N.W., Washington, DC 20006.) (This reference can be found in Appendix I of this report.)

- 2. Blackburn, D. L., An Electrical Technique for the Measurement of the Peak Junction Temperature of Power Transistors, 13th Annual Proceedings, Reliability Physics 1975, Las Vegas, Nevada, April 1-3, 1975, pp. 142-150.

- 3. Blackburn, D. L., and Oettinger, F. F., Transient Thermal Response Measurements of Power Transistors, *PESC '74 Record*, IEEE Power Electronics Specialists Conference, Murray Hill, New Jersey, June 10-12, 1974, pp. 140-148.

- 4. Rubin, S., Thermal Resistance Measurements on Monolithic and Hybrid Darlington Power Transistors, *PESC '75 Record*, IEEE Power Electronics Specialists Conference, Culver City, California, June 9-11, 1975, pp. 252-261.

- 5. Oettinger, F. F., and Gladhill, R. L., Thermal Response Measurements for Semiconductor Device Die Attachment Evaluation, 1973 IEDM Technical Digest, Washington, D. C., December 3-4, 1973, pp. 47-50.

- 6. Reich, B., Continuous Thermal Resistance Measurements, Semiconductor Products 5, No. 11, 24-27 (1962).

- 7. Reich, B., and Hakim, E. B., An Appraisal of Transistor Thermal Resistance, SCP and Solid State Technology 8, No. 4, 21-29 (1965).

- 8. Early, J. M., Effect of Space Charge Layer Widening in Junction Transistors, *Proc. IRE* 40, 1401-1406 (1952).

- 9. Sparkes, J. J., Voltage Feedback and Thermal Resistance in Junction Transistors, *Proc. IRE* 46, 1305-1306 (1958).

- 10. Oettinger, F. F., and Rubin, S., The Use of Current Gain as an Indicator for the Formation of Hot Spots Due to Current Crowding in Power Transistors, 10th Annual Proceedings, Reliability Physics 1972, Las Vegas, Nevada, April 5-7, 1972, pp. 12-18.

- 11. Tellerman, J., Measuring Transistor Temperature Rise, *Electronics* 27, No. 4, 185-187 (1954).

- 12. Nelson, J. F., and Iwersen, J. E., Measurement of Internal Temperature Rise of Transistors, *Proc. IRE* 46, 1207-1208 (1958).

- 13. Gates, R. F., and Johnson, R. A., The Measurement of Thermal Resistance A Recommendation for Standardization, Semiconductor Products 2, No. 7, 21-26 (1959).

- 14. Coleby, P., Thermal Resistance of Semiconductor Devices under Steady-State Conditions, Mullard Technical Communications 7, No. 65, 127-140 (1963).

- 15. Vollheim, E. L., How to Measure Thermal Resistance of Transistors, *EEE* 11, No. 12, 71-73 (1963).

- 16. Grutchfield, H. B., Measurement of the Thermal Resistance and Thermal Response of Diffused Silicon Transistors, Fairchild Semiconductor Application Bulletin, APP-53 (January 1963).

- 17. Verway, J. F., On the Mechanism of  $h_{FE}$  Degradation by Emitter-Base Reverse Current Stress, *Microelectronics and Reliability*  $\underline{9}$ , 425-432 (1972).

- 18. Gaur, S. P., Navon, D. H., and Teerlinck, R. W., Transistor Design and Thermal Stability, *IEEE Trans. Electron Devices* ED-20, 527-534 (1973).

- 19. Brenner, D. J., A Technique for Measuring the Surface Temperature of Transistors by Means of Fluorescent Phosphors, NBS Tech. Note 591 (July 1971).

- 20. Hower, P. L., and Govil, P. K., Comparison of One- and Two-Dimensional Models of Transistor Thermal Instability, *IEEE Trans. Electron Devices* <u>ED-21</u>, pp. 617-623 (1974).

- 21. Olmstead, J., Einthoven, W., Ponczak, S., and Kannam, P. J., High Level Current Gain in Bipolar Power Transistors, RCA Rev. 32, 221-249 (1971).

# THERMAL RESISTANCE MEASUREMENTS OF CONDUCTION COOLED POWER TRANSISTORS

Reprinted with Permission of the Electronic Industries Association

**ELECTRONIC INDUSTRIES ASSOCIATION**

RS-313-B Revision of RS-313-A

Formulated by

JEDEC SOLID STATE PRODUCTS COUNCIL

### NOTICE

EIA engineering standards are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for his particular need. Existence of such standards shall not in any respect preclude any member or non-member of EIA from manufacturing or selling products not conforming to such standards, nor shall the existence of such standards preclude their voluntary use by those other than EIA members whether the standard is to be used either domestically or internationally.

Recommended standards are adopted by EIA without regard to whether or not their adoption may involve patents on articles, materials, or processes. By such action, EIA does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the recommended standards.

Published by

# **ELECTRONIC INDUSTRIES ASSOCIATION**

Engineering Department

2001 Eye Street, N.W., Washington, D. C. 20006

© Electronic Industries Association 1975

All rights reserved

Printed in U.S.A.

# **FOREWORD**

This standard describes a recommended test method for measuring the thermal resistance of conduction-cooled power transistors. This method is offered as a replacement for that contained in EIA/NEMA Standard RS-313-A (March 1968) which has been found deficient in its test method detail. The present method is the emitter-base forward voltage method with emitter-base switching and treats the detail circuitry, test instruments, calibration and precautions to assure reliable and reproducible measurement. It generally conforms to the principle of MIL-STD-750 Method 3131 and to IEC Publication 147-C2 Method 12.3.1. However, experience has shown that the test performed under this Standard is applicable to all power transistors regardless of thermal response times.

This material was prepared by JEDEC Committee JC-25 on Power Transistors and approved for publication by the JEDEC Solid State Products Council.

(From Standards Proposal No. 1179, formulated under the cognizance of the JC-25 JEDEC Committee on Power Transistors.)

# 1. THERMAL RESISTANCE, JUNCTION to SPECIFIED REFERENCE POINT (R $_{ heta\,\mathrm{IR}}$ ).

1.1 General Considerations. Of the thermal characteristics of a semiconductor device, the most frequently specified parameter is the thermal resistance between the chip and a reference point such as the device case or ambient.

The thermal resistance of a semiconductor device is a measure of the ability of its mechanical structure (package) to provide for heat removal from the semiconductor junction. In most devices, the maximum junction temperature can't be measured directly since the area of interest is not accessible due to packaging considerations. Thus, indirect means are used to infer the temperature of a specific area on the chip. The thermal resistance of a semiconductor device is therefore determined by the measurement of a temperature-sensitive electrical parameter of a semiconductor junction within the device.

The measured thermal resistance of semiconductor elements (transistors) is not constant as frequently assumed, but depends on the device operating conditions, the junction and reference point temperatures, and the temperature-sensitive parameter chosen. When specifying thermal resistance, it is therefore important to indicate clearly the measuring conditions. The temperature sensitive device parameter is used as an indicator of an average (weighted) junction temperature of the semiconductor element for calculations of thermal resistance.

In measuring power transistor thermal resistance, either the emitter-base forward voltage or the collector-base forward voltage can be used as the temperature sensitive electrical parameter to indicate the junction temperature. Although equally precise, the Emitter-Base Voltage Technique has been found to be more accurate than the Collector-Base Voltage Technique, i.e., the Emitter-Base Voltage Technique gives a junction temperature closer to the actual peak temperature on the chip. The greater inaccuracy of the Collector-Base Voltage Technique is due to the greater deviation between the region of the collector junction traversed by the measuring current during calibration and the region traversed during test.

- 1.2 The Measurement of Thermal Resistance, Junction to Specified Reference Point ( $R_{\theta JR}$ ), using the emitter-base voltage of a transistor in the emitter-only switching mode as the temperature sensitive parameter.

- 1.2.1 Purpose. The purpose of the test is to measure the junction to specified reference point thermal resistance of single element transistors by using the emitter-base junction to indicate the device junction temperature. This method is to be used as the standard

technique, i.e., referce method for the measurement of thermal resistance. However, the procedure is also adaptable to production testing, including die attachment screening (see Appendix A).

1.2.2 Procedure. In measuring transistor thermal resistance, the emitter-base forward voltage of the transistor is used as the temperature sensitive parameter (TSP) to indicate the junction temperature. The TSP is measured at a small fixed forward current. This low level current, at which the temperature sensitive parameter is measured, is called the measuring or calibration current ( $I_{\rm M}$ ). The magnitude of  $I_{\rm M}$  is such that the TSP varies linearly with temperature and is stable. The TSP is measured under two general operating conditions. First, the measurements of the emitter-base forward voltage necessary to determine the changes in the TSP due to the dissipation of power are made. For these measurements the case temperature is kept at a constant preset value. After this is complete, the calibration curve is generated by measuring the TSP as a function of the case temperature starting at the lowest case temperature of interest. The information generated under these operating conditions is then used to calculate the junction-to-reference point thermal resistance in the following manner:

$$R_{\theta JR} = \frac{T_J - T_R}{P(AVG)} = \frac{V_{M2} - V_{M1}}{(P_2 - P_1)D} \times \left[\frac{\Delta V_{MC}}{\Delta T_{MC}}\right] \frac{-1}{Calibration}$$

where:

R<sub>\theta JR</sub> = Thermal Resistance, junction to reference point, in degrees Celsius/watt.

T<sub>I</sub> = Junction temperature in degrees Celsius.

T<sub>R</sub> = Reference point temperature in degrees Celsius.

P(AVG) = Average heating power applied to transistor causing temperature difference  $T_J - T_R$  in watts.

P<sub>2</sub> = Magnitude of higher heating power applied to transistor in watts.

P<sub>1</sub> = Magnitude of lower heating power applied to transistor in watts.

$V_{M2}$  = Value of TSP corresponding to the temperature of the junction heated by  $P_2$  and measured at  $I_M$  in millivolts.

V<sub>M1</sub> = Value of TSP corresponding to the temperature of the junction heated by P<sub>1</sub> and measured at I<sub>M</sub> in millivolts.

D = Heating power duty factor.

$(\triangle V_{MC}/\triangle T_{MC}) = \text{Temperature sensitive parameter temperature eoefficient measured at } I_{M}$  in millivolts/degree Celsius.

T<sub>MC</sub> = Calibration temperature measured at reference point in degrees Celsius.

$V_{MC}$  = Value of TSP during ealibration at  $I_{M}$  and specific value of  $T_{MC}$  in millivolts.

If the lower heating power ( $P_1$ ) applied to the transistor is equal to the power dissipation during calibration then  $V_{M1} = V_{MC}$  (for  $T_{MC} = T_R$ ). Also, if the power dissipation during ealibration is negligible, then  $P_1 \approx 0$ .  $R_{\theta \, IR}$  can then be simplified to:

$$R_{\theta JR} = \frac{V_{M2} - V_{MC} \text{ (for } T_{MC} = T_R)}{P_2 D} \times \left[\frac{\Delta V_{MC}}{\Delta T_{MC}}\right] - 1$$

Calibration

Measurements of  $T_R$  and  $T_{MC}$  are made by means of a thermocouple attached to the reference point. See Appendix B for information on reference point temperature measurements of conduction cooled power transistors. The power dissipation in the device under test is calculated as follows:

$$P = I_C V_{CB} + I_E V_{BE}.$$

The measurement of thermal resistance is generally divided into two steps:

Step I - Power Application Test.